2020屆IC企業校招部分筆試題

1 AMD

1.1 if A=4’b0011,B=3’b110 and C=4’b1110,then which one is the correct result for expression of {2{~^A}}^(B[1:0]&C[3:2]) ?

A. 00

B. 01

C. 10

D. 11

~^A = ~(0&0&1&1) = ~0 = 1;

{2{~^A}} = {2{1}} = 2’b11;

(B[1:0]&C[3:2]) = 2’b10 & 2’b11 = 2’b10;

{2{~^A}}^(B[1:0]&C[3:2]) = 2’b11 ^ 2’b10 = 2’b01.

1.2 Which statement is correct?

A. UVM test termination is using raise/drop uvm_object.

B. When we set the verbosity to UVM_LOW,the message with UVM_NONE cannot be issued.

C. If we set the configuration object in test layer,both subcomponents and sequences can retrieve its handle.

D. In SV language,It fails to cast a null pointer to an object. 「$(abc,null);」

1.3 …全特麼是驗證的

1.7 Please select the 4-state unsigned integer types()

A. bit.

B. logic.

C. reg.

D. shortint.

1.8 Choose the right descriptions of the different between latch and flip-flop listed below()

A. Flip-Flop saves area.

B. Latch can’t avoid glitch.

C. Flip-Flop is easier for timing closure.

D. Latch run slower than Flip-Flop.

Latch可以組成Flip-Flop;

Latch也可以避免毛刺,比如門控時鐘。

1.9 Which of the following items can help reduce test time()

A. Increase Operation Voltage.

B. Increase scan shift clock frequency.

C. Utilize more scan IOs.

D. Insert gating logic.

1.11 Coverage is usually used to evaluate the verification quality, please identify all code coverage related items from following options.

A. Branch coverage.

B. Condition coverage.

C. Function coverage.

D. Toggle coverage.

E. State coverage.

F. Expression coverage.

G. FSM coverage.

1.12 Which type of timing path is NOT included in this picture?

A. Input port to a D pin of Flop.

B. CLK pin of One Flop to D pin next Flop.

C. Q pin of flop to an output port.

D. Input to output port through purely combinational logic.

典型的組合邏輯路徑只有以下四種:

1.13 Which is the correct flow for Physical Design ?

A. Floorplan → Placement → CTS → Routing

B. CTS → Floorplan → Placement → Routing

C. Placement → Floorplan → CTS → Routing

D. CTS → Placement → Floorplan → Routing

The main steps in ASIC Physical design flow are:

- Design Netlist (after Synthesis);

- Floorplanning;

- Partitioning;

- Placement;

- Clock-Tree Synthesis (CTS);

- Routing;

- Physical Verification;

- GDS Ⅱ Generation。

1.14 「PVT corner」 is a significant concept in physical design to characterize different working conditions of a chip -P stands for Process and V stands for voltage. What does T stand for ?

A. Time.

B. Temperature.

C. Thickness.

D. Threshold.

1.15 Which of the following metal layer has Maximum resistance?

A. Metal2.

B. Metal3.

C. Metal5.

D. Metal8.

1.16 which of the following files are necessary for timing analysis?

A. SPEF.

B. DEF.

C. SDC.

D. Netlist.

STA tool:

- Netlist;

- Library;

- SDC;

- Parasitic.

1.17 Which among the following methods are applicable to fix setup violation?

A. Swap high Vt cells into low Vt cells.

B. Increase driver size of long net.

C. Delaying the clock to the end point.

D. Decreasing the size of certain cells in the data path.

降低cell電壓;

增加驅動;

延時時鐘;

減小cell面積。

1.18 Which of the following timing arcs should a normal DFF have in stand cell library?

A. CK → D.

B. CK → Q.

C. D → Q.

D. CK → CDN.

1.19 Cell Delay can be calculated based on:()

A. input transition.

B. input load.

C. output transition.

D. output load.

input transition:輸入數據的變換時間;

output transition: 上一級數據的變換時間;

input load:輸入負載,負載越大input transition越小;

output load:輸出負載。

1.20 太簡單

1.21 7nm工藝中的7nm指的是()

A. 晶片中最小電晶體的源極長度.

B. 晶片中最小電晶體的源極寬度.

C. 晶片中最小單元的溝道長度.

D. 晶片中最小單元的源極寬度.

1.22 What is the layer that TCP worked on?

A. Network.

B. Data Link.

C. Transport.

D. Application. E. Session.

OSI七層模型:

- 應用層;

- 表示層;

- 對談層;

- 傳輸層;

- 網路層;

- 數據鏈路層;

- 物理層。

TCP屬於傳輸層;IP屬於網路層;HTTP屬於應用層,基於TCP連線。

1.23 有一個4位元的D/A轉換器,設他的滿刻度輸出電壓位10V,當輸入數位量爲1101時,輸出電壓爲()

A. 8.125V.

B. 4V.

C. 6.25V.

D. 9.375V.

1.24 Which of below pattern can detect the fault in below diagram?

A. A=1,B=1,C=0,D=0.

B. A=1,B=1,C=1,D=1.

C. A=0,B=0,C=1,D=1.

D. A=0,B=1,C=0,D=1.

1.25 In ARM AMBA AHB protocol,which of following responses is ONE cycle response?

A. OKAY.

B. ERROR.

C. RETRY.

D. SPLIT.

1.26 Assume A[3:0]=4’b0101,B[3:0]=4’b1111,which statement is correct()?

A. if C=&(A|B),then C=1’b0.

B. if C=(|A)&(|B),then C=1’b1.

C. if C=|(A&B),then C=1’b0.

D. if C=(&A)|(&B),then C=1’b0.

1.27 For a truth table like below,which kind of logic cell could it be?

| input A | input B | output Z |

|---|---|---|

| 1 | 1 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 1 |

A. OR.

B. NAND.

C. XOR.

D. NOR.

1.28 Choose the correct equation for power calculation()

A. Ptotal=Pstatic+Pdynamic.

B. Ptotal=Pleakage+Pinternal+Pswitching.

C. Ptotal=Pinternal+Pdynamic.

D. Ptotal=Pleakage+Pswitching.

1.29 We need to define clock specifications in SDC file,using commands like below:create_clock -name GFXCLK -period 600 -waveform {0 300}.What can we know from this command?

A. Clock frequency.

B. Clock duty cycle.

C. Clock source latency.

D. Clock name.

1.30 Which is the correct method to fix EM issue?

A. downsize victim driver.

B. double net width,double net spacing,chanfe route layer.

C. insert buffer in victim net.

D. add shield.

1.31 高頻放大器工作頻率越高,以下說法正確的是()

A. 增益和頻寬都大.

B. 增益和頻寬都小.

C. 增益變大,頻寬變小.

D. 增益變小,頻寬變大.

1.32 PCIE

1.33 Ubuntu的內核有哪幾個子系統()

A. 進程管理系統.

B. 使用者管理系統.

C. I/O管理系統.

D. 檔案管理系統.

E. 記憶體管理系統.

F. 安全管理系統.

2 大疆

2.1 下列關於多bit數據跨時鐘域的處理思路,錯誤的有()

A. 發送方給出數據,接收方用本地時鐘同步兩拍再使用.

B. 發送方把數據寫到非同步fifo,接收方從非同步fifo裡讀出.

C. 對於連續變化的信號,發送方轉爲格雷碼發送,接收方收到後再轉爲二進制.

D. 發送方給出數據,發送方給出握手請求,接收方收到後回覆 回復.

兩級信號同步是處理單位元信號,而多位元數據可以用非同步FIFO、格雷碼、握手協定。

2.2 對12.918做無失真定點化,需要的最小位寬是多少位,位寬選擇11位時的量化誤差是多少?

A. 12位元,0.0118.

B. 13位,0.0039.

C. 12位元,0.0039.

D. 13位,0.0118.

12用二進制表示需要4位元,若小數用8位元表示0.918/(2^(-8))=235.008,即235×2^(-8)=0.918,所以最少只要12位元。當11位時,小數的位寬只有7,0.918/(2^(-7))=117.5040,117×2^(-7)=0.9141,0.918-0.9141=0.0039。

2.3 考慮如下的4×4的「二維仲裁器」,R00到R33爲輸入,G00到G33爲輸出,N和W也爲輸入,E和S也爲輸出,假設所有的邏輯閘(包括非門/與門/反相器)延時都爲1ns,請問該電路的最大延遲爲:

A. 23ns.

B. 25ns.

C. 19ns.

D. 21ns.

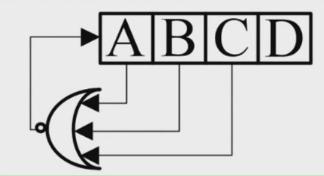

2.4 下圖所示4位元右移位暫存器,0時刻ABCD初始狀態爲0111,請寫出5個時刻後的ABCD輸出:

A. 1010.

B. 0100.

C. 1101.

D. 1110.

Time A B C D NAND 0 0 1 1 1 0 1 0 0 1 1 0 2 0 0 0 1 1 3 1 0 0 0 0 4 0 0 0 0 0 5 0 1 1 0 0

2.5 關於流水線設計的理解,錯誤的是:

A. 流水線設計會消耗較多的組合邏輯資源.

B. 流水線設計會導致原有通路延時增加.

C. 流水線設計的思想,是使用面積換取速度.

D. 關鍵路徑中插入流水線,能夠提高系統時鐘頻率.

2.6 下列哪種邏輯閘可以實現邏輯(A XOR B)OR (C AND D)?

A. NAND.

B. NOR.

C. XOR.

D. INV.

(A XOR B)OR (C AND D) = AB’ + A’B + CD

= ((AB’)’(A’B)’(CD)’)’

= ((A(BB)’)’((AA)’B)’(CD)’)’

2.7 關於DFT的描述錯誤的是:

A. DFT測試不能覆蓋電路時序問題.

B. DFT測試過程通常會消耗大量的動態功耗.

C. DFT的主要目的是發現晶片生產過程中出現的缺陷.

D. 暫存器掃描鏈是一種常用的DFT技術.

DFT的at-speed test會採用晶片PLL高速時鐘進行暫存器的setup和hold測試

2.8 下列那個工具不具備邏輯綜合功能

A. Synplify.

B. Design Compiler.

C. Modelsim.

D. ISE.

2.9 對晶片靜態功耗影響最大的是哪一項

A. 工作模式.

B. 頻率.

C. 負載.

D. 電壓.

Pstat = Istat × Vdd

2.10 組合邏輯中的冒險是由於()引起的

A. 電路中有多個輸出.

B. 電路未達到最簡.

C. 邏輯閘型別不同.

D. 電路中的延時.

由於延時導致電平翻轉不能同時進行

2.11 指令系統中程式控制類指令的功能是

A. 實現主記憶體於CPU之間的數據傳送.

B. 實現程式執行順序的改變.

C. 實現算術和邏輯運算.

D. 時間堆疊操作.

程式控制類指令包括:

- 跳轉指令;

- 回圈指令;

- 子程式指令;

- 中斷指令。 這些指令可以控製程式的執行順序。

2.12 在對信號做降採樣前新增濾波器,一般需要新增什麼樣的濾波器,完成什麼功能?

A. 高通,抗週期延拓.

B. 高通,抗混疊濾波.

C. 低通,抗週期延拓.

D. 低通,抗混疊濾波.

爲解決頻率混疊,在對模擬信號進行離散化採集前,採用低通濾波濾除 高於1/2採樣頻率的頻率成分。實際儀器設計中,這個低通濾波器的截止頻率(fc)爲:截止頻率(fc)=採樣頻率(fz)/2.56,在進行動態信號測試中測量儀器必須具有抗混疊濾波功能。

2.13 假設一個cycle只能完成一個8bits×8bits或一個17bits+17bits+17bits操作,那麼設計16bits×16bits乘法最少可以多少個cycle完成?

A. 2.

B. 4.

C. 3.

D. 1.

兩個16位元相乘(A×B),等於同時有兩個「兩個8位元相乘」,消耗一個cycle;

A的低八位乘B的低八位產生一個16位元的數,類似的,一共產生4個16位元的數,這四個16位元的數交錯相加;

最低八位不變,最高八位不變,次高位三個八位數相加,次低位三個八位數相加,又消耗兩個cycle。

2.14 如下關於「線與」邏輯的描述,錯誤的是:

A. 可以使用OC門來實現「線與」.

B. 「線與」邏輯必須在輸出端加一個下拉電阻.

C. 「線與」邏輯是兩個輸出信號相連可以實現「與」的功能.

D. 可以用OD門來實現「線與」.

OD:開漏,是對MOS管而言;

OC:集電極開路,是對雙極性管而言。

兩者實現線與需外加上拉電阻。

2.15 關於非同步處理,以下說法正確的是:

A. 靜態設定信號可以不做非同步處理.

B. 非同步FIFO採用格雷碼的原因是爲了提高電路速度.

C. 非同步處理需要考慮發送和接收時鐘之間的頻率關係.

D. 單位元信號打兩拍之後可以避免亞穩態的發生.

2.16 關於16點的FFT描述正確的是:

A. 每個蝶形演算法需要一次複數加法.

B. 每級有8個蝶形演算法.

C. 每個蝶形演算法需要一次複數乘法.

D. 共有4級分解.

完成一個蝶形運算需要一次複數乘法和兩次複數加法。

2.17 在不增加pipeline的情況下,如何解決一條critical path的setup時序不滿足的問題

A. 使用更先進工藝的工藝庫.

B. 在這條path上插入暫存器.

C. 將部分組合邏輯電路搬移到前級path上.

D. 降低時鐘頻率.

2.18 下列關於程式碼覆蓋率描述錯誤的是:

A. 程式碼覆蓋率達到百分之一百說明程式碼bug已消除.

B. 程式碼覆蓋率包括功能覆蓋率.

C. 程式碼覆蓋率包括條件覆蓋率.

D. 程式碼覆蓋率包括語句覆蓋率.

覆蓋率是衡量設計驗證完成程度的指標,並不是驗證的目的。任何覆蓋率達到100%並不代表晶片bug已消除。 程式碼覆蓋率包括:

- 行覆蓋率;

- 條件覆蓋率;

- 狀態機覆蓋率;

- 翻轉覆蓋率。 功能覆蓋率反映開發出來的需要覆蓋的功能點覆蓋的比例。 斷言覆蓋率測量斷言被觸發的頻繁程度。

2.19 C語言中定義了一個全域性陣列,編譯後此陣列可能分配在下列哪個階段?

A. Text段.

B. Bss段.

C. Data段.

D. Stack段.

BSS存放的是未初始化的全域性變數;

DATA存放的是初始化的全域性變數。

2.20 下列優化方法中那些是速度優化方法:

A. 資源共用.

B. 關鍵路徑優化.

C. 流水線.

D. 序列化.

2.21 對於PSK和QAM調製,以下哪些說法是正確的?

A. 對於QAM調製,星座圖的每個點的幅度相等.

B. 2PSK和4PSK在歸一化條件下,其幅值都是1.

C. 4-QAM調製與QSPK的調製方式一致.

D. 在同樣通道條件下,16-QAM的誤位元速率大於4-QAM.

PSK調製,星座圖中的點都位於單位圓上,模相同(都爲1),只有相位不同。而QAM調製星座圖中的點不再位於單位圓上,而是分佈在複平面的一定範圍內,各點如果模相同,則相位必不相同,如果相位相同則模必不相同。

2.22 wirte-back cache和write-through cache的區別:(write-back)cache只在cache line被替代的時候把cache裡的有效數據寫下一級儲存。

write-through(直寫模式)在數據更新時,同時寫入快取cache和後端儲存。此模式的優點是操作簡單,缺點是因爲數據修改需要同時寫入儲存,數據寫入速度較慢。

write-back(回寫模式)在數據更新時寫入快取cache只在數據被替換出快取時,被修改的快取數據纔會被寫到後端儲存。此模式的優點是數據寫入速度快,因爲不需要寫儲存;缺點是已更新後的數據未被寫入儲存時出現系統掉電的情況,數據將無法找回。

2.23 正則表達式裡可以使用計數符和通用字元集進行搜尋匹配,這些計數符中,(*)號的意思是匹配0個,1個或多個,(+)號的意思是匹配一個或多個,(?)的意思是匹配0個或1個。

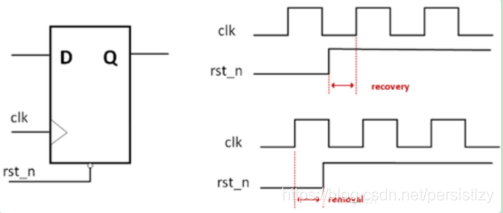

2.24 FPGA時序檢查中對於非同步復位電路的時序分析分別叫(恢復時間檢查)和(移除時間檢查)。

recovery time:恢復時間。

復原復位時,恢復到解復位狀態的電平必須在時鐘有效沿來臨之前的一段時間到來,才能 纔能保證時鐘能有效恢復到解復位狀態,此段時間爲recovery time。類似於同步時鐘的setup time。

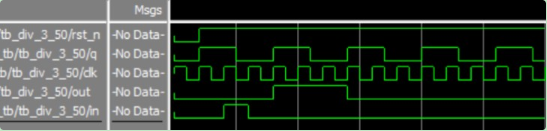

如下圖,rst_n爲1’b0表示覆位,clk上升沿觸發,rst_n從1’b0到1’b1的上升沿與時鐘上升沿必須不小於recovery time才能 纔能保證暫存器恢復到正常狀態。

removal time:移除時間。

復位時,在時鐘有效沿來臨之後復位信號還需要保持的時間爲移除時間removal time。類似同步時鐘hold time。 如下圖,rst_n爲1’b0表示覆位有效,clk爲上升沿觸發,rst_n保持爲1’b0經過clk上升沿後仍需保持一段時間,才能 纔能保證暫存器有效復位,放置亞穩態。

2.25 並行計算是提高程式速度的關鍵,設a爲並行計算部分所佔比例,n爲並行處理的節點數,則並行計算帶來的加速比爲(1 /(a/n + 1 - a))。

S = (Ws + Wp)/(Ws + Wp/p),Ws爲程式中序列部分,Wp爲程式中的並行部分,p爲並行節點數。

2.26 下圖球框由三個相同的鐵圈兩兩正相交組成,每個鐵圈的電阻均爲R。AB兩點間的電阻爲(5R/48)。

2.27 signal_a是clk_a(300M)時鐘域的一個單時鐘脈衝信號,如何將其同步到時鐘域clk_b(100M)中,併產生出signal_b同步脈衝信號。請用verilog程式碼描述,並畫出對應的時序波形說明圖。

module div_3_50( input clk, input rst_n, input in, output q, output out, ); reg q1,q2; reg [1:0] count1,count2; reg in_p,in_pp,in_ppp; wire out_b; reg out_bb,out_bbb; assign q=q1|q2; always_ff@(posedge clk , negedge rst_n)begin if(!rst_n) begin q1 <= '0; count1 < ='0; end else if(count1==0) begin q1 <= ~q1; count1 <= count1 + 1; end else if(count1==1) begin q1 = ~q1; count1 <= count1 + 1; end else begin count1 <= '0; end end always_ff@(negedge clk , negedge rst_n)begin if(!rst_n) begin q2 <= '0; count2 < ='0; end else if(count2==0) begin q2 <= ~q2; count2 <= count2 + 1; end else if(count2==1) begin q2 = ~q2; count2 <= count2 + 1; end else begin count2 <= '0; end end always_ff@(posedge clk , negedge rst_n)begin if(!rst_n) begin in_p <= '0; in_pp <= '0; in_ppp <= '0; end else begin in_p <= in; in_pp <= in_p; in_ppp <= in_pp; end end assign out_b = in_ppp|in_pp|in_p; always_ff@(posege clk , negedge rst_n)begin if(!rst_n) begin out_bb <= '0; out_bbb <= '0; end else begin out_bb <= out_b; out_bbb <= out_bb; end end assign out = out_bbb; endmoduleselect this verilog

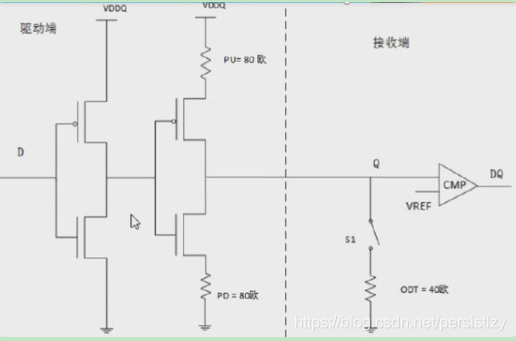

2.28 如下圖,一個高速介面的埠電路示意圖,要求D端發送數位0/1。D/Q端收到相同的數位0/1。VREF電壓爲比較器數位輸出0/1的判決電壓。

(1)S1斷開時,DQ端VREF電壓需設定爲?

(2)S1連通時,DQ端VREF電壓需設定爲?

(3)驅動端發送0時功耗比較低,這句話正確嗎?爲什麼?

(1)S1斷開時,若D爲1,Q端電壓爲VDDQ,因此VREF要小於VDDQ。若D爲0,Q端電壓爲0,因此VREF要大於0,因此0<VREF<VDDQ。

(2)S1連通時,若D爲1,Q端電壓爲VDDQ/3。若D爲0,Q端電壓爲0,因此VREF要大於0,因此0<VREF<VDDQ/3。

(3)驅動端爲0時,NMOS管道通,反相器輸出接地,電阻沒有電流,因此功耗較低。

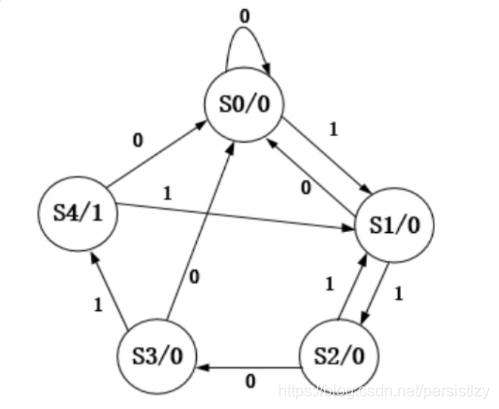

2.29 用Moore型狀態機實現序列「1101」從右至左的不重疊檢測。

(1)請畫出狀態轉換圖,其中狀態用S0,S1,S2…表示。

(2)針對這個具體設計如何衡量驗證的完備性?

(1):

(2):可以從定向測試,隨機測試兩種方式中產生激勵,從程式碼覆蓋率的角度保證程式碼覆蓋率達100%。

2.30 進行一個運算單元的電路設計,A[7:0]*11111011,儘量用最少的資源實現,寫出對應的RTL程式碼。

module mul( input [7:0] A, output [15:0] B ); wire [15:0] reg1; wire [15:0] reg2; wire [15:0] reg3; assign reg1 = { A, {8{1'b0}}}; assign reg2 = { {6{1'b0}} , A ,{2{1'b0}}}; assign reg3 = { {8{1'b0}} , A}; assign B = reg1 - reg2 - reg3; endmoduleselect this verilog

2.31 用C語言實現整數到ASCII碼字串的轉換

額。。。。我尼瑪

3 聯芸科技

3.1 請解釋D觸發器和Latch的區別,解釋同步復位和非同步復位的區別及優缺點。

一、

- Latch有電平觸發,非同步控制。在使能信號有效時Latch相當於通路,在使能信號無效時Latch保持輸出狀態。D觸發器由時鐘沿觸發,同步控制。

- Latch容易產生毛刺,D觸發器則不易產生毛刺。

- 如果使用閘電路來搭建Latch和D觸發器,則Latch消耗的門資源比D觸發器要少,這是Latch比D觸發器優越的地方。所以在ASIC中使用Latch的整合度比D觸發器高,但在FPGA中恰好相反,因爲FPGA中沒有標準的Latch單元,但有D觸發器單元,一個Latch需要多個LE才能 纔能實現。

二、- 同步復位:同步復位只有在時鐘沿到來時復位信號才起作用,則復位信號持續時間應該超過一個時鐘週期才能 纔能保證系統復位。

- 非同步復位:非同步復位只要有復位信號系統馬上就復位,因此非同步復位抗幹擾能力差,有些噪聲也是能系統復位,因此有時候顯得不夠穩定,要想設計一個好的復位最好使用非同步復位同步釋放。

- 同步復位:

- 優點:

- 有利於模擬器模擬;

- 可以使用所設計的系統成爲100%同步時序電路,這大大有利於時序分析,而且綜合出來的fmax一般較高。

- 因爲他只有在時鐘有效電平到來時纔有效,所以可以濾掉高於時鐘頻率的毛刺。

- 缺點:

- 復位信號的有效時長必須大於時鐘週期,才能 纔能真正被系統識別並完成復位任務。同時還要考慮,諸如:clk skew,組合邏輯路徑延>時,復位延時等因素;

- 由於大多數的邏輯裝置的目標庫內的DFF都只有非同步復位埠,所以,倘若採用同步復位的話,綜合器就會在暫存器的暫存器的數據輸入埠插入組合邏輯,這樣就會耗費較多的邏輯資源。

- 非同步復位:

- 優點:

- 大多數目標器件庫的DFF都有非同步復位埠,因此採用非同步復位可以節省資源;

- 設計相對簡單;

- 非同步復位信號識別方便,而且可以很方便的使用FPGA的全域性復位埠GSR。

- 缺點:

- 在復位信號釋放(release)的時候很容易出現問題,倘若復位釋放時恰好在時鐘有效沿附近,就很容易使暫存器輸出出現亞穩態,從而導致亞穩態。

- 復位信號容易收到毛刺影響。

3.2 解釋什麼叫clock gating?並說明一下通常情況下爲什麼要做clock gating?簡單列舉通常實現的方法有哪些?

門控時鐘計數(clock gating)是一種非常簡單和有效的功耗控制方法,它的基本原理就是通過關閉晶片上暫時用不到的功能和它的時鐘,從而實現節省電流消耗的目的。

clk信號和clk_enable相與。

3.3 實現一個可以1-8分頻任意切換的分頻器,要求無論是奇數分頻還是偶數分頻,分頻後的時鐘的duty cycle都是50%。

佔空比模組:

module Duty_Cycle#( parameter HIGH_TIME = 1, //高電平時間 LOW_TIME = 2, //低電平時間 BIT_WIDTH = 2 //位寬 )( input clk, //時鐘 input rst_n, //非同步復位 output reg clk_out //輸出 ); reg [BIT_WIDTH-1:0] count; //計數器 always_ff @(posedge clk, negedge rst_n) begin if(!rst_n) begin count <= '0; end else if(count < HIGH_TIME) begin count <= count + 1; clk_out <= '1; end else if((count < HIGH_TIME+LOW_TIME-1) && (count >= HIGH_TIME))begin clk_out <= '0; count <= count + 1; end else if(count >= HIGH_TIME+LOW_TIME-1)begin clk_out <= '0; count <= '0; end else begin clk_out <= clk_out; count <= count; end end endmoduleselect this verilog

分頻模組:

module Frequency_Divider#( parameter DIV_COEFF = 3, //分頻係數 BIT_WIDTH = 2 //分頻係數位寬 )( input clk, //時鐘 input rst_n, //復位 output clk_out //分頻時鐘 ); //====================================================== //奇偶判斷,0爲偶 wire odd_even; wire [BIT_WIDTH-1:0] div_coeff; assign div_coeff = DIV_COEFF; assign odd_even = div_coeff[0]; //====================================================== //計算高低佔空比時間 parameter HIGH_TIME = DIV_COEFF/2; parameter LOW_TIME = DIV_COEFF-HIGH_TIME; //====================================================== //根據奇偶分頻分配時鐘 reg clk_p,clk_n; always_comb begin if(odd_even)begin clk_p = clk; clk_n = ~clk; end else begin clk_p = clk; clk_n = clk; end end wire clk_out_p,clk_out_n; Duty_Cycle#( .HIGH_TIME (HIGH_TIME), .LOW_TIME (LOW_TIME), .BIT_WIDTH (BIT_WIDTH) )u1_Duty_Cycle( .clk (clk_p), .rst_n (rst_n), .clk_out (clk_out_p) ); Duty_Cycle#( .HIGH_TIME (HIGH_TIME), .LOW_TIME (LOW_TIME), .BIT_WIDTH (BIT_WIDTH) )u2_Duty_Cycle( .clk (clk_n), .rst_n (rst_n), .clk_out (clk_out_n) ); assign clk_out = clk_out_p | clk_out_n; endmoduleselect this verilog

3.4 請畫一個狀態機(狀態轉換圖)來檢測序列位元流中的‘10011’。

3.5 現有三個輸入信號分別是a,b,c,並且前級DFF Clock到a,b,c的延時分別是Ta,Tb,Tc(Ta>Tb>Tc),請用兩個二輸入選擇器對a,b,c實現三輸入選擇輸出,畫電路圖並解釋設計思路,不需要考慮Clock Skew的影響。

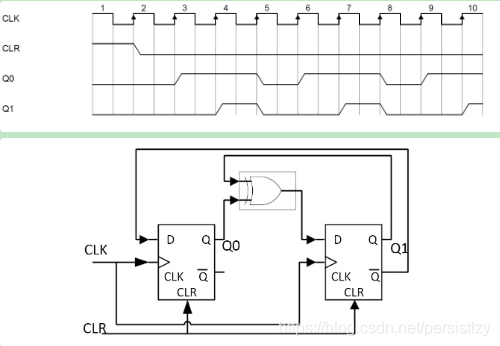

3.6 請畫出下列數位電路D觸發器輸出Q0,Q1的波形圖(復位之後Q0,Q1均爲0,畫出復位後8個時鐘週期)。

| Q0 | Q1 | |

|---|---|---|

| RESET | 0 | 0 |

| 第一個CLK | 1 | 0 |

| 第二個CLK | 1 | 1 |

| 第三個CLK | 0 | 0 |

| 第四個CLK | 1 | 0 |

| 第五個CLK | 1 | 1 |

| 第六個CLK | 0 | 0 |

| 第七個CLK | 1 | 0 |

| 第八個CLK | 1 | 1 |

3.7 分析程式碼覆蓋率時,verilog語句if(a||b&&c)有那幾個條件需要覆蓋?請用表格列出每種狀況下a/b/c的值(a/b/c均爲bit型別,如果是0或1都無所謂,請用「-」表示)。

a b c a||b&&c 1 - - 1 0 0 0 0 0 0 1 0 0 1 0 0 - 1 1 1 a爲真或b&&c爲真,結果爲真;

a和b&&c都爲假時,結果爲假。

3.8 使用任意一種程式設計或指令碼語言(C,Verilog,SystemVerilog,shell,perl,Python)實現32位元十六進制轉化爲二進制數(如abcd0123->10101011110011010000000100100011)。

。。。

3.9 使用C或Verilog/SystemVerilog,定義並實現一個函數,傳遞三個int型別參數A,B,C,函數返回後,A的值不變,B的值變爲A+B,C的值變爲A-C,請寫出函數原型定義與函數體的實現。

module A; int A; int B; int C; initial begin A=1; B=2; C=3; $display("%d,%d,%d",A,B,C); #1; func1(A,B,C); $display("%d,%d,%d",A,B,C); end function automatic viod func1(ref int A,ref int B,ref int C); A=A; B=A+B; C=A-C; endfunction endmoduleselect this verilog

3.10 請列出下述模組與中斷先關的所有功能測試點。

CPU通過APB介面讀寫暫存器,interrupt爲中斷輸出信號。模組內有如下暫存器,每個bit對應一種中斷源,當某個中斷enable位設定爲1時,內部邏輯被允許對中斷status位進行置位元運算;當任意一位status被置位1,且其mask位爲0時,則interrupt輸出爲高電平。CPU通過APB將status位寫1清0。如果所有status位都被清0後,interrupt輸出低電平。

中斷使能暫存器reg_int_enable[7:0];

中斷遮蔽暫存器reg_init_mask[7:0]; 中斷狀態暫存器reg_int_status[7:0](所有位都是W1C,即「寫1清0」)。

- APB匯流排對三個暫存器任意一位讀寫操作功能測試;

- reg_int_status暫存器任意一位W1C功能測試;

- APB匯流排設定reg_int_enable暫存器任意一位爲1,對應位status置位功能測試;

- 暫存器reg_int_enable和reg_int_status對應位置位時,且reg_int_mask對應位置0時,信號interrupt拉高功能測試;

- reg_int_status暫存器所有位W1C操作,信號interrupt拉低功能測試。

4 聯發科

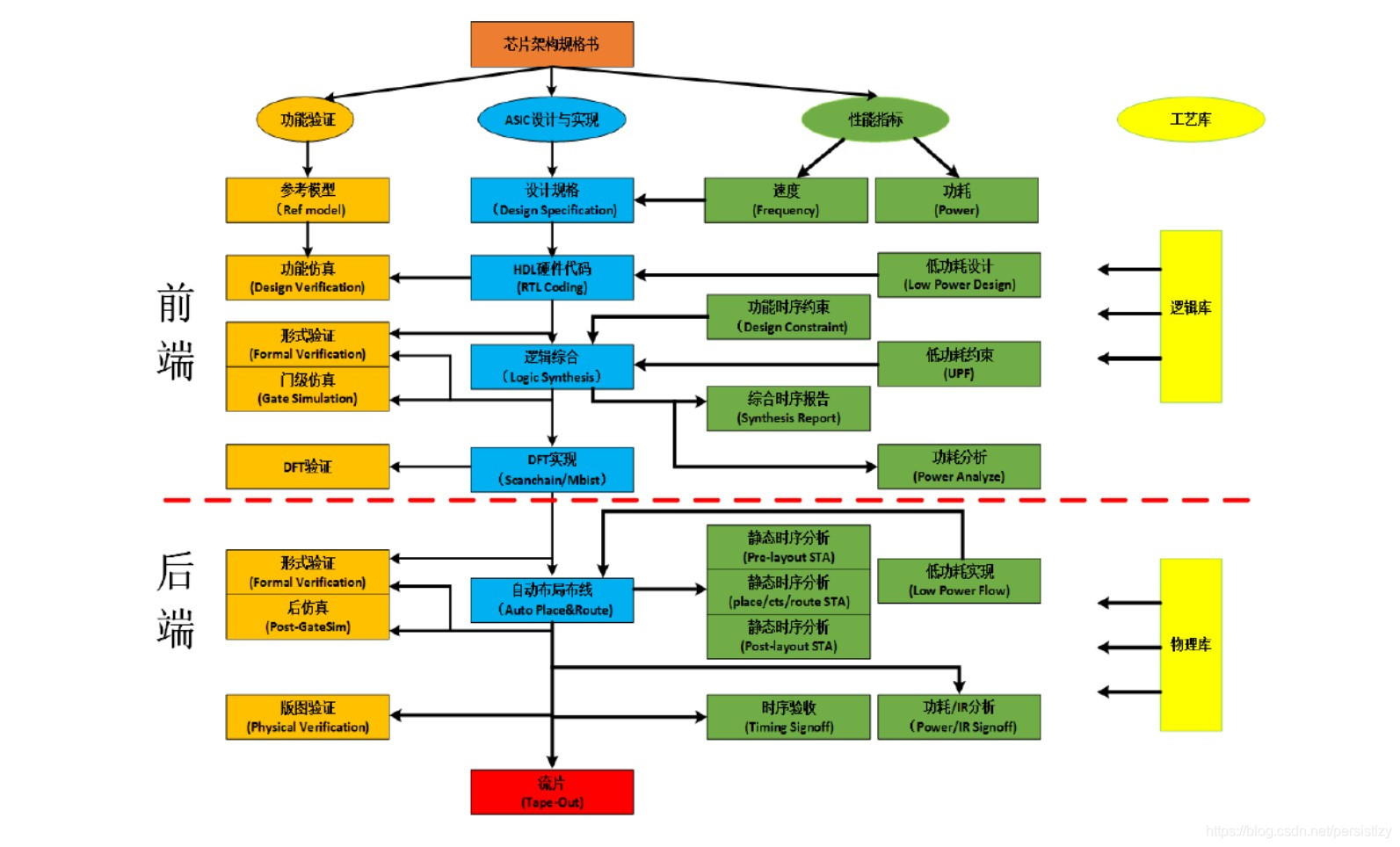

4.1 ASIC流程,說出5個以上環節;Verilog說出5個以上keyword。

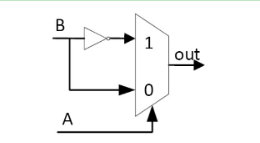

4.2 用一個mux和一個反相器實現xor,畫電路或Verilog程式碼實現。

A B XOR 0 0 0 0 1 1 1 0 1 1 1 0

4.3 如下圖所示:clk到Q的輸出延時爲T1min<T1<T1max,組合邏輯的延時爲:T2min<T2<T2max,時鐘週期爲T。滿足約束條件下,計算暫存器的setup和holdup。

T1max + T2max + Tsetup < T;

所以:Tsetup < T-T1max-T2max;

T1min + T2min > Tholdup。

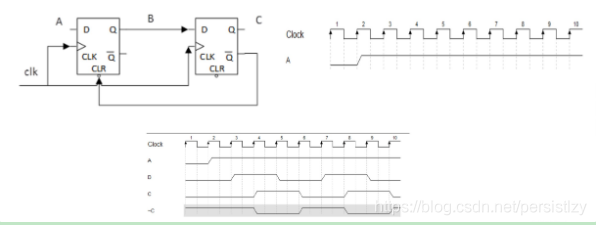

4.4 如下圖所示:根據A的波形,畫出B,C的波形,暫存器是同步清零的。

4.5 十進制的12.8125用二進制的數表示,十六進制的A8D6用八進制的數表示。

12 = 1100;

0.1825 × 4 = 3.25,表示:11.01,所以0.8125=0.1101;

所以,12.8125 = 1100.1101。

A8D6 = 1010100011010110 = 124326。

4.6 SV比Verilog強在哪裏?OVM、UVM、VMM是什麼?

SV支援物件導向的程式設計,支援斷言的語法,支援更多的數據型別。 VMM:Verification Methodology Manual,由ARM和Synopsys提出的,暫存器解決方案RAL機制 機製;

OVM:Open Verification Methodology,Mentor和Cadence共同提出,引進了factory機制 機製;

UVM:Universal Verification Methodology,通用驗證方法學,Accellera提出的,繼承了VMM和OVM的優點,克服了二者的缺點,代表了驗證方法學的主流,並得到了三大EDA廠商Cadence、Synopsys和Mentor Graphics的支援。

4.7 用Python或Perl寫程式,在xxx.log中找到fail單詞。

用你媽

4.8 int b = 100;int *a; a=&b有什麼意義?a=b有什麼意義?

a=&b定義指針變數a,變數指向整形數據b的地址,printf(「%d」,a)結果爲100;

a=b表示指針變數a的值爲100,a表示一個地址爲100的數據。

4.9

4.10 CPU cache miss/hit 區別

CPU要存取的數據在Cache中有快取,稱爲「命中」(Hit),反之則稱爲「缺失」(Miss)。

當運算器需要從記憶體中提取數據時,它首先在最高階的Cache中尋找然後在次高階的Cache中尋找。如果在Cache中找到,則稱爲命中hit;反之則稱爲不命中hit。

4.11 110序列選擇器,畫出狀態圖,寫出Verilog程式碼

module Sequential_Detector( input clk, input rst_n, input in, output out ); parameter s0 = 2'b00, s1 = 2'b01, s2 = 2'b10; reg [1:0] cur_state,next_state; reg out_r; always_ff(posedge clk,negedge rst_n)begin if(!rst_n) cur_state <= s0; else cur_state <= next_state; end always_comb begin case(cur_state) s0: next_state = (in==1'b1)?s1:s0; s1: next_state = (in==1'b1)?s2:s0; s2: nexe_state = (in==1'b0)?s0:s2; default: nexe_state = s0; endcase end always_ff@(posedge clk,negedge rst_n)begin if(!rst_n) out_r <= '0; else begin case(cur_state) s0: out_r <= '0; s1: out_r <= '0; s2: begin if(in==0) out_r <= '1; else out_r <= '0; end endcase end assign out = out_r; endmoduleselect this verilog

4.12 某夜,A、B、C、D四人要過橋,該橋每次只能通行2個人,只有一個手電筒,過橋必須持有手電筒,A、B、C、D四人單獨過橋的時間分別爲1分鐘、2分鐘、5分鐘和10分鐘。現要求四人最短時間完成過橋,不能折返,請問該如何操作?

AB先過去,A返回,CD再過去,B返回,AB再走一遍:2+1+10+2+2=17min。

5 平頭哥

5.1 SV裡四值變數有哪些?

- reg(單位元或多位元的無符號數);

- wire(線網);

- time(64位元的無符號數);

- integer(32位元的有符號數);

- logic(SV改進型reg)。

5.2 SV裏面動態陣列、關聯陣列、佇列各自的優缺點,應用場合。

- 特點:

- 動態陣列:可以在模擬時分配空間或者調整寬度,這樣在模擬中就可以使用最小的儲存量;

- 關聯陣列:用來儲存稀疏矩陣的元素,當隨一個非常大的地址空間進行定址時,SV只對實際寫入的元素分配空間,比定寬和動態陣列所> 佔用的空間要小得多;

- 佇列:結合了鏈表和陣列的優點,可以在佇列的任意位置增加或刪除元素,這類操作在效能上比動態陣列小得多,可以通過索引對任意> 元素進行存取;

- 應用場合:

- 動態陣列:隨機事務不確定位寬的大小;

- 關聯陣列:需要建立一個超大容量陣列,用關聯陣列來存放稀疏矩陣中的元素;

- 佇列:增加元素或刪除元素方便。

5.3 function和task的區別

function task 函數能呼叫另一個函數,但不能呼叫另一個任務 任務能呼叫另一個任務,也能呼叫另一個函數 函數總是在模擬0時刻就開始執行 任務可以在非零模擬時刻執行 函數一定不能包含任何延遲、事件或時序控制宣告語句 任務可以包含延遲、事件或時序控制宣告語句 函數至少有一個輸入變數,函數可以有多個輸入變數 任務可以沒有或者有多個輸入、輸出和雙向變數 函數只能返回一個值,函數不能有輸出或者雙向變數 任務不返回任何值,任務可以通過輸出或者雙向變數傳遞多個值

5.4 數據的型別轉換怎麼做?靜態強制型別轉換絕動態強制型別轉換有什麼區別?

- 靜態轉換:轉換時指定目標型別,並在需要轉換的表達式前加上單引號即可;

- 動態轉換:使用函數$cast。

- 區別:靜態型別轉換操作不對轉換值進行檢查,具有一定的危險性;動態轉換在執行時將進行檢查,如果轉換失敗會產生執行時錯誤。

5.5 virtual interface的作用

- interface只在module中宣告,在class中要用virtual interface;

- virtual interface是模擬執行時才連線到DUT上的,如果只是interface,在編譯時就必須進行連線,在class中時是automatic,在執行> 的時候產生;

- virtual interfacec主要完成介面的動態分配,只要在top層定義virtual interface,其它層不需要改變,直接通過interface傳遞參數> 即可;

- 消除絕對路徑,避免修改的時候改的東西很多。

5.6 多型

- 多型性(polymorphisn)是允許你將父物件設定稱爲一個和更多的他的子物件相同的技術,複製之後,父物件就可以根據當前賦值給它的子> 物件的特性以不同的方式運作。簡單的說就是允許將子類型別的指針賦值給父類別型別的指針。

- 多型的作用是爲了實現介面重用,爲了類在繼承和派生的時候,保證使用「家譜」中任一類的範例的某一屬性時的正確呼叫。

- 多型的實現方法:

- 覆蓋:是指子類重新定義父類別的虛擬函式的做法;

- 過載:是指允許存在多個同名函數,而這些函數的參數表不同(或許參數個數不同,或許參數型別不同,或許兩者都不同)。

驗證的好多。。。

5.14 fork join,fork join_any,fork join_none的用法

- fork join:當前速優子進程執行完畢,纔會繼續執行後面的進程;

- fork join_any:當前的任一子進程執行完畢後,纔會繼續執行後面的進程;

- fork join_none:當前的子進程並不阻塞後面的進程執行。

5.15 阻塞賦值和非阻塞賦值的區別。

- 阻塞賦值的操作符號用等號(=)表示,當前語句的賦值阻塞其它語句的賦值;

- 非阻塞賦值的操作符號用小於等於好(<=)表示,當前語句的賦值不阻塞其它語句的賦值。

5.16 Callback機制 機製的執行機理

Callback機制 機製,其實是使用OOP來實現的一種程式開發者向程式使用者提供的模組內部的介面,可以在Test_case的高度改變其他Component的一些行爲。

對於程式的開發者而言:

- 派生一個uvm_callback的類;

- typedef定義一個uvm_callbacks pool;

- 在對應的元件中註冊派生的callback類。 對於程式的使用者而言:

- 定義一個新的callback的派生子程式開發者所定義的類,並重寫類的方法;

- 在對應的test_base中範例化並新增callback的類。

5.17 clock模組爲什麼要放在top module中,不放在program中的原因?

SV介紹program的一個重要部分就是爲了將涉及和驗證的排程區域通過顯式的方式來安排,例如設計部分被建議放置在module中,而測試採樣部分被建議放置在program中,program中不能使用always,program中的模擬時間與RTL中的是有區別的,SV將同一模擬時刻分爲四個區域,相當於在原verilog的基礎上又爲program增加了一個執行區間,一個採樣區間,所以clk的定義不能放在program中。當program中的initial結束時,SV會呼叫$finish完成模擬。

5.18 談談對block level,chip level,product level驗證的理解?

- block level:

- 每個模組驗證首先要考慮的是哪些功能點是可以在模組一級完全驗證的的,這基於如下考慮:

- 內部功能如狀態機驗證;

- 內部數據儲存驗證;

- 數據打包功能、編解碼功能;

- 指令執行;

- 暫存器設定;

- 同時也需要考慮哪些功能無法在模組一級被驗證到:

- 與其他相鄰模組的互動信號;

- 與其他子系統的互動信號;

- 與晶片外部的互動信號;

- 與電源開關的驗證。

- chip level:

- 在晶片系統級,驗證平臺的複用性較高,主要因爲:

- 外圍的驗證元件不需要像模組級、子系統級的元件數量多且經常需要更新,它們主要側重於驗證晶片的輸入輸出;

- 晶片內部的子系統之間的互動、共同作業檢查主要交給了處理器和子系統,從暫存器檢查和數據檢查入手,寫直接測試用例。

- 在晶片系統級的驗證側重於不同子系統之間的信號互動問題,以及實現更貼近實際使用的用例。這裏的實習用例並非是在系統軟體層面的,而是將> 系統軟體層面的場景進一步拆分爲多個模組互動情景,再分類測試的。

- product level:

- 直接的軟體測試激勵,可根據示波器等工具觀察波形變化,也可以根據SDK軟體debug。

5.19 讓用sv來驗證一塊memory的讀寫1G空間的過程

對地址空間分割區間平均分成多份,對每份地址採取固定地址讀寫和隨機讀寫兩種策略:連續寫,連續讀,讀緊跟着寫;同時注意邊界地址的讀寫操作。

5.20 UVM架構

5.21 請畫出時鐘的門控電路,要求是在使能信號無效時將時鐘輸出門控到高(低)電平,門控過程中請注意不產生毛刺。

5.22 請用ROM實現以下Verilog程式碼對應的功能:

always@(posedge clk) begin

if(a&&b)

q <= 1'b0;

else

q <= !q;

end

select this verilog

ROM查詢表:

a b D Q 0 0 0 1 0 0 1 0 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 0

5.23 設計一個時序電路,輸入是2個8bit的無符號數,輸出是這兩個數的最小公倍數。要求電路面積儘可能的小。請使用Verilog語言實現。

- 首先可以採用輾轉相除法或者相減法求解最大公約數MCD;

- 然後利用A×B=MCD×LCM,求解最小公倍數;

- 其中輾轉相減法和除法運算可採用狀態機的方式實現。

module lcm#( parameter DATA_W = 8 )( input clk, input rst_n, input [DATA_W-1:0] a, input [DATA_W-1:0] b, input vld_in, output [DATA_W*2-1:0] lcm_out, output [DATA_W-1:0] mcd_out, output vld_out, output ready ); reg [DATA_W*2-1:0] mcd,a_buf,b_buf; reg [DATA_W*2-1:0] mul_buf; reg mcd_vld; reg [1:0] cur_stata,next_state; parameter IDLE = 2'b00; s0 = 2'b01; s1 = 2'b10; s2 = 2'b11; always_ff@(posedge clk , negedge rst_n)begin if(!rst_n) cur_state <= '0; else cur_state <= next_state; end always_ff@(posedge clk , negedge rst_n)begin if(!rst_n)begin next_state <= IDLE; mcd <= '0; mcd_vld <= '0; a_buf <= '0; b_buf <= '0; mul_buf <= '0; end else begin case(cur_state) IDLE: if(vld_in)begin a_buf <= a; b_buf <= b; next_state <= s0; mul_buf <= a*b; mcd_vld <= '0; end else begin next_state <= IDLE; mcd_vld <= '0; end s0: if(a_buf!=b_buf)begin if(a_buf>b_buf)begin a_buf <= a_buf - b_buf; b_buf <= b_buf; end else begin b_buf <= b_buf-a_buf; a_buf <= b_buf; end next_state <= s0; end else begin next_state <= s1; end s1: begin mcd <= b_buf; mcd_vld <= 1'b1; next_state <= IDLE; end default: next_state <= IDLE; end endcase end end div #( .DATA_W(DATA_W*2) ) u_div( .clk, .rst_n, .vld_in(mcd_vld), .ready, .dividend(mul_bur), .divisor(mcd), .quotient(lcm_out), .remainder(), .vld_out ); assign mcd_out = mcd; endmoduleselect this verilog

module div#( parameter DATA_W = 8 )( input clk, input rst_n, input vld_in, output ready, input [DATA_W-1:0] dividend, input [DATA_W-1:0] divisor, output [DATA_W-1:0] quotient, output [DATA_W-1:0] remainder, output vld_out ); reg [DATA_W*2-1:0] dividend_e; reg [DATA_W*2-1:0] divisor_e; reg [DATA_W-1:0] quotient_e; reg [DATA_W-1:0] remainder_e; reg [1:0] cur_state,next_state; reg [DATA_W-1:0] count; paratemer IDLE = 2'b00, SUB = 2'b01, SHIFT= 2'b10, DONE = 2'b11; always_ff@(posedge clk or negedge rst_n)begin if(!rst_n)begin dividend_e <= '0; divisor_e <= '0; quotient_e <= '0; remainder_e <= '0; count <= '0; cur_state <= IDLE; end else begin case (sur_state) IDLE: begin dividend_e <= ,dividend}; divisor_e <= {divisor,{DATA_W{1'b0}}}; if(vld_in) cur_state <= SUB; else cur_state <= IDLE; end SUB: begin if(dividend_e >= devisor_e)begin quotient_e <= {quotient_e[DATA_W-2:0],1'b1}; dividend_e <= dividend_e - divisor_e; end else begin quotient_e <= {quotient_e[DATA_W-2:0],1'b0}; dividend_e <= dividend_e; end cur_state <= SHFIT; end SHIFT:begin if(count<DATA_W)begin cur_state <= SUB; dividend_e <= dividend_e<<1; cound <= count + 1; end else begin cur_state <= DONE; remainder_e <= dividend_e[DATA_W*2-1:DATA_W]; end end DONE: begin count <='0; cur_state <= IDLE; end endcase end end assign quotient = quotient_e; assign remainder = remainder_e; assign ready = (cur_state==IDLE)?1'b1:1'b0; assign vld_out = (cur_state==DONE)?1'b1:1'b0; endmoduleselect this verilog

或者我寫的:

//------------------------------------------------------------------------------ // //Module Name: LCM.v //Department: Xidian University //Function Description: 求最大公約數和最小公倍數 // //------------------------------------------------------------------------------ // //Version Design Coding Simulata Review Rel data //V1.0 Verdvana Verdvana Verdvana 2020-01-04 // //----------------------------------------------------------------------------------- // //Version Modified History //V1.0 // //----------------------------------------------------------------------------------- `timescale 1ns/1ns module LCM #( parameter DATA_WIDTH = 8 //數據位寬 )( //**********時鐘&復位***********// input clk, //時鐘 input rst_n, //復位 //**********控制信號***********// input en, //使能 //**********輸入數據***********// input [DATA_WIDTH-1:0] a, //第一個數 input [DATA_WIDTH-1:0] b, //第二個數 //**********輸出數據***********// output valid, //輸出數據有效信號 output [DATA_WIDTH*2-1:0] gcd, //最大公約數 output [DATA_WIDTH*2-1:0] lcm //最小公倍數 ); //=================================================== //使能上升沿檢測 reg en_r1,en_r2; always_ff @(posedge clk, negedge rst_n) begin if(!rst_n) begin en_r1 <= '0; en_r2 <= '0; end else begin en_r1 <= en; en_r2 <= en_r1; end end wire enable; assign enable = en_r1 && ~en_r2; //=================================================== //輾轉相除計算最大公約數 reg [DATA_WIDTH-1:0] numer,denom; wire [DATA_WIDTH-1:0]quotient,remain; DIV#( .DATA_WIDTH(DATA_WIDTH) //數據位寬 )u_DIV( .numer, //被除數 .denom, //除數 .quotient, //商 .remain //餘數 ); reg [DATA_WIDTH*2-1:0] gcd_r; always_ff @(posedge clk, negedge rst_n) begin if(!rst_n) begin numer <= '0; denom <= '0; end else if(valid) begin numer <= '0; denom <= '0; end else if(enable) begin numer <= a; denom <= b; end else if(remain!='0)begin numer <= denom; denom <= remain; end else begin gcd_r <= denom; end end assign gcd = (valid)?gcd_r:'0; //=================================================== //產生輸出有效信號 reg valid_r; always_ff @(posedge clk, negedge rst_n) begin if(!rst_n) begin valid_r <= '0; end else if((remain=='0)&&(denom!='0)&&(valid_r=='0)) begin valid_r <= '1; end else begin valid_r <= '0; end end assign valid = valid_r; //=================================================== //計算最小公倍數 wire [DATA_WIDTH*2-1:0] lcm_r; wire [DATA_WIDTH*2-1:0] product; assign product = a*b; DIV#( .DATA_WIDTH(DATA_WIDTH*2) //數據位寬 )ulcm_DIV( .numer(product), //被除數 .denom(gcd), //除數 .quotient(lcm_r), //商 .remain() //餘數 ); assign lcm = (valid)?lcm_r:'0; endmoduleselect this verilog

//------------------------------------------------------------------------------ // //Module Name: DIV.v //Department: Xidian University //Function Description: 整數除法器 // //------------------------------------------------------------------------------ // //Version Design Coding Simulata Review Rel data //V1.0 Verdvana Verdvana Verdvana 2020-01-03 // //----------------------------------------------------------------------------------- // //Version Modified History //V1.0 // //----------------------------------------------------------------------------------- module DIV #( DATA_WIDTH = 8 //數據位寬 )( //**********輸入***********// input [DATA_WIDTH-1:0] numer, //被除數 input [DATA_WIDTH-1:0] denom, //除數 //**********輸出***********// output [DATA_WIDTH-1:0] quotient, //商 output [DATA_WIDTH-1:0] remain //餘數 ); reg [DATA_WIDTH*2-1:0] numer_r; reg [DATA_WIDTH*2-1:0] denom_r; reg quotient_e [DATA_WIDTH]; always_comb begin numer_r = ,numer}; //左邊補齊0 denom_r = denom << DATA_WIDTH; //右邊補齊0 end reg [DATA_WIDTH*2-1:0] numer_e [DATA_WIDTH+1]; reg [DATA_WIDTH*2-1:0] denom_e [DATA_WIDTH+1]; assign numer_e[0] = numer_r; assign denom_e[0] = denom_r >> 1; generate genvar i; for(i=0;i<DATA_WIDTH;i++) begin:shift always_comb begin if( numer_e[i] >= denom_e[i])begin quotient_e[DATA_WIDTH-1-i] = 1'b1; numer_e[i+1] = numer_e[i]-denom_e[i]; denom_e[i+1] = denom_e[i] >> 1; end else begin quotient_e[DATA_WIDTH-1-i] = 1'b0; numer_e[i+1] =numer_e[i]; denom_e[i+1] = denom_e[i] >> 1; end end assign quotient[i] = quotient_e[i]; //得出商 end endgenerate assign remain = numer_e[DATA_WIDTH]; //取餘數 endmoduleselect this verilog

6 其它

6.1 常用邏輯電平

低速:RS232、RS485、RS422、TTL、CMOS、LVTTL、LVCMOS、ECL、LVPECL等;

高速:LVDS、GTL、PGTL、CML、HSTL、SSTL等。

6.2 可程式化邏輯裝置

ROM、PLA、FPLA、PAL、GAL、EPLD、FPGA、CPLD等

6.3 基爾霍夫定律

KCL:電路中的任意節點,任意時刻流入該節點的電流等於流出該節點的電流;

KVL:在任何一個閉合迴路中,各元件上的電壓降的代數和等於電動勢的代數和。

6.4 描述反饋電路的概念,列舉他們的應用

反饋是將放大器輸出信號(電壓或電流)的一部分或全部,回收到放大器輸入端與輸入信號進行比較(相加或相減),並用比較所得的有效輸入信號去控制輸出,負反饋可以用來穩定輸出信號或者增益,也可以擴充套件通頻帶,特別適合於自動控制系統。正反饋可以形成振盪,適合振盪電路和波形發生電路。

6.5 負反饋種類及其優點

電壓並聯反饋,電流串聯反饋,電壓串聯反饋和電流並聯反饋。

降低放大器的增益靈敏度,改變輸入電阻和輸出電阻,改善放大器的線性和非線性失真,有效地擴充套件,放大器的通頻帶,自動調節作用。

6.6 放大電路的頻率補償的目的是什麼,有哪些方法

頻率補償:是爲了改變頻率特性,減小時鐘和相位差,使輸入輸出頻率同步。

相位補償:通常是改善穩定裕度,相位補償與頻率補償的目標有時是矛盾的。

不同的電路或者說不同的元器件對不同頻率的放大倍數是不相同的,如果輸入信號不是單一頻率,就會造成 高頻放大的倍數大,低頻放大的倍數小,結果輸出的波形就產生了失真。

放大電路中頻率補償的目的:一是改善放大電路的高頻特性,二是克服由於引入負反饋而可能出現自激振盪現象,使放大器能夠穩定工作。

在放大電路中,由於電晶體結電容的存在常常會使放大電路頻率響應的高頻段不理想,爲了解決這一問題,常用的方法就是在電路中引入負反饋。然後,負反饋的引入又引入了新的問題,那就是負反饋電路會出現自激振盪現象,所以爲了使放大電路能夠正常穩定工作,必須對放大電路進行頻率補償。

頻率補償的方法可以分爲超前補償和滯後補償,主要是通過接入一些阻容元件來改變放大電路的開環增益在高頻段的相頻特性,目前使用最多的就是鎖相環。

6.7 有源濾波器和無源濾波器的區別

無源濾波器:這種電路主要有無源元件 R、L 和 C 組成;

有源濾波器:整合運放和 R、C 組成,具有不用電感、體積小、重量輕等優點。整合運放的開環電壓增益和輸入阻抗均很高,輸出電阻小,構成有源濾波電路後還具有一定的電壓放大和緩衝作用。但整合運放頻寬有限,所以目前的有源濾波電路的工作頻率難以做得很高。

6.8 什麼是頻率響應,怎麼纔算是穩定的頻率響應,簡述改變頻率響應曲線的幾個方法

這裏僅對放大電路的頻率響應進行說明。在放大電路中,由於電抗元件(如電容、電感線圈等)及電晶體極間電容的存在,當輸入信號的頻率過低或過高時,放大電路的放大倍數的數值均會降低,而且還將產生相位超前或之後現象。也就是說,放大電路的放大倍數(或者稱爲增益)和輸入信號頻率是一種函數關係,我們就把這種函數關係稱爲放大電路的頻率響應或頻率特性。

放大電路的頻率響應可以用幅頻特性曲線和相頻特性曲線來描述,如果一個放大電路的幅頻特性曲線是一條平行於x軸的直線(或在關心的頻率範圍內平行於x軸),而相頻特性曲線是一條通過原點的直線(或在關心的頻率範圍是條通過原點的直線),那麼該頻率響應就是穩定的。

改變頻率響應的方法主要有:

- 改變放大電路的元器件參數;

- 引入新的 元器件來改善現有放大電路的頻率響應;

- 在原有放大電路上串聯新的放大電路構成多級放大電路。

6.9 DAC和ADC的實現各有哪些方法?

實現DAC轉換的方法有:

- 權電阻網路 D/A 轉換;

- 倒梯形網路 D/A 轉換;

- 權電流網路 D/A 轉換;

- 權電容網路 D/A 轉換;

- 開關樹形 D/A 轉換等。

實現ADC轉換的方法有:

- 並聯比較型A/D轉換;

- 反饋比較型A/D轉換;

- 雙積分型A/D轉換;

- V-F變換型A/D轉換。

6.10 A/D電路組成、工作原理

A/D 電路由取樣、量化和編碼三部分組成。

由於模擬信號在時間上是連續信 號而數位信號在時間上是離散信號,因此A/D轉換的第一步就是要按照奈奎斯 特採樣定律對模擬信號進行採樣。又由於數位信號在數值上也是不連續的,也就是說數位信號的取值只有有限個數值,因此需要對採樣後的數據儘量量化,使其 量化到有效電平上,編碼就是對量化後的數值進行多進位制到二進制二進制的轉換。

6.11 爲什麼一個標準的倒相器中P管的寬長比要比N管的寬長比大?

和載流子有關,P管是空穴導電,N管電子導電,電子的遷移率大於空穴,同樣的電場下,N管的電流大於P管,因此要增大P管的寬長比,使之對稱,這樣才能 纔能使得兩者上升時間下降時間相等、高低電平的噪聲容限一樣、充電和放電是時間相等。

6.12 鎖相環有哪幾部分組成?

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL)鎖相環的特點是:利用外部輸入的參考信號控制環路內部振盪信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用於閉環跟蹤電路。

鎖相環在工作的過程中,當輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環名稱的由來鎖相環通常由鑑相器(PD)、環路濾波器(LF)和壓控振盪器(VCO)三部 分組成。

鎖相環中的鑑相器又稱爲相位比較器,它的作用是檢測輸入信號和輸出信號的相位差,並將檢測出的相位差信號轉換成電壓信號輸出,該信號經低通濾波器濾波後形成壓控振盪器的控制電壓,對振盪器輸出信號的頻率實施控制。

告辭。