基於Xlinx Artix-7 xc7a35t 的數位電子設計實戰課程(四)

基於Xlinx7 xc7a35t 的FPGA開發日記(四)

沒想到在短短幾天之內我的部落格存取量就近千了,感謝大家的支援。接下來我會將更多的經驗和技術分享給大家。但其實我也是入門級選手,所以如果有錯誤請大家不吝賜教,謝謝!

我們來進行實戰開發前的最後一課:Verilog硬體語言的學習。

這節課先將一些基礎知識和數據型別,下節課會將運算子和賦值語句。

Verilog HDL 語言是目前最流行的兩種硬體語言之一,因爲設計這門語言很大程度上參考了C語言的思路,所以之前學習過C語言的同學可以輕鬆掌握這門語言。

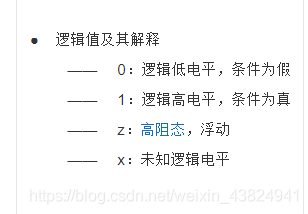

首先,在Verilog開發環境中一共有以上四種邏輯狀態。

在Verilog中表示數位的方法有三種:

1.<位寬>’<進位制><數位>

2.<進位制><數位> (這種方式缺位寬,此時至少有32位元)

3.<數位> (這種方式預設爲十進制,位寬32位元)

任何一門語言都有數據型別,Verilog的數據型別分爲:

線網型(net) 和 變數型。

一、線網型

顧名思義,實際上就是在FPGA內部以線(「與」邏輯運算)連線的量。例如我設定一個D觸發器的輸出爲Q1,然後我定義一個線網型變數A等於Q1,於是A就一直隨着Q1的值變化。

線網型數據有兩個關鍵詞,第一個是wire,意思就是線,他代表的就是定義一個量,在接下一直隨着另一個量的變化而變化,比如說

wire clk_out;

assign clk_out = c_out; //這裏的assign是一個賦值語句,後面會說

這兩行程式碼的意思就是定義一個線網型變數 clk_out ,它的值等於c_out變數,並且隨着c_out 的變化而變化。

第二個關鍵詞是parameter,它的作用是定義一個識別符號,也就是常數,類似於c語言的宏定義。parameter 是可以重定義的。

parameter width = 3;

//這行程式碼的意思就是定義一個常數等於3,也就是說接下來程式碼中出現 width,程式就會自動將它替換成3。

二、變數

變數一共只有一個關鍵字reg,對應着我們能夠完成時序電路功能的暫存器,所以reg也被稱爲暫存器型。

記憶體的標準定義形式是:

reg [msb:lsb] memory [upper:lower]

例如:

reg[3:0] memory1[63:0]

//定義memory1 爲64個4位元暫存器陣列

而常用的也有:

reg[4:0] dog ; //沒有說明個數,預設一個,也就是定義了一個5位暫存器dog。

數據型別的介紹就到這裏,在下節課講述運算子和賦值語句之前,我們還需要說一些Verilog語言中的注意事項:

- Verilog程式由模組構成,每個模組巢狀在module 和 endmodule的宣告之中。

- 每個source file 只能有一個頂層模組。

- 每個模組要進行埠定義,例如 module A (input b,outout c) //定義一個模組A,它有一個輸入量b,一個輸出量c。

- 時序部分在always塊內,在其中只能對暫存器變數賦值。

- 對線網型變數只能在always塊外賦值。

- Verilog程式格式自由,一行可以書寫多個語句,一個語句也可以分多行書寫。

- 除了endmodule、begin、end、fork、join外,每個語句和數據定義最後要有分號。

- 可用/…/ 和 / /…進行註釋。

本節課的學習就到這裏,很快我們會更新下節課結束verilog的學習,並且進入實戰環節。如果想進行實戰操作的同學請到Xlinx網站下載Vivado(版本至少2017)並且註冊免費獲得lisence。

謝謝觀看!