FPGA開發之時序收斂10個小技巧

1、好的程式碼風格

1)程式碼要跟器件結構相關

2)避免非同步復位,非同步復位同步化,全域性復位區域性化

3)層次的邊界要加流水寄存

\quad

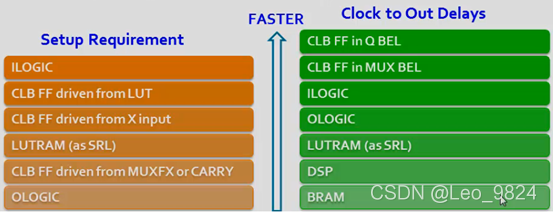

例如:BRAM中有兩級register,第一級在內部,第二級在外部slice裡的寄器。不同功能模組內部的暫存器要求的速度也不一樣,不同位置的暫存器速度不一樣。如ILOGIC中的暫存器對setup要求最高(暫存器最慢),OLOGIC中的暫存器對setup的要求最低(暫存器最快)。Slice中的暫存器速度最快,所以經常在mem,clock模組輸出端增加一個slice的register。

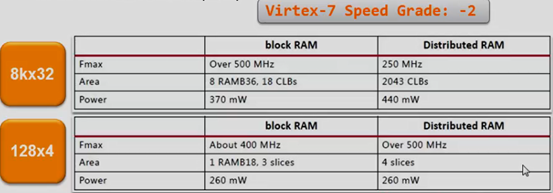

4)Block RAM和DRAM的選擇

\quad

根據應用需求適當選擇

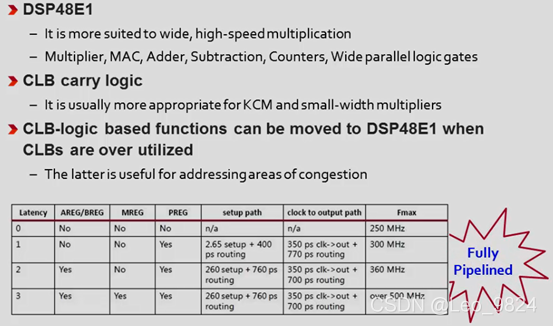

4)流水線技術是提高系統頻率的一種方法

2、精準的時序約束

\quad

精簡而準確的約束是時序收斂的必要條件,Baseline基線方法是充分條件。

1)檢查時序約束命令:

\quad

check_timing

2)小技巧:

\quad

如果約束過緊可以用以下命令:

\quad

set_clock_uncertainty –setup 0.3 [get_clocks my_CLK]

3、管理高扇出網路

\quad

高扇出網路幾乎是限制FPGA設計實現更高效能的第一大障礙,所以需要嚴肅對待設計中的高扇出。

1)查詢最大的扇出網路命令:

\quad

Report_high_fanout_nets –load_types –max_nets 2 –timing

2)約束高扇出網路命令

\quad

max_fanout可以限定其扇出值,讓工具在實現過程中複製驅動端暫存器來優化。也可以多次物理優化phys_opt_design改善扇出。

4、層次化設計結構

\quad

自底向上的設計流程

5、跨時鐘域路徑的設計和約束

1)預設模式下所有時鐘域都是related

2)同步時鐘跨時鐘域

\quad

擁有相同的源和確定的相位關係

3)非同步時鐘跨時鐘域

\quad

源不相同,沒有確定相位關係

\quad

簡單的處理方式:雙register(ASYNC_REG),FIFO,握手方式同步

4)常用的約束命令

\quad

時鐘約束

set_multicycle_path:多時鐘路徑約束

set_clock_groups:時鐘分組,等效set_false_path

set_false_path:偽時鐘路徑約束

\quad CDC結構問題檢查

report_cdc

methodology_checks

\quad 跨時鐘域問題檢查

report_clock_interation

\quad 檢視時鐘網路

report_clock_networks

6、少而精的物理約束

\quad

萬不得已的時候 不要手動佈局LOC,如果要做也是對關鍵元件關鍵路徑做。

7、選擇恰當的策略

\quad

不同的工程包含不同的設計策略:效能、功耗、面積、流程

\quad

可以制訂自己的策略,如:利用勾點檔案,在設計前設計後調Phys_opt_design

8、共用控制訊號

1)儘量整合頻率相同的時鐘和時鐘使能訊號;

2)在生成IP時選擇「共用邏輯」功能,則可以在不同IP間儘可能的共用時鐘資源;

3)復位

\quad

a) 儘量少使用復位

\quad

b) 必須復位時採用同步復位

\quad

c) 用高電平有效復位

\quad

d) 避免非同步復位

4)常用命令

\quad

report_control_sets

9、讀懂紀錄檔和時序報告

1)注重critical warnings 和 errors

2)檢查DRC violations

\quad

methodology_checks

\quad

timing_checks

3)設計分析報告

\quad

Report_design_analysis(非常有用)用來報告關鍵路徑上的潛在問題以及設計的擁塞程度。

10、充分發揮tcl的作用