時序約束(二)

時序約束(二)

上一篇對時序約束原理做了概述,網上也有講的比較清楚的,或者網上小梅哥和尤凱元老師得視訊都講的很不錯,這裡主要是講一下原理概述,重點是做一些範例演練,或者自己目前手頭的專案遇到的情況。

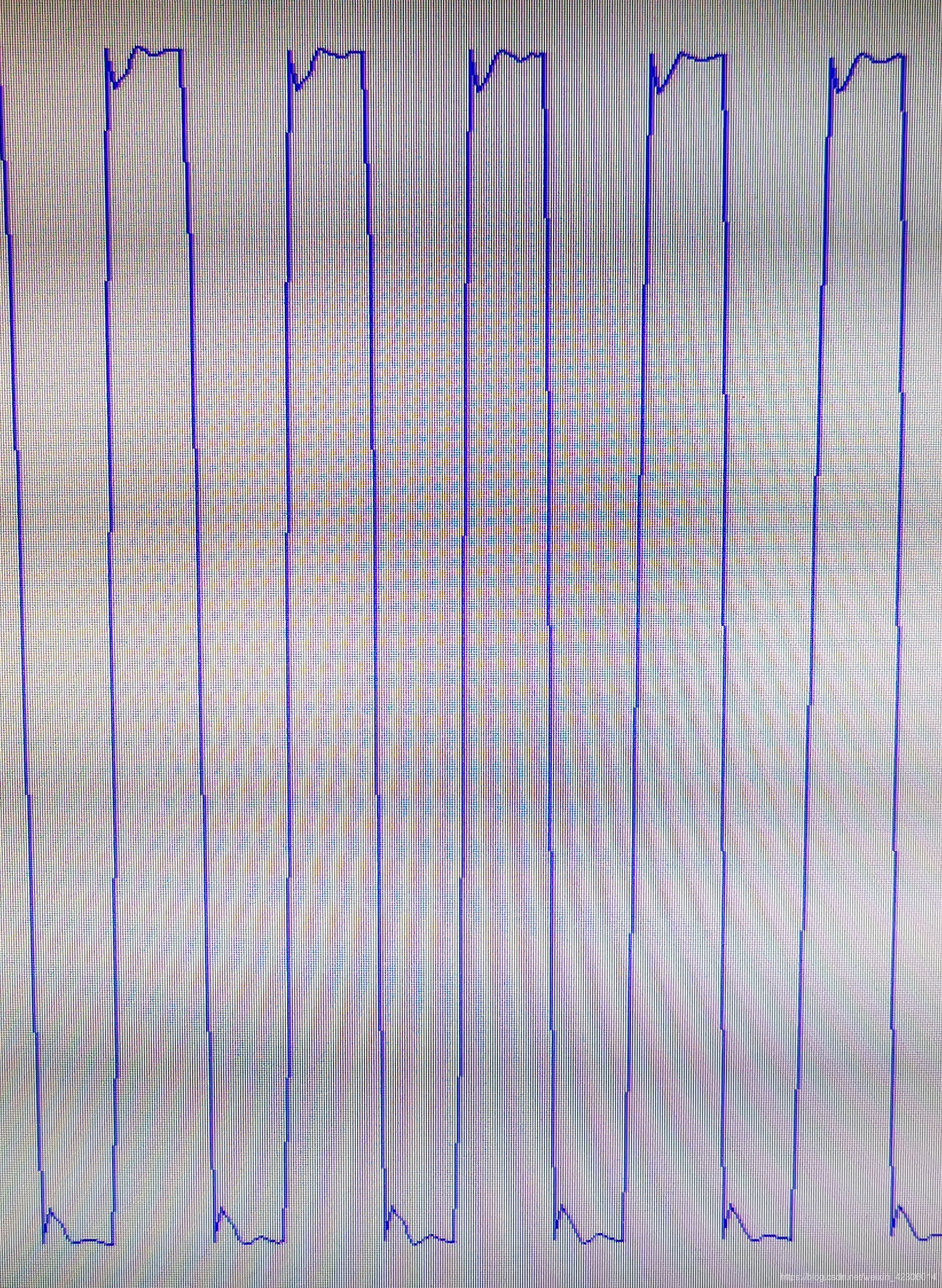

目前手頭的專案是高速的AD資料採集,300M的取樣時鐘,DDR的資料傳輸模式,也就是說時鐘週期3.33ns,上下沿取樣,相當於時鐘週期只有1.667ns,這裡不進行正確的時序約束,很可能無法正常的採集資料。這裡我們先看看沒有正確的約束,或者沒有約束情況下資料採集的情況。如下圖:

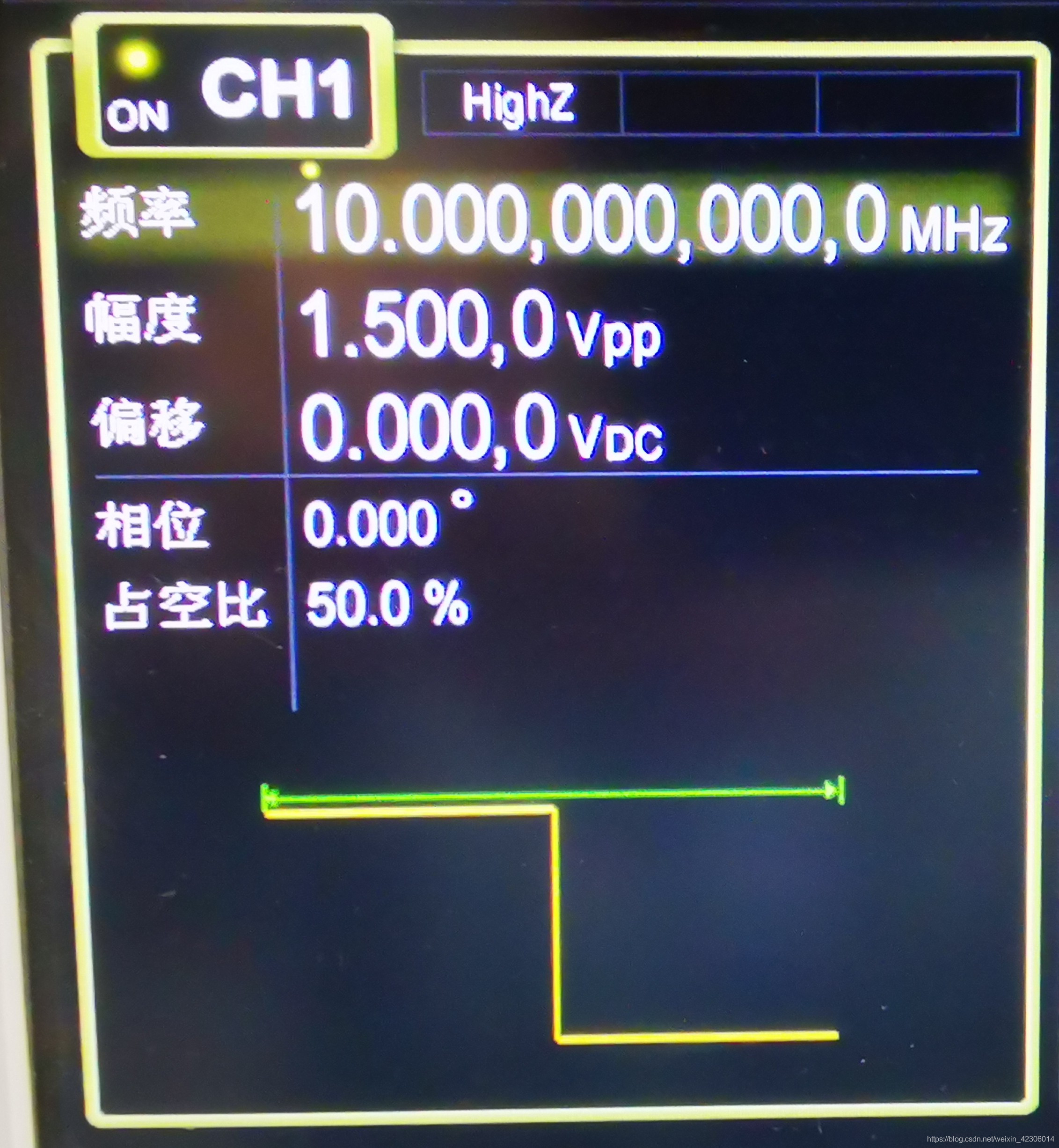

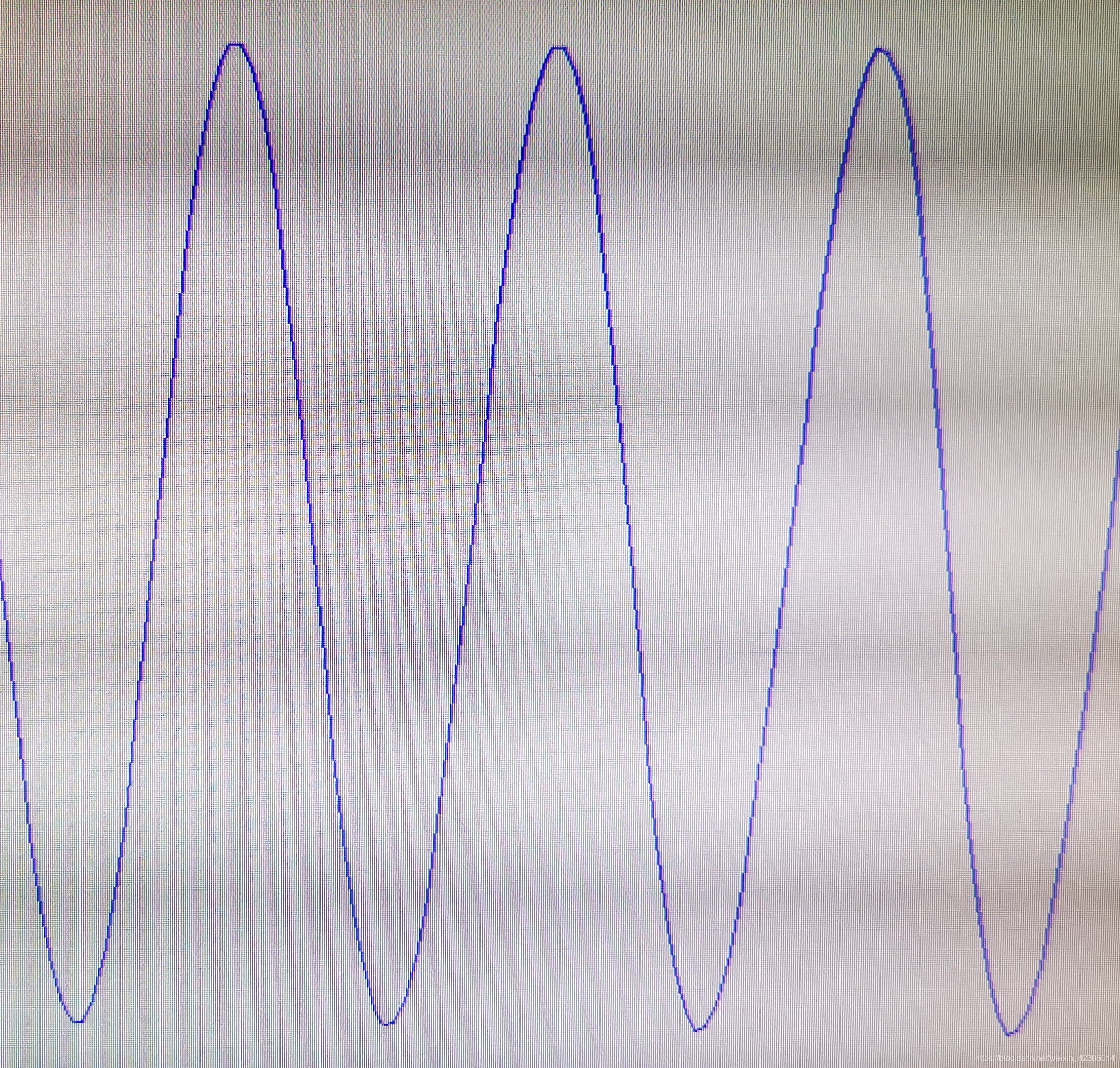

1.時序未約束或錯誤約束情況下,輸入訊號5M正弦波和方波如下:

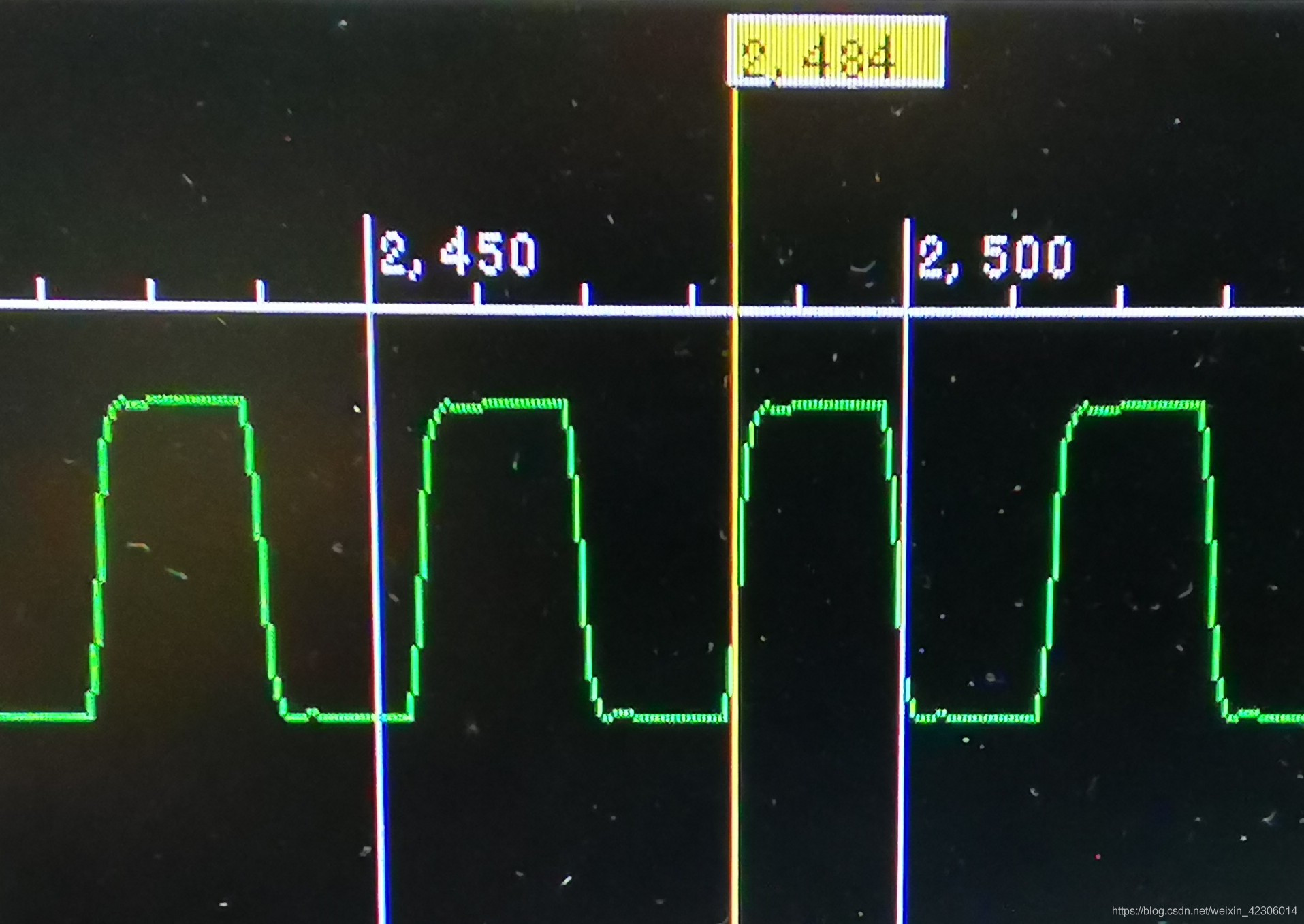

FPGA取樣後儲存到ram中,由DSP採集後做顯示得到的結果如下:

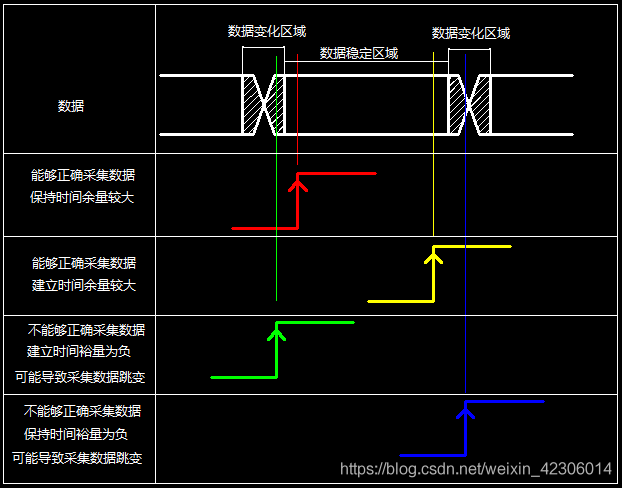

我們可以看到輸入訊號沒有毛刺,而採集到的訊號卻有了明顯的毛刺,直接原因就是時序沒有正確約束,時鐘上升下降沿採集資料時,不能夠滿足建立保持時間,也就是說,時鐘取樣時,資料不穩定,正在進行交變。示意圖如下:

由圖可以直觀的看到,時序約束所要做的就是使時鐘的取樣沿落在資料的穩定區域。如何能讓時鐘取樣沿落在資料穩定區域呢?實際情況是時鐘與資料在電路中傳播都有延時,如果建立時間不滿足可以讓時鐘延時大一些,也可以讓資料延時小一些,如果保持時間不滿足,可以讓時鐘延時小一些,也可以讓資料延時大一些,具體情況具體分析,例如修改邏輯,增加流水,加鎖相環移相,input/output delay中還可以改變外部器件的時鐘資料相位關係等方法。所有的這些方法都是為了讓時鐘取樣沿落在資料穩定區。實際例子和操作我們後面再具體分析。

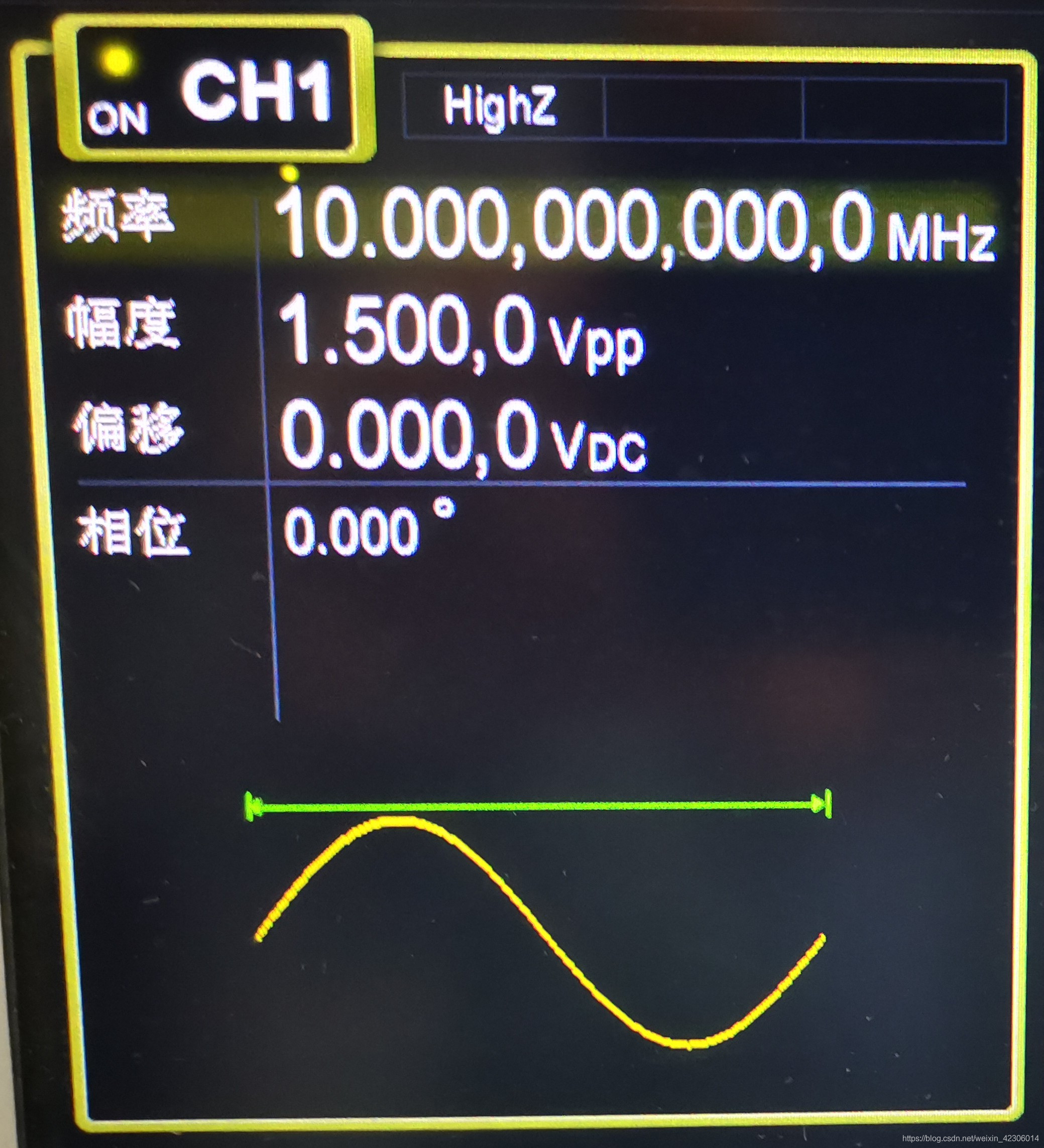

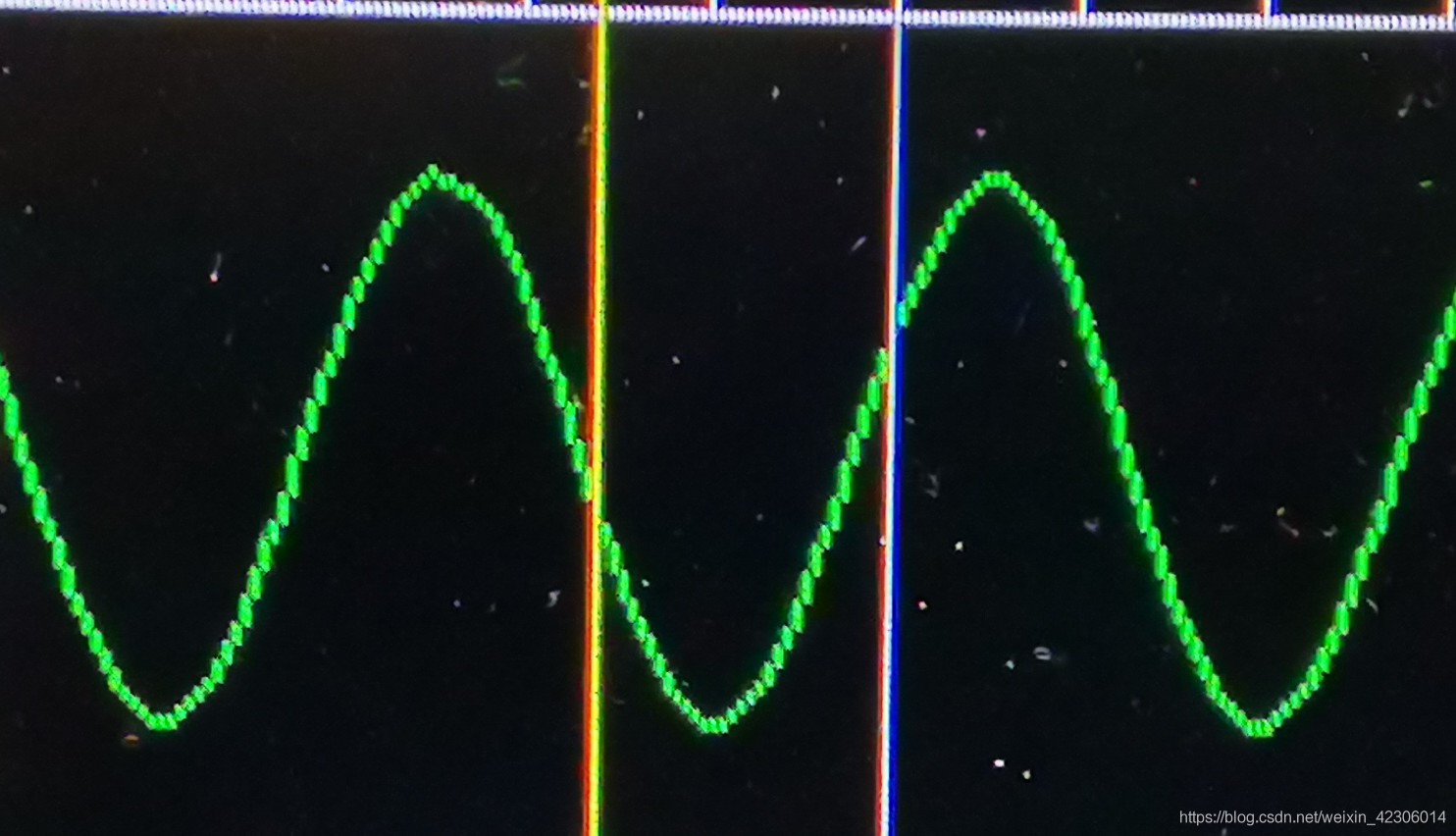

2.時序約束情況下,輸入訊號10M正弦波和方波如下:

FPGA取樣後儲存到ram中,由DSP採集後做顯示得到的結果如下:

FPGA取樣後ila直接抓取資料做顯示得到的結果如下:

可以看到正確的時序約束後波形的毛刺消失了,採集的訊號與輸入的訊號一致,基本還原了原始輸入訊號,這是後續訊號處理的前提,如果採集資料都不正確,後面也就談不上資料的計算處理。

這一篇主要通過一個時序約束範例顯示了時序約束的重要性,後面會通過vivado工程範例的操作來具體瞭解一下vivado工具是如何進行時序約束的。