數位IC設計瞭解篇(8)初識數位IC設計前端

-

前端做什麼工作

數位前端設計也稱邏輯設計,前端以設計架構爲起點,以功能正確且滿足目標時序的網表爲終點,用邏輯電路實現預期的功能。主要包括:規則書制定、系統架構設計、部件詳細設計、HDL編碼、模擬驗證、SDC編寫、邏輯綜合、STA檢查、形式化驗證等,系統架構設計最難掌握,需要有豐富的設計經驗,對應用場景也需要有深入的理解。

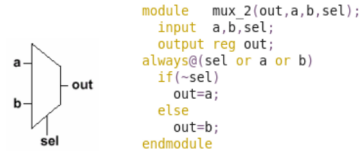

前端設計師需要掌握的最基本技能就是實現編碼,但編碼不是數位前端設計的全部,它只是前端設計過程中的部分工作。下面 下麪編寫一個MUX邏輯,MUX的行爲可以描述爲:只要信號a或b或sel發生變化,如果sel爲0則選擇a輸出;否則選擇b輸出。

學習前端設計首先要掌握數位電路基礎知識並建立硬體意識,基本的數位電路像與或非門、D觸發器、計數器、移位暫存器、狀態機、多路選擇器、譯碼器等一定要掌握,所有複雜的電路都可由這些基本電路構成,軟體設計和邏輯設計的不同要明白,軟體是順序執行思維,而邏輯設計需要併發思維。數位電路是由很多的與非門及D觸發器構成,上電之後所有部件都同時執行,不會因爲A觸發器的程式碼描述在 B觸發器之前A觸發器就先工作,事實上,RTL級程式碼書寫的先後順序在綜合成網表檔案後就消失了,取代的是基本邏輯電路之間的互聯關係描述。數位電路功能中存在先後順序的關係,但這種順序不是靠程式碼的先後順序來實現,它的先後順序是基於時間軸(時鐘)來實現,它的承載體是時序邏輯(觸發器)。

因此邏輯設計需要的是一種併發的思維,設計師需要用併發的思維去考慮電路的設計。 -

前端設計流程

①規格制定(一般多個部門共同參與)

規格制定是晶片設計中最重要的步驟之一,這個步驟就像是在設計建築前, 先決定要幾間房間、浴室,有什麼建築法規需要遵守,在確定好所有的功能之後再進行設計,這樣纔不用再花額外的時間進行後續修改。如果規格還制定好就開始設計,很難確保設計中不出任何差錯。

規格制定前需要進行市場調研,收集客戶需求,第一步是確定晶片的功能、功耗、效能,對大方向做設定;接着需要確定相容那些規範,如無線網絡卡的晶片就需要符合 IEEE 802.11 等規範;最後則是確立這顆 IC 的製作方法,將不同功能分配成不同的單元,並確立不同單元間連結的方法,如此便完成規格的制定。

②系統架構和部件詳細設計(做設計方案)

這個步驟就像初步有了建築的規劃,將整體輪廓描繪了出來,方便後續製圖。根據規則需求編寫詳細設計文件,明確具體架構,劃分功能模組。對不確定的功能進行建模測試確保方案可順利實現,這個階段就是確定晶片設計的細節。

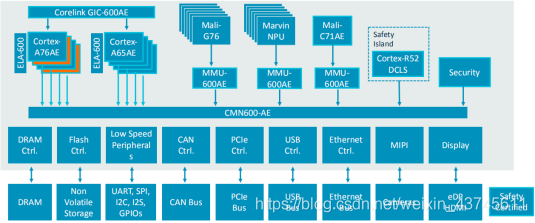

下圖爲基於ARM的自動駕駛晶片系統架構圖。

做好設計方案非常重要,這裏說的方案絕不是隻擺幾個框圖,設計的時候需要做總體設計方案、邏輯詳細設計方案,這兩種方案包括了很多東西,總體方案主要是一級功能模組的劃分及介面時序的定義,而邏輯詳細方案就是程式碼的文字及圖形描述(模組內部所有關鍵信號的時序最好都設計好)。

③HDL編碼

很多人在做邏輯設計時喜歡一上來就狂寫程式碼,寫到一半後發現了功能問題,只好推倒重來,反覆 反復好幾次才能 纔能做到模擬基本正確,最後通過修補湊時序達到對的功能。這個做法除了設計週期長外,程式碼的品質也難以保證,往往存在很多冗餘的邏輯,甚至會有一些隱藏較深的bug。所以數位邏輯設計一定要方案先行,根據方案寫程式碼,這樣才能 纔能在寫程式碼時做到胸有成竹,避免邏輯混亂的情況。其實在方案階段把時序設計好後,模組內部各個信號之間的邏輯關係也就理得差不多了,之後就是將它翻譯成程式碼的體力勞動了。

HDL編碼這個階段是要使用硬體描述語言(HDL)描述實現功能模組,也就是把電路描寫出來。常使用的HDL有 Verilog、VHDL等,國內一般使用verilog編寫RTL(暫存器傳輸級)程式碼。

④功能驗證

功能驗證就是檢驗編碼設計的正確性,不符合規格的要重新設計和編碼。設計和模擬驗證是反覆 反復迭代的過程,直到驗證結果顯示完全符合規格標準。設計師一般只做基本通路驗證,功能和程式碼的詳細驗證一般由驗證工程師完成,驗證和設計可同步進行。

常用模擬工具:Synopsys的VCS,Mentor ModelSim(Linux版本爲Questasim),Cadence Xcelium(老版本叫incisive)。

⑤編寫SDC和程式碼檢查

SDC是一種約束檔案,這裏的約束是針對綜合和佈局佈線工具而言的。爲什麼會有約束這個東西出現呢?主要原因是EDA軟體比較笨,難以理解設計師的心思,如果設計師不把更詳細的資訊告訴它的話它就幹不好活,所以設計師需要用SDC來把設計意圖(時序、面積和功耗等)傳達給EDA工具。這裏說的程式碼檢查是指用EDA工具(spyglass最常用)來檢查和診斷設計中可能存在的潛在問題,然後用其分析和追蹤問題的根源,RTL級一般做lint、CDC(多時鐘域檢查)、Constraint(約束)三個方面的檢查。

常用的檢查工具:spyglass

⑥ 邏輯綜合(可能放後端做或者前後端交接設計師做)

邏輯綜合就是把HDL程式碼翻譯成門級網表(netlist),綜合需RTL程式碼和SDC檔案。邏輯綜合需要基於特定的綜合庫,不同庫中的閘電路基本標準單元(standard cell)的面積,時序參數是不一樣的,因此綜合出來的電路在時序,面積上是有差異的。一般來說,綜合完成後需要再次做模擬驗證(這個也稱爲後模擬)。

常用綜合工具:Synopsys的dc,cadence的genus

⑦靜態時序分析(STA,可能放後端做)

Static Timing Analysis(STA),靜態時序分析屬於驗證範疇,它主要是在時序上對電路進行驗證,檢查電路是否存在建立時間(setup time)和保持時間(hold time)的違例(violation)。這個是數位電路基礎知識,一個暫存器出現這兩個時序違例時,是沒有辦法正確採樣數據和輸出數據的,所以以暫存器爲基礎的數位晶片功能肯定會出現問題。

STA工具:Synopsys的Prime Time。

⑧形式驗證(可能放後端做)

形式化驗證屬驗證範疇,它是從功能上(STA是時序上)對綜合後的網表進行驗證。常用的就是等價性檢查方法,以功能驗證後的HDL設計爲參考,對比綜合後的網表功能,他們是否在功能上存在等價性。這樣做是爲了保證在邏輯綜合過程中沒有改變原先HDL描述的電路功能。

形式驗證工具:Synopsys的Formality,cadence Conformal -

前端設計入門要學的知識

前端設計所需知識很廣,最好的學習方法就是專案實踐,光看書和視訊教學是學不會的,真正入門得靠專案。重點在於掌握設計思想和分析問題的方法,形成良好書寫習慣(遵循程式碼書寫、命名規範),最好把常用的基本的電路標準化、固定化。高手水平高並不是體現在他能寫出一些很奇特的電路,相反水平高體現在他們總能將複雜的電路用一些很樸素的基本電路去描述。

前端設計一般需要掌握的知識有Linux操作基礎、數位電子基礎、verilog語言、計算機體系結構、指令碼語言、EDA模擬工具等。

以下書籍可以作爲入門教材。

《數位電子技術基礎(第五版)》閻石 主編

《Verilog數位系統設計教學》

《Verilog程式設計藝術》

《專用積體電路設計實用教學》

《SOC設計方法與實現》

《數位設計和計算機體系結構》

《綜合與時序分析的設計約束》

《SystemVerilog測試驗證平臺(中文版)》

本文是通過收集網上資源整理,版權屬於原作者。