【Computer Organization筆記20】靜態記憶體及高速緩衝記憶體

本次筆記內容:

P39 計算機組成原理(39)

P40 計算機組成原理(40)

我的計組筆記彙總:計算機組原理成筆記

視訊地址:計算機組成原理 清華大學劉衛東 全58講 國家精品課程 1080P 更完

幻燈片見我的 GitHub 倉庫:計算機組成原理 src/slides

本節課幻燈片:組成原理31 dram.pptx

這節課與2013年11月28日,按理說應該要交實驗報告了。

實驗目標概述

主要模組設計

- 硬體:Datapath、Controller、Memory、I/O

- 軟體:對系統軟體的修改、應用軟體

主要模組實現

實驗成果展示

實驗心得和體會

提交材料

- 實驗報告

- 視訊材料

- 完整原始碼及相關說明

靜態記憶體是快取記憶體記憶體的基礎,因此,先講靜態記憶體。

文章目錄

本節內容提要

- 動態記憶體儲存原理

- 靜態記憶體儲存原理

- 高速緩衝記憶體(Cache)概述

- Cache的地址對映

-

- 直接對映

-

- 全相聯

-

- 多路組相連

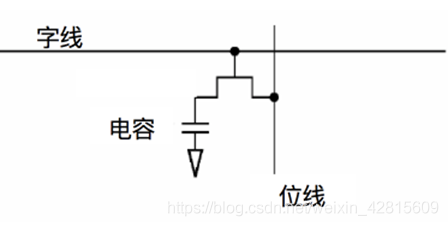

動態記憶體複習

動態記憶體原理

寫:

- 往位線上送數據

- 選擇字線

讀:

- 將位線上置高電平

- 選中字線

- 感知電容是否放電並放大

- 寫回

重新整理:

- 定期的批次讀操作

動態記憶體的特點

儲存容量高:

- 單位儲存單元面積小

存取速度慢:

- 電容充放電

- 重新整理

能耗低、成本低。

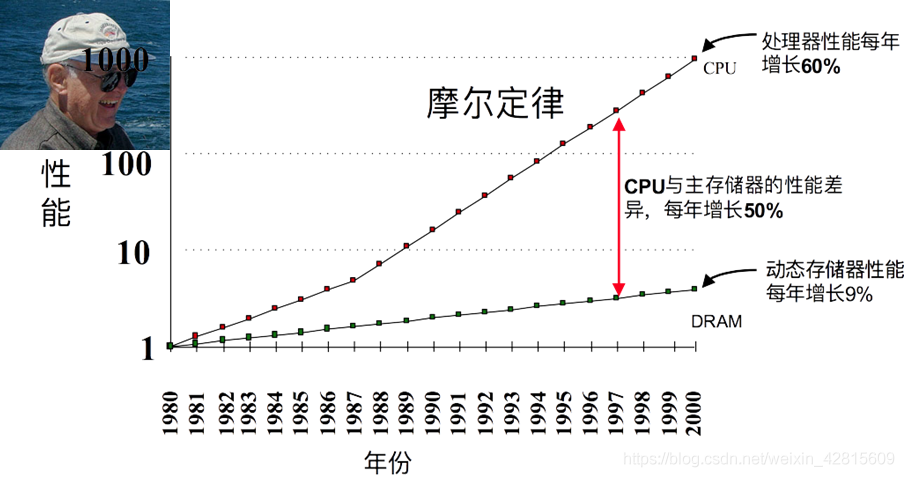

摩爾定律

如何彌補這個鴻溝呢?答案:靜態記憶體。

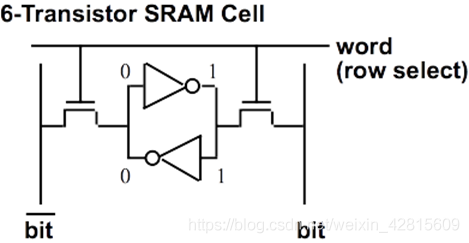

靜態記憶體

也用 CPU 的觸發器結構做儲存就可以了。

靜態記憶體儲存單元

寫1:

- 在位線上設定使()

- 使字線選通

讀:

- 使和都充爲高電平Vdd

- 使字線選通

- 根據觸發器的狀態,將使其中一條位線電平爲低

- 放大器感知和的變化,讀出儲存的值

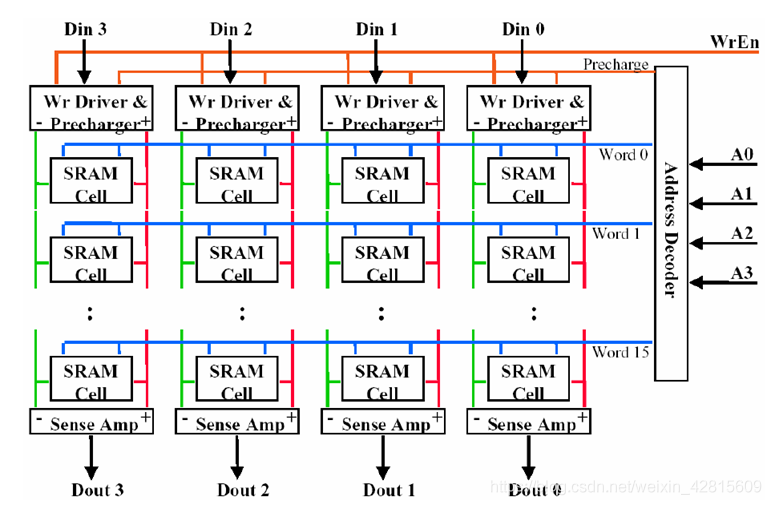

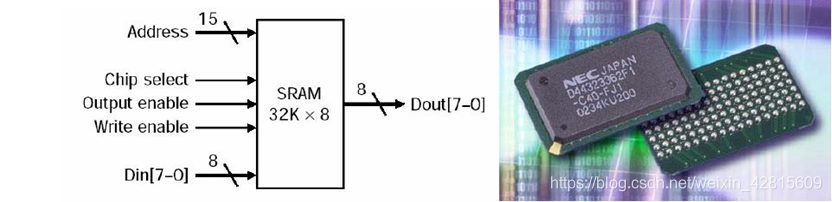

靜態記憶體典型組織方式

上面,地址進行譯碼後,選中數據。

如何做到存取的每一個地址響應速度都是一樣的?如何實現隨機存取?

- 因爲每個二進制位都有一個讀寫(光碟就不是);

- 因爲都是經過 Decoder ,再進行選擇的。

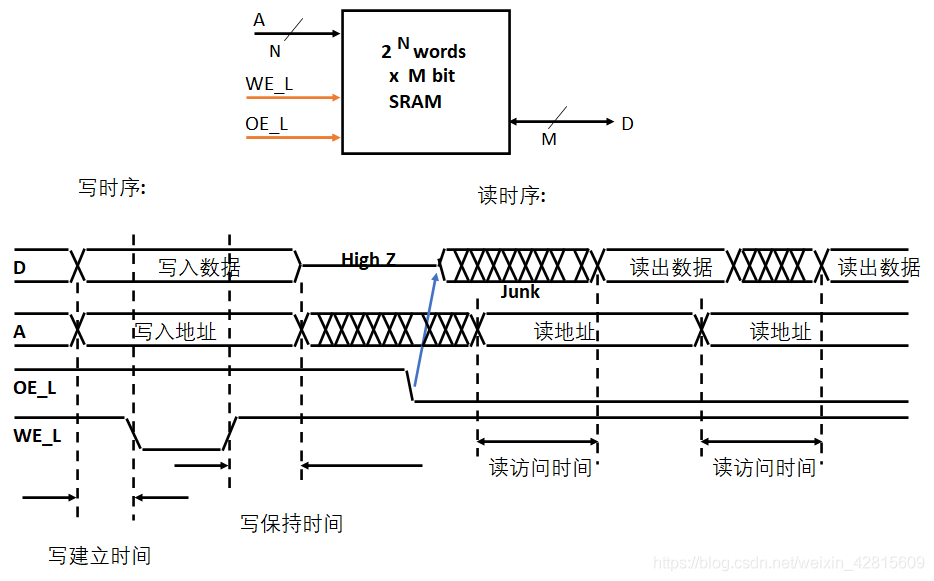

SRAM典型時序

靜態記憶體特點

- 速度快

- 儲存密度低,單位面積儲存容量小

- 數據入/出共用管腳

- 能耗高(用了很多電晶體)

- 成本高

靜態和動態記憶體晶片特性

「靜態」之所以爲「靜態」,是因爲其不需要像動態記憶體一樣重新整理。通電即保證恆定穩定數據。

| 特點 | SRAM | DRAM |

|---|---|---|

| 儲存資訊 | 觸發器 | 電容 |

| 破壞性讀出 | 非 | 是 |

| 需要重新整理 | 不要 | 需要 |

| 送行列地址 | 同時送 | 分兩次送 |

| 執行速度 | 快 | 慢 |

| 整合度 | 低 | 高 |

| 發熱量 | 大 | 小 |

| 儲存成本 | 高 | 低 |

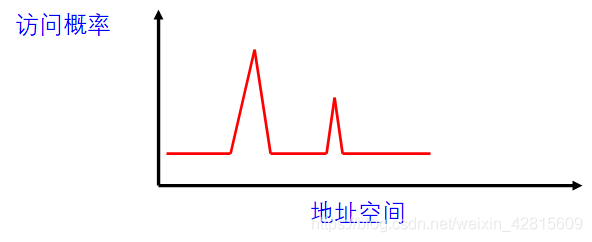

複習程式執行的區域性性原理

程式執行時的區域性性原理表現在:

- 在一小段

時間內,最近被存取過的程式和數據很可能再次被存取 - 在

空間上這些被存取的程式和數據往往集中在一小片儲存區 - 在存取

順序上,指令順序執行比轉移執行的可能性大(大約5:1)

合理地把程式和數據分配在不同儲存媒介中。

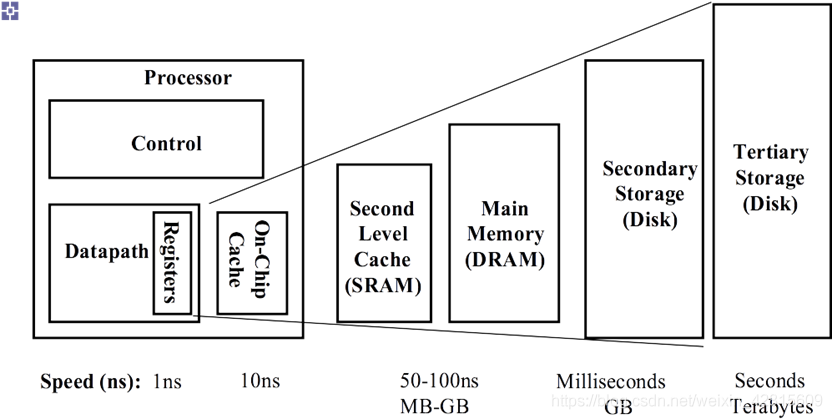

層次記憶體系統

利用程式的區域性性原理:

- 以最低廉的價格提供儘可能大的儲存空間

- 以最快速的技術實現高速儲存存取

一個程式的例子

for (i=0; i<1000; i++) {

for (j=0; j<1000; j++ ) {

a[i] = b[i] + c[i];

}

}

If err {……}

else for (i=0; i<1000; i++) {

for (j=0; j<1000; j++ ) {

e[i] = d[i] * a[i];

}

}

- 數據流存取的區域性性;

- 指令存取的區域性性;

- 不同的程式段可能存取不同的記憶體空間。

總結:程式的區域性性原理

程式在一定的時間段內通常只存取較小的地址空間,兩種區域性性:

- 時間區域性性

- 空間區域性性

層次儲存系統

使用高速緩衝記憶體Cache來提高CPU對記憶體的平均存取速度。

- 時間區域性性:最近被存取的資訊很可能還要被存取。將最近被存取的資訊項裝入到Cache中。

- 空間區域性性:最近被存取的資訊臨近的資訊也可能被存取。將最近被存取的資訊項臨近的資訊一起裝入到Cache中。

高速緩衝記憶體Cache

定義與特點

定義:設定於主記憶體和CPU之間的記憶體,用高速的靜態記憶體實現,快取了CPU頻繁存取的資訊。

特點:

- 高速:與CPU的執行速度基本匹配

- 透明:完全硬體管理,對程式設計師透明

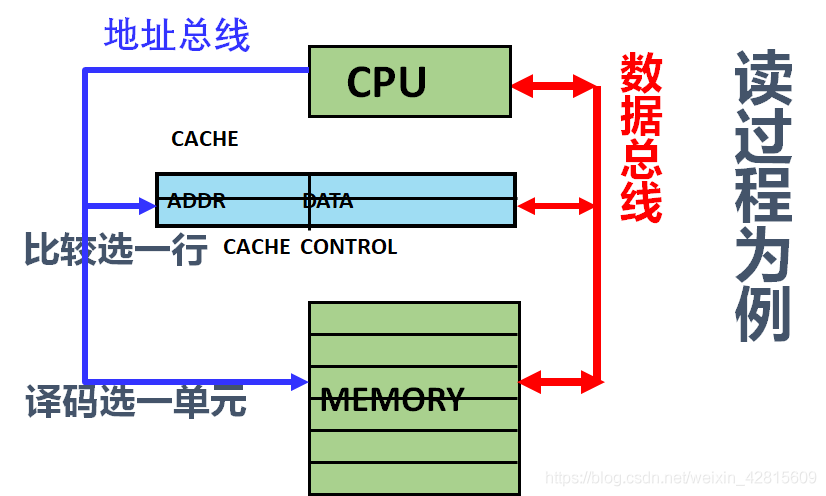

Cache的基本執行原理

如上,其實先不存取主記憶體,先存取 CACHE 。可能 CPU 要等50個週期去讀,有了 CACHE ,可能等 1 個週期就結束了。

要解決的問題

-

地址和Cache行之間的對映關係:

如何根據主記憶體地址得到Cache中的數據? -

數據之間一致性:

Cache中的內容是否已經是主記憶體對應地址的內容? -

數據交換的粒度:

Cache中的內容與主記憶體內容以多大的粒度交換? -

Cache內容裝入和替換策略

如何提高Cache的命中率?

Cache 參數

塊(Line):數據交換的最小單位

命中(Hit):在較高層次中發現要存取的內容

- 命中率(Hit Rate):命中次數/存取次數

- 命中時間:存取在較高層次中數據的時間

缺失(Miss):需要在較低層次中存取塊

- 缺失率(Miss Rate):1-命中率

- 缺失損失(Miss Penalty):替換較高層次數據塊的時間+將該塊交付給處理器的時間

注意:命中時間<<缺失損失

平均存取時間=HR*命中時間+(1-HR)*缺失損失

參數典型數值

塊大小:4~128 Bytes

命中時間:1~4週期

失效損失:

- 存取時間:6~10個週期

- 傳輸時間:2~22個週期

命中率:80%~99%

Cache容量:1KB~256KB

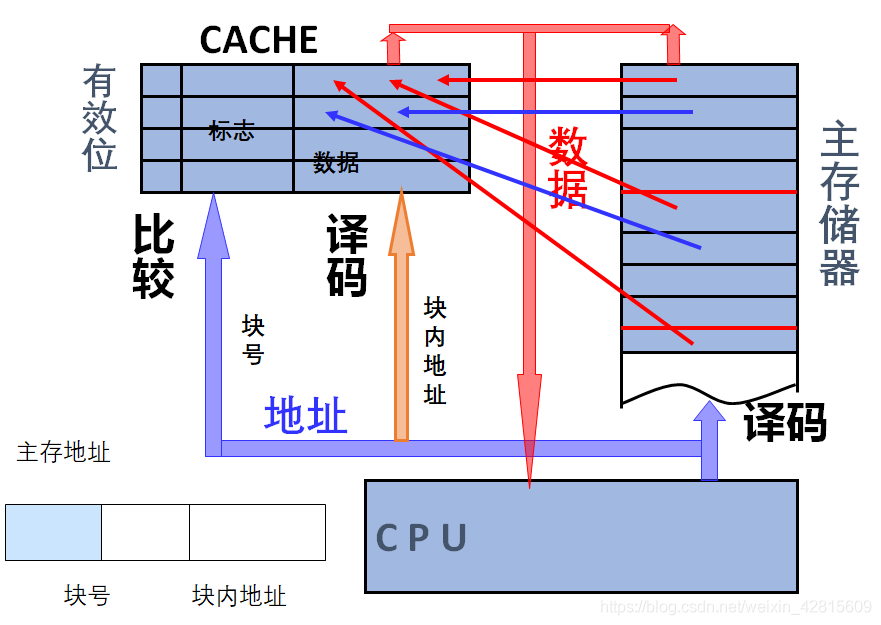

如何對映主記憶體

全相聯方式

如何把塊放入 CACHE ?CACHE 明顯比主記憶體容量小得多。因此,不光要裝入數據,還要裝入數據標記:把哪些數據裝入了。對應地,主記憶體儲器的主記憶體地址分爲兩部分:塊號、塊內地址。

此外,還有應該有有效位,表達這條數據是否可用。

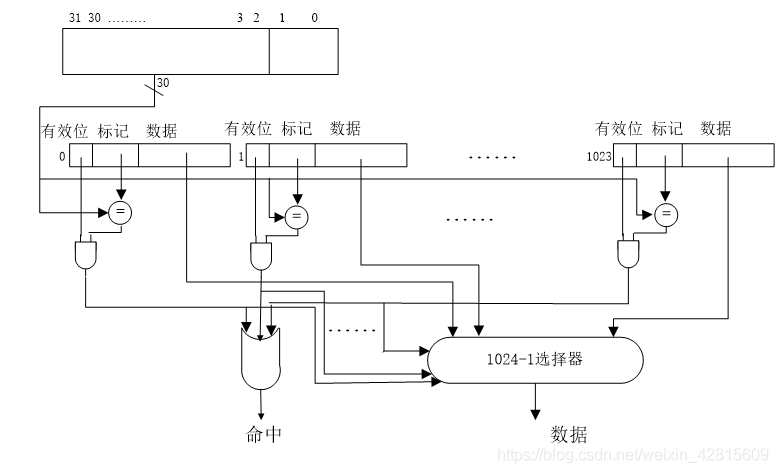

全相連對映硬體實現舉例

主記憶體:4GB,Cache:4KB,塊大小:4B,全相聯標記位數?

解:

4GB 記憶體,地址需要 32 位表達;

Cache 有 4KB ,每塊 4B ,則有 1k 塊。

一塊有 4B,塊內地址用 2 位表達;

其他的位都是用來做標記的。

因此,標記位數爲 32-2=30 。

因此,在讀主記憶體時,把主記憶體地址的高 30 位作爲標記去比較,如果與 Cache 的某條/塊相等,且有效位爲1,那麼會讀這個數據。具體是哪個位元組,則由塊內地址決定。

特點

- 主記憶體的字塊可以和 Cache 的任何字塊對應,利用率高,方式靈活。

- 標誌位較長,比較電路的成本太高。如果主記憶體空間有 2m 塊,則標誌位要有 m 位。同時,如果 Cache 有 n 塊,則需要有 n 個比較電路。使用成本太高。

能不能設計一個只有一個比較器的 Cache ?

- 犧牲掉塊和行的隨機對映關係;

- 建立唯一的對映。

這就是直接對映方式。

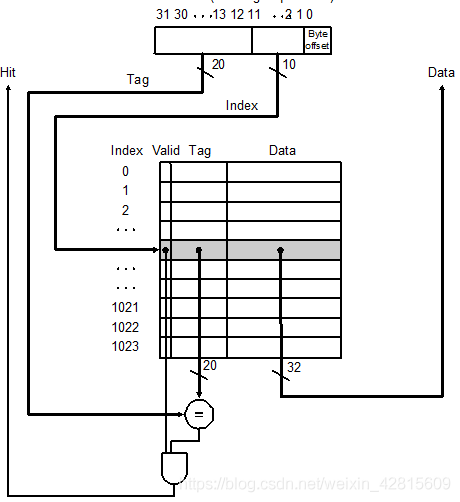

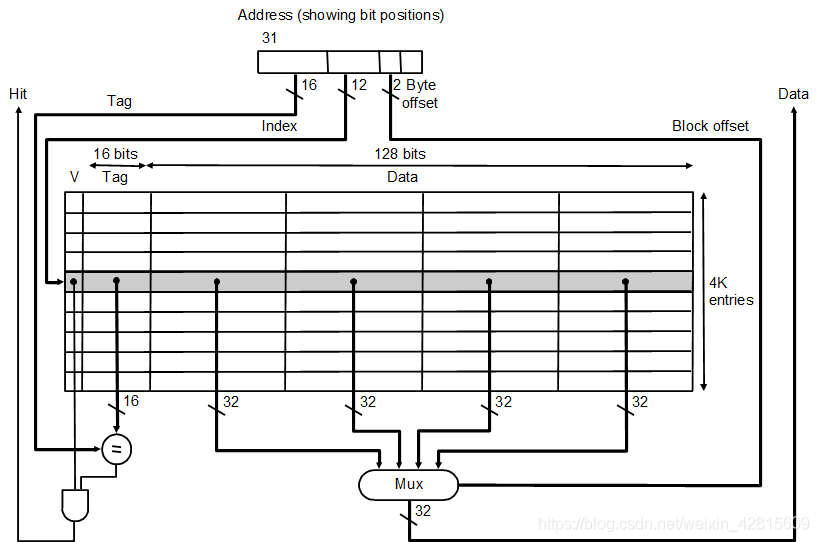

直接對映方式

如上,從多對多的關係,變成一對多的關係,

主記憶體儲器的各區域的第 1 塊只能到 Cahce 的第 1 行/塊裏面去。

因此,主記憶體地址還需要多一個索引,用於說明:這一塊在 Cache 行裡的第幾行(上圖中的紅線還是藍線)。

因此,存取過程爲:

- 比較器只有一個,進行一次比較;

- 比較誰呢?

看索引,索引點明瞭 Cache 中的第幾行要用來比較; - 如果相等,有效位爲1,則命中。

計算與舉例

主記憶體:4GB

Cache:4KB

塊大小:4B

直接對映的標記位數? 索引位數?

4GB 記憶體,地址需要 32 位表達;

Cache 有 4KB ,每塊 4B ,則有 1k 塊。

由 1k 的,索引應該有 10 位。

一塊有 4B,塊內地址用 2 位表達;

其他的位都是用來做標記的。

因此,標記位數爲 32-2-10=20 。

硬體實現比較簡潔,只有一個比較器。

Cache 舉例

8 塊 cache ,每塊 16 位元組,「直接對映」:記憶體中的每個單元在Cache中只會有一個唯一的位置和它對應。

假定有如下存取操作:

Read location 0

Read location 16

Read location 32

Read location 4

Read location 8

Read location 36

Read location 32

Read location 128

Read location 148

cache中命中和缺失各有多少次?缺失的操作如下:

Read location 0

Read location 16

Read location 32

Read location 128 (並且把 0-15 從第一塊替換)

Read location 148 (並且把 16-31 從第一塊替換)

命中率 = 4/9 = 45%

失效的原因:

- 啓動失效

- 衝突失效

直接對映 Cache: 硬體實現

增加塊大小可以更好地利用空間區域性性。

特點

- 主記憶體的字塊只可以和固定的 Cache 字塊對應,方式直接,利用率低。

- 標誌位較短,比較電路的成本低。如果主記憶體空間有 2m 塊,Cache中字塊有 2c 塊,則標誌位只要有 m-c 位。

且僅需要比較一次。

但是缺點是:利用率低,命中率低,效率較低。

小結

靜態記憶體:

- 儲存速度快

- 整合度低,容量小

- 成本高

Cache:

- 在CPU和主記憶體儲器之間設定

- 提高存取記憶體的速度

- Cache和主記憶體地址對映方式

-

- 全相聯

-

- 直接對映

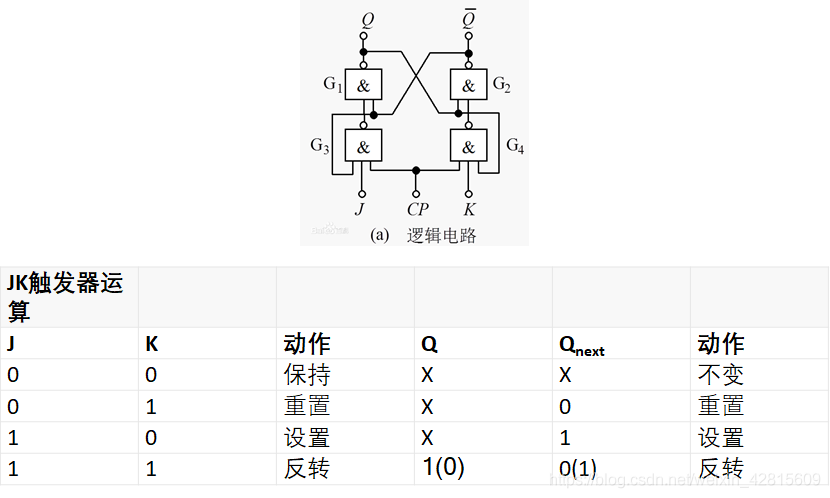

JK觸發器運算

T觸發器是在數位電路中,凡在CP時鐘脈衝控制下,根據輸入信號T取值的不同,具有保持和翻轉功能的電路,即當T=0時能保持狀態不變,T=1時一定翻轉的電路。