【Computer Organization筆記19】層次記憶體系統概述及動態記憶體

本次筆記內容:

P37 計算機組成原理(37)

P38 計算機組成原理(38)

我的計組筆記彙總:計算機組原理成筆記

視訊地址:計算機組成原理 清華大學劉衛東 全58講 國家精品課程 1080P 更完

幻燈片見我的 GitHub 倉庫:計算機組成原理 src/slides

本節課幻燈片:組成原理31 dram.pptx

本節課進入第三單元。

文章目錄

本單元內容提要

- 第一講 層次記憶體系統概述及動態記憶體

- 第二講 靜態記憶體及高速緩衝記憶體

- 第三講 高速緩衝記憶體的組成與執行原理

- 第四講 虛擬記憶體的執行原理

- 第五講 磁表面儲存裝置的儲存原理與組成

- 第六講 MIPS系統例外處理和響應

與 13 年的課不同的是,19年課程中去掉了「光碟」的部分,用 MIPS 取而代之。

控制器那單元不太好出題,因此用大實驗替代;本單元與操作系統聯繫緊密,適於出題。

本講概要

- 記憶體系統功能

- 記憶體系統的設計目標

- 需要解決的問題

- 層次記憶體系統

- 動態記憶體的組成與原理

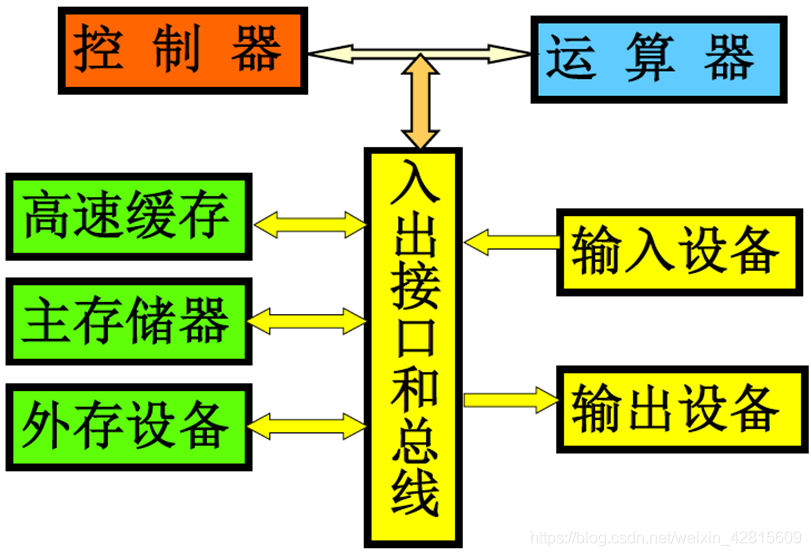

計算機硬體系統

記憶體地位和作用

- 儲存程序使計算機走向通用。

- 計算機中用來存放程式和數據的部件,是Von Neumann結構計算機的重要組成,是計算機的

中心。 - 程式和數據的特點:

-

- 源程式、彙編程式、機器語言程式

-

- 各種型別的數據

-

共同點:二進制數據

對儲存媒介的基本要求

- 能夠

有兩個穩定狀態來表示二進制中的「0」和「1」 - 容易識別

- 兩個狀態能方便地進行轉換

- 幾種常用的儲存方式:

磁顆粒、半導體(電平/電容)、光

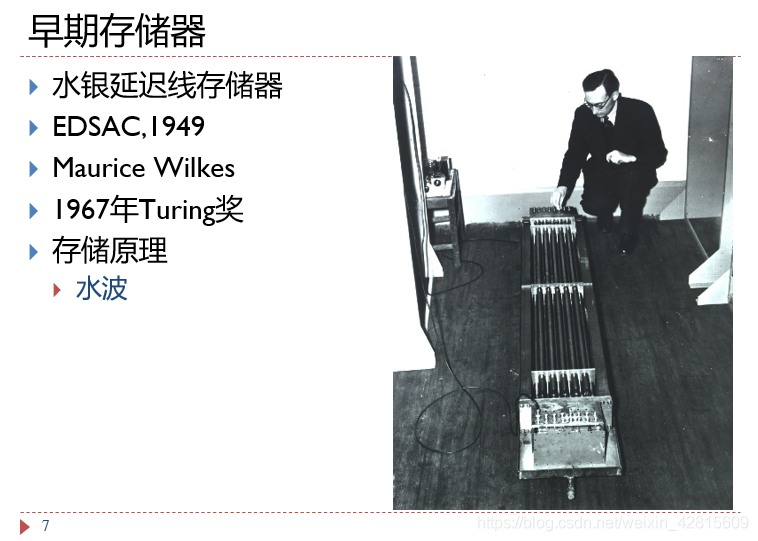

早期記憶體:水銀延遲線記憶體

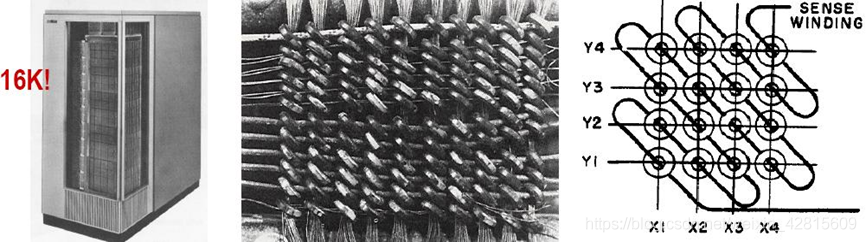

磁芯記憶體

- 圓柱型陶瓷上塗磁粉

- 手工穿線,水手結

- 消磁後重寫

這個記憶體在歷史舞臺呆了很久。發明者是華裔王安。

需要很大人工。

半導體記憶體

儲存原理:

- MOS管寄生電容

- 觸發器

存取機制 機製:

- 隨機存取(所謂隨機存取,是存取地址與讀取時間沒關係)

分類:

- ROM、RAM

- SRAM、DRAM

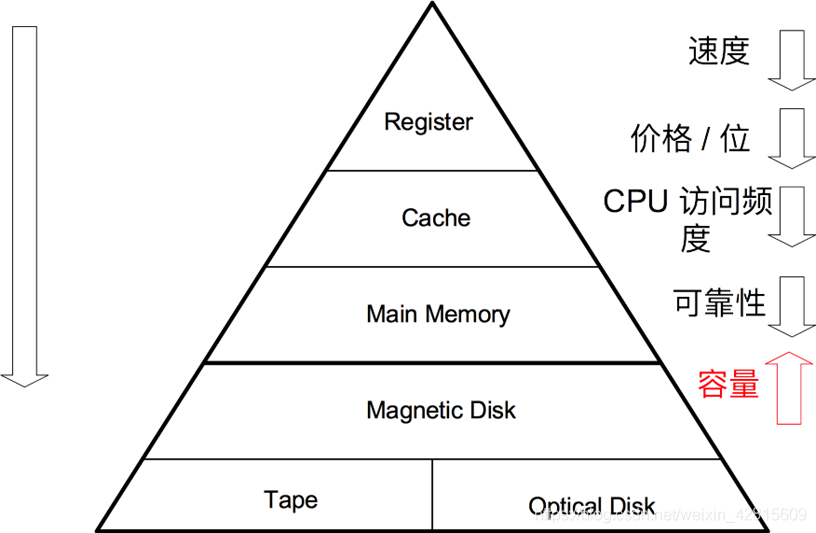

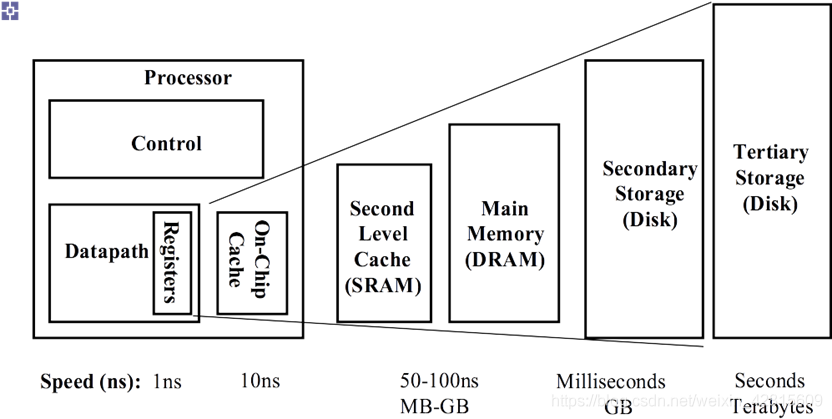

現代計算機記憶體系統

主記憶體儲器:

- 暫存器 Register

- 快取記憶體 Cache

- 主記憶體儲器 Main Memory

輔助記憶體:

- 磁碟 Disk

- 磁帶 Tape

- 光碟 Compact Disc

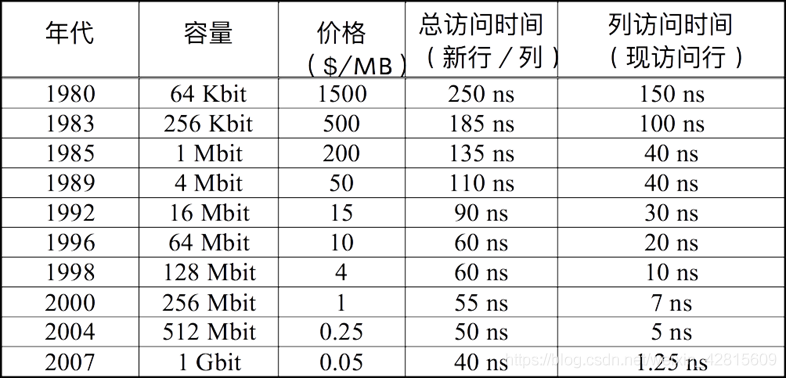

不同類型記憶體比較

按存取方式分類

隨機存取記憶體(RAM):

- 存取時間與存放位置無關

- 半導體記憶體

順序存取記憶體(SAM):

- 按照儲存位置依次存取

- 磁帶記憶體

直接存取記憶體(DAM):

- 隨機+順序

- 磁碟記憶體

關聯存取記憶體(CAM):

- 根據內容存取

- Cache和TLB

記憶體系統設計目標

- 儘可能快的

存取速度:應能基本滿足CPU對數據的存取要求 - 儘可能大的儲存

空間:可以滿足程式對儲存空間的要求 - 儘可能低的

單位成本(價格/位):使用者能夠承受的範圍內 - 較高的

可靠性

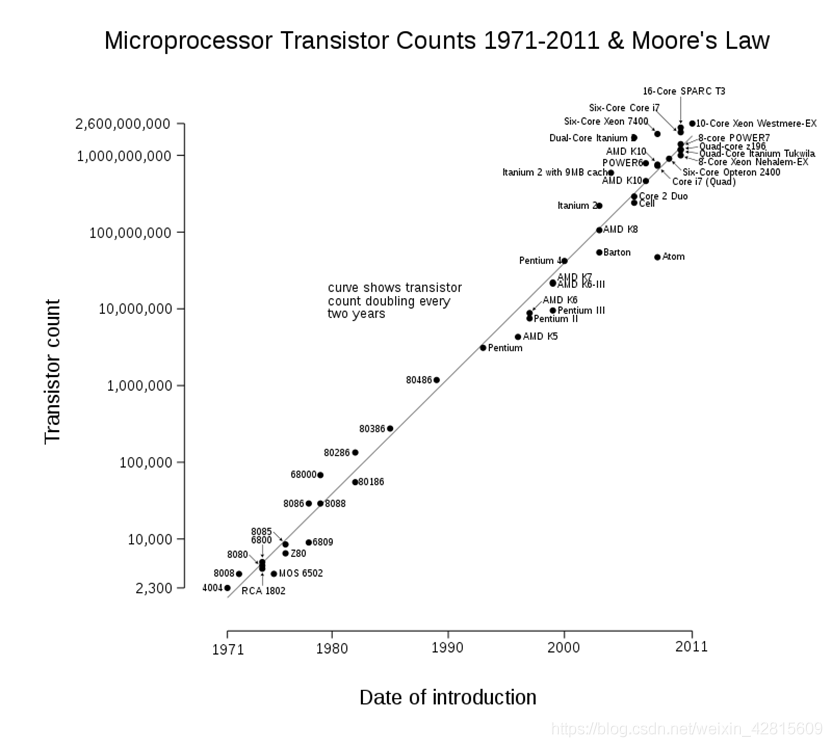

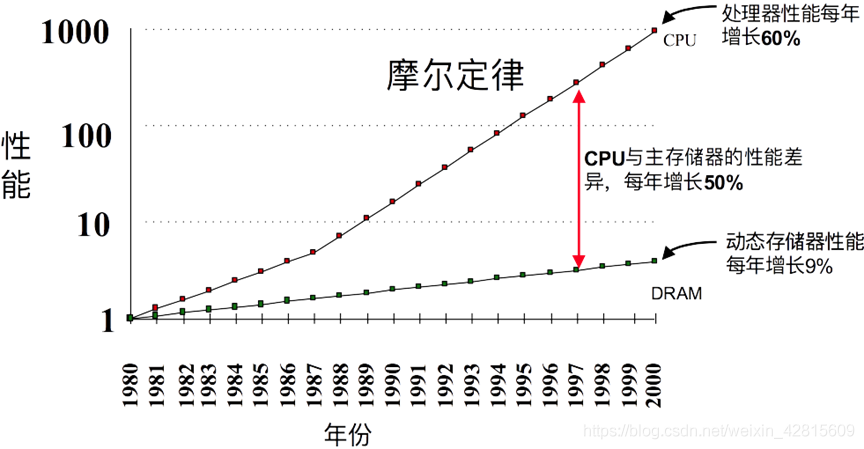

摩爾定律

1965年,Intel公司創始人之一Gordon Moore提出:晶片上整合的電晶體數量每18個月翻一番。

記憶體對效能的影響

假定某台計算機的處理器工作在:

- 主頻= 1GHz (機器週期爲1 ns)

- CPI = 1.1

- 50% 算邏指令, 30% 存取指令, 20% 轉移指令

再假定其中 10% 的存取指令會發生數據缺失,需要50個週期的延遲:

- CPI = 理想CPI + 每條指令的平均延遲 = 1.1 + (0.30 x 0.10 x 50)= 1.1 cycle + 1.5 cycle = 2. 6 CPI!

- 也就是說,

處理器 58% 的時間花在等待記憶體給出數據上面! 每1% 的指令的數據缺失將給CPI附加0.5個週期!

記憶體設計目標

目標:大容量、高速度、低成本、高可靠性

目前現實:

- 大容量記憶體速度慢

- 快速記憶體容量小

如何實現我們的目標呢?

- 層次記憶體系統

層次記憶體系統

高速度:

- 靜態記憶體速度高

- 設定較小容量的高速緩衝記憶體

大容量:

- 動態記憶體價格適中,速度適中

- 可作爲主記憶體儲器

低成本:

- 磁碟記憶體價格低廉

- 作爲輔助記憶體,暫存CPU存取頻率不高的數據和程式

- 作爲虛擬記憶體的載體

程式執行的區域性性原理

程式執行時的區域性性原理表現在:

- 在一小段

時間內,最近被存取過的程式和數據很可能再次被存取 - 在

空間上這些被存取的程式和數據往往集中在一小片儲存區 - 在存取

順序上,指令順序執行比轉移執行的可能性大(大約5:1)

合理地把程式和數據分配在不同儲存媒介中。

有了區域性性原理,我們的層次記憶體就有了依據。

層次之間應滿足的原則

(1)一致性原則:處在不同層次記憶體中的同一個資訊應保持相同的值。

(2)包含性原則:處在內層的資訊一定被包含在其外層的記憶體中,反之則不成立,即內層記憶體中的全部資訊,是其相鄰外層記憶體中一部分資訊的複製品。

這就是層次記憶體基本原理

利用程式的區域性性原理:

- 以最低廉的價格提供儘可能大的儲存空間

- 以最快速的技術實現高速儲存存取

並行技術

主記憶體的一體多字:

- 一個讀寫體,每次多個字

單字多體:

- 多個讀寫體,交叉編址

多埠記憶體

主記憶體儲器的作用和連線

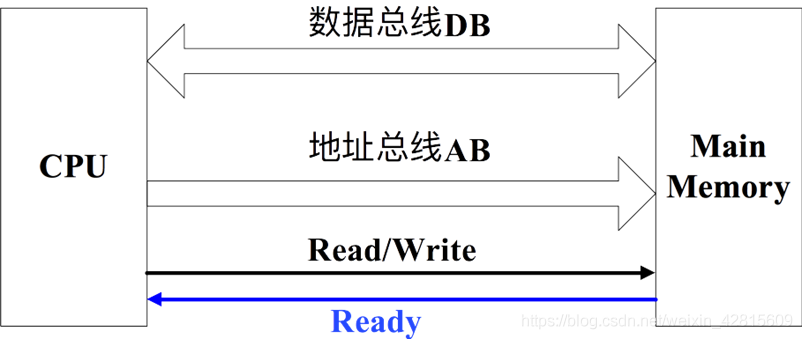

儲存正處在執行中的程式和數據(或一部分) 的部件,通過地址數據控制三類匯流排與CPU、與其它部件連通。

地址匯流排

地址匯流排用於選擇主記憶體儲器的一個儲存單元(字或位元組),其位數決定了能夠存取的儲存單元的最大數目,稱爲最大可定址空間。例如,當按位元組定址時,20位的地址可以存取1MB的儲存空間,32位元的地址可以存取4GB的儲存空間。

數據總線

數據總線用於在計算機各功能部件之間傳送數據,數據總線的位數(匯流排的寬度)與匯流排時鐘頻率的乘積,與該匯流排所支援的最高數據吞吐(輸入/輸出)能力成正比。

控制匯流排

控制匯流排用於傳「控制信號」並不準確。

控制匯流排用於指明匯流排的工作週期型別和本次入/出完成的時刻。匯流排的工作週期可以包括主記憶體儲器讀週期、主記憶體儲器寫週期、I/O裝置讀週期、I/O裝置寫週期,即用不同的匯流排週期來區分要用哪個部件(主記憶體或I/O裝置)和操作的性質(讀或寫);還有直接記憶體存取(DMA)匯流排週期等。

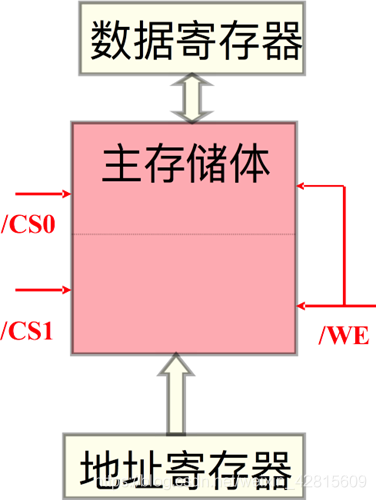

主記憶體儲器的讀寫過程

讀過程:

- 給出地址

- 給出片選與讀命令

- 儲存讀出內容

寫過程:

- 給出地址

- 給出片選與數據

- 給出寫命令

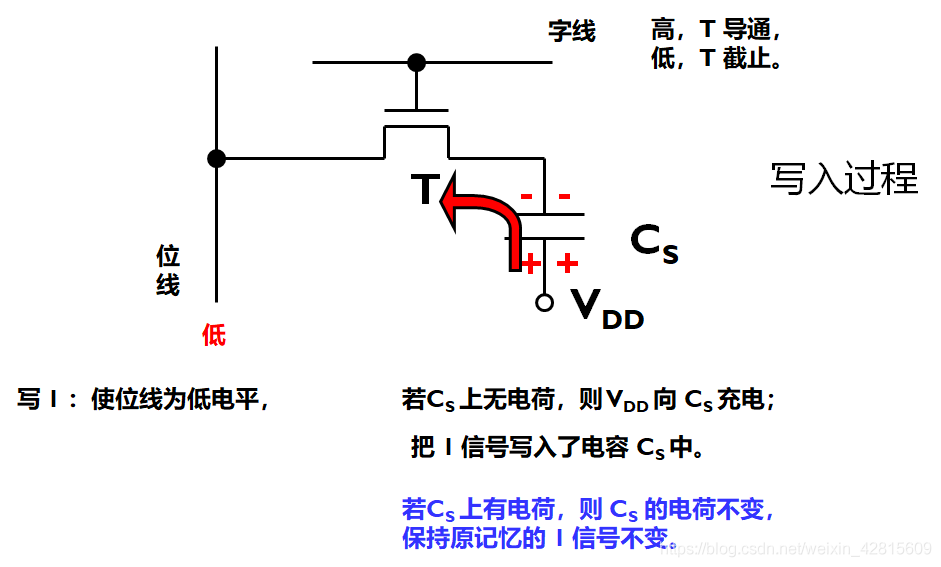

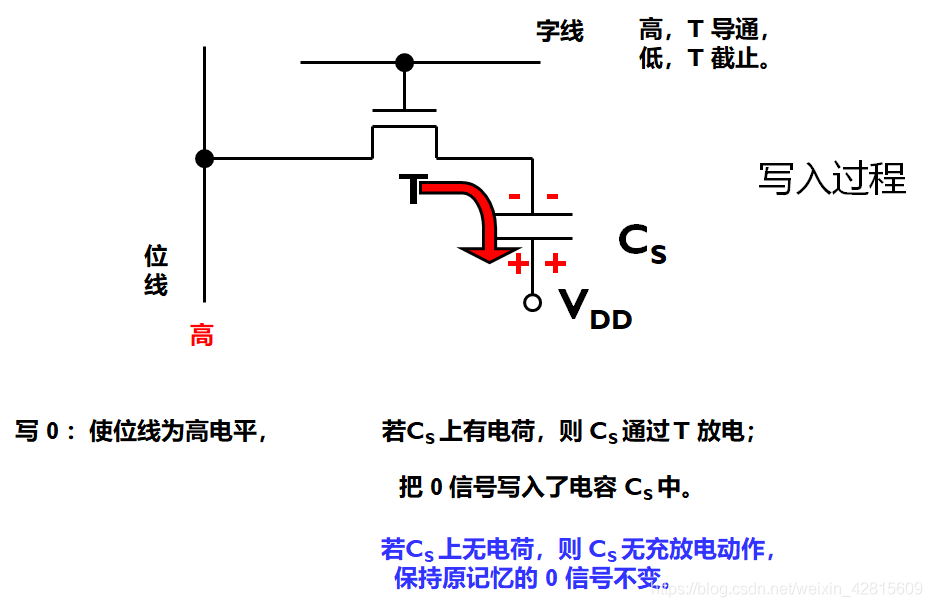

動態記憶體的儲存原理

動態記憶體,是用金氧半導體(MOS)的單個MOS管來儲存一個二進制位(bit)資訊的。資訊被儲存在MOS管T的源極的寄生電容CS中,例如,用CS中儲存有電荷表示1,無電荷表示0。

動態記憶體的寫過程

是電源。

寫 1

若CS 上有電荷,則 CS 的電荷不變,保持原記憶的 1 信號不變;

若CS 上有電荷,則 CS 的電荷不變,保持原有的內容 1 不變。

寫 0

若CS 上無電荷,則 CS 無充放電動作,保持原記憶的 0 信號不變。

若CS 上無電荷,則 CS 無充放電動作,保持原記憶的 0 信號不變。

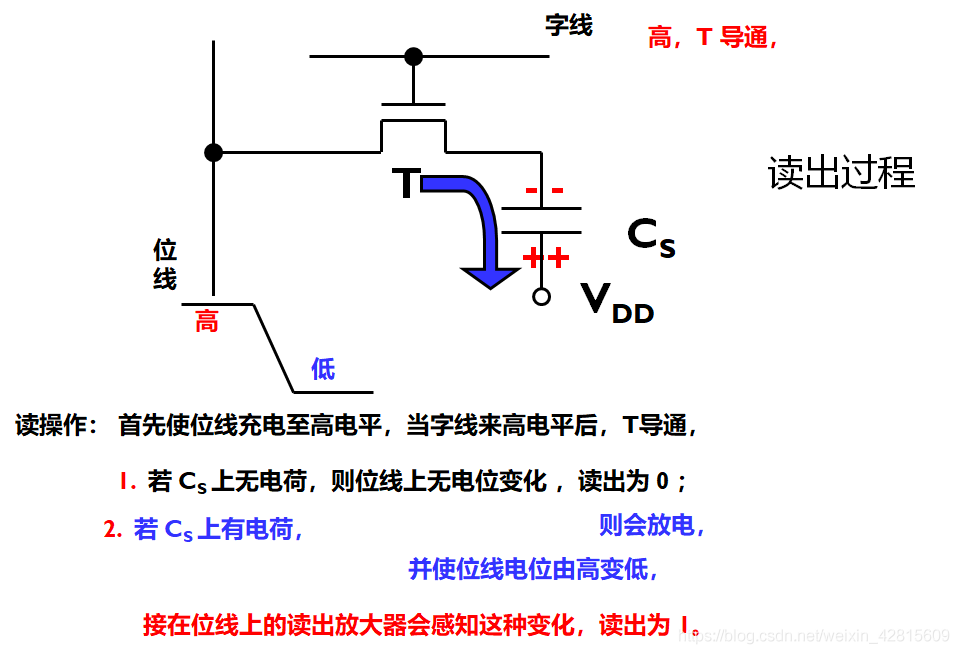

讀出過程

讀操作,首先使位線充電至高電平,當字線來高電平後,T導通:

- 若 CS 上無電荷,則位線上無電位變化 ,讀出爲 0 ;

- 若 CS 上有電荷,則會放電,並使位線電位由高變低,

接在位線上的讀出放大器會感知這種變化,讀出爲 1。

但是,有一個問題:讀了 1 ,電容電放沒了,變成 1 了。

動態記憶體的工作特點

破壞性讀出:

- 讀出時被強制清零

- 因此,預充電延遲

需定期重新整理(防止電掉光):

- 集中重新整理:停止讀寫,逐行重新整理

- 分散重新整理:定時週期性重新整理

重新整理的單位是頁,因此要做快速分頁組織。

破壞性讀出:讀操作後,被讀單元的內容一定被清爲零,必須把剛讀出的內容立即寫回去,通常稱其爲預充電延遲,它影響記憶體的工作頻率,在結束預充電前不能開始下一次讀。

要定期重新整理:在不進行讀寫操作時,DRAM 記憶體的各單元處於斷路狀態,由於漏電的存在,儲存在電容CS 上的電荷會慢慢地漏掉,爲此必須定時予以補充,通常稱其爲重新整理操作。

重新整理不是按字處理,而是每次重新整理一行,即爲連線在同一行上所有儲存單元的電容補充一次能量。 重新整理有兩種常用方式:①集中重新整理,停止記憶體讀寫操作,逐行將所有各行重新整理一遍;②分散重新整理,每一次記憶體讀寫後,重新整理一行,各行輪流進行。或在規定的期間內,如 2 ms ,能輪流把所有各行重新整理一遍。

快速分頁組織的記憶體:行、列地址要分兩次給出,但連續地讀寫用到相同的行地址時,也可以在前一次將行地址鎖存,之後僅送列地址,以節省送地址的時間,支援這種執行方式的被稱爲快速分頁組織的記憶體。

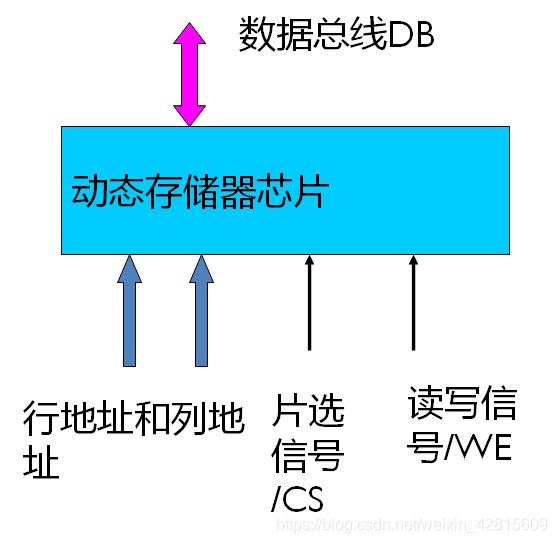

動態記憶體讀寫過程(行/列地址)

動態記憶體整合度高,儲存容量大,爲節約管腳數,地址分爲行地址和列地址。

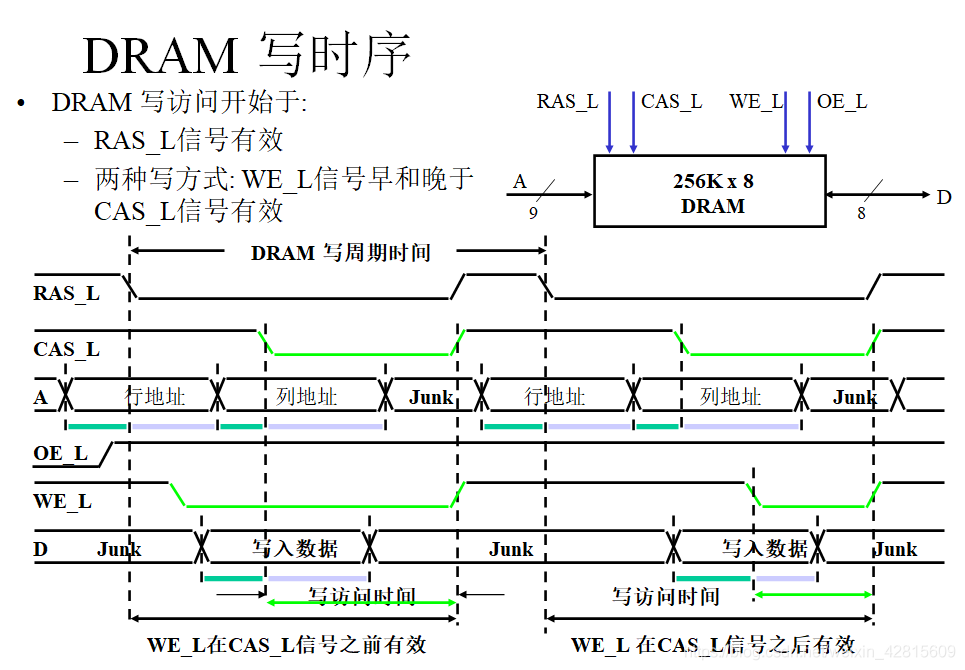

DRAM 寫時序

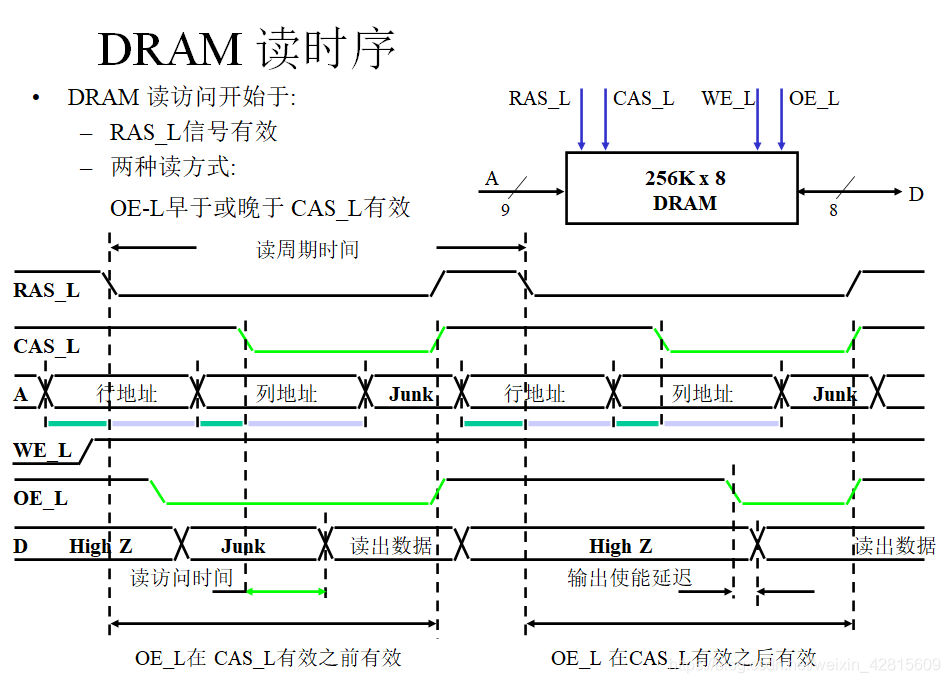

DRAM 讀時序

小結

程式的區域性性原理:

- 時間區域性性:最近被存取過的程式和數據很可能再次被存取

- 空間區域性性:CPU很可能存取最近被存取過的地址單元附近的地址單元。

利用程式的區域性性原理:

- 使用盡可能大容量的廉價、低速記憶體存放程式和數據。

- 使用高速記憶體來滿足CPU對速度的要求。

動態記憶體DRAM:

- 電容充放電來儲存數據

- 整合度高、容量大、能耗低、速度慢