Quartus 入門

2023-10-27 06:01:18

轉載請標明出處:https://www.cnblogs.com/leedsgarden/p/17790320.html

本文介紹的是Quartus的免費版,可以滿足基本的教學需要

如果你用的是Xilinx的話,這篇文章不適合你。本文適用於Altera使用者

下載安裝

在 Lite Edition 一欄,選擇你的發行版,點選下載。

(下載可能比較慢,有條件可以掛代理)

下載後解壓,雙擊Setup安裝。

基本預設選項即可,會把幫助選單和器件庫全部安裝完成。

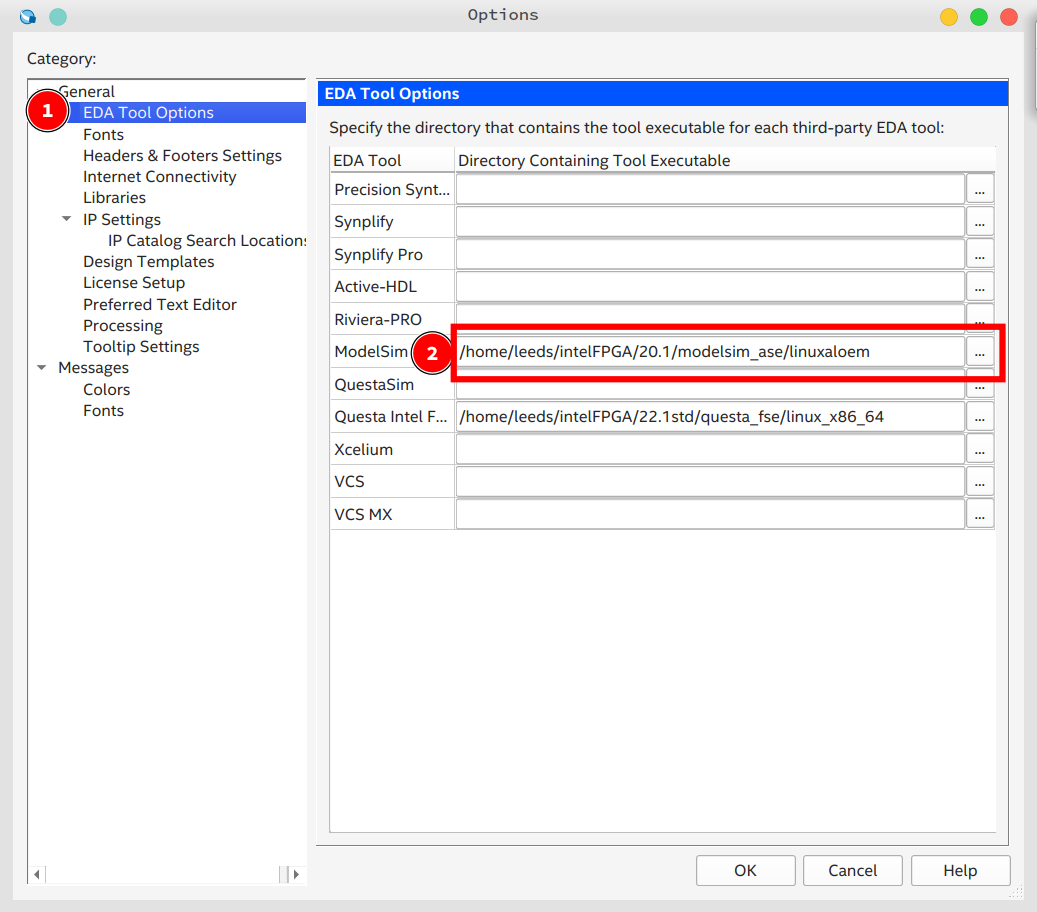

聯合ModelSim模擬

安裝完成後,開啟 Quartus,在Tools->Options...開啟,設定路徑,最後點選OK。

範例

# windows

C:\\intelFPGA\20.1\modelsim_ase\win32aloem # 預設

# Linux

~/intelFPGA/20.1/modelsim_ase/linuxaloem # 預設

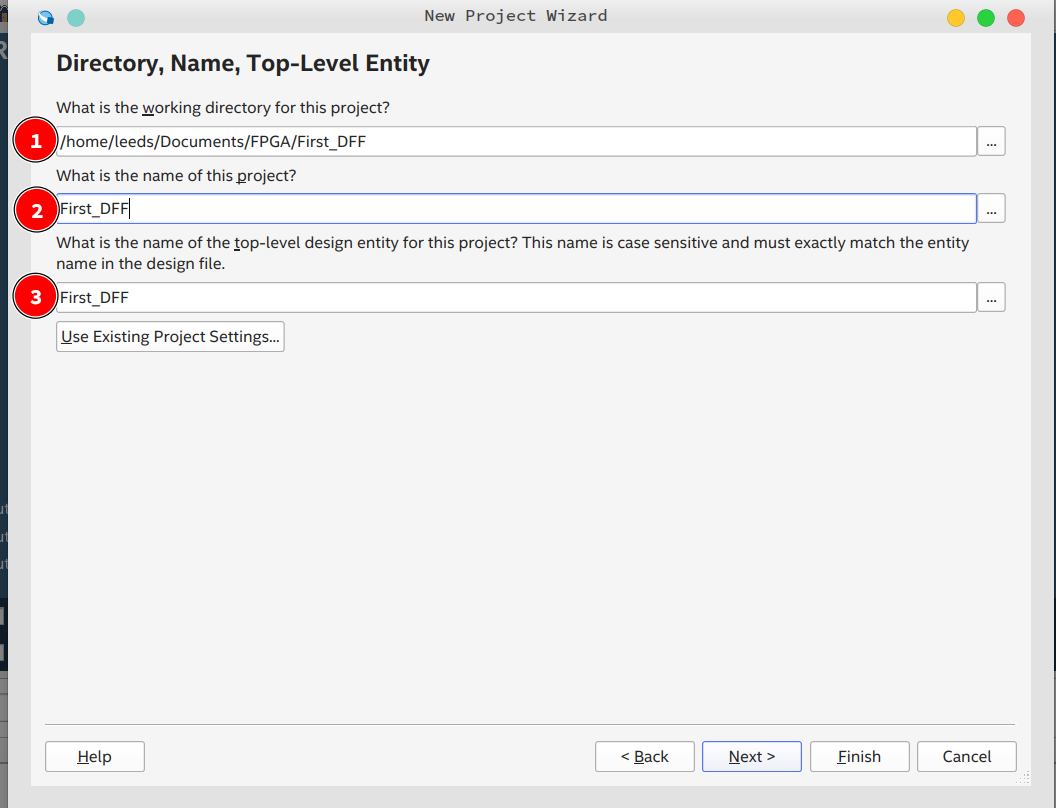

建立工程專案

第一步

或者

File->New Project Wizard

第二步

選擇路徑加上專案名,在第二欄輸入專案名,第三欄會自動補上。

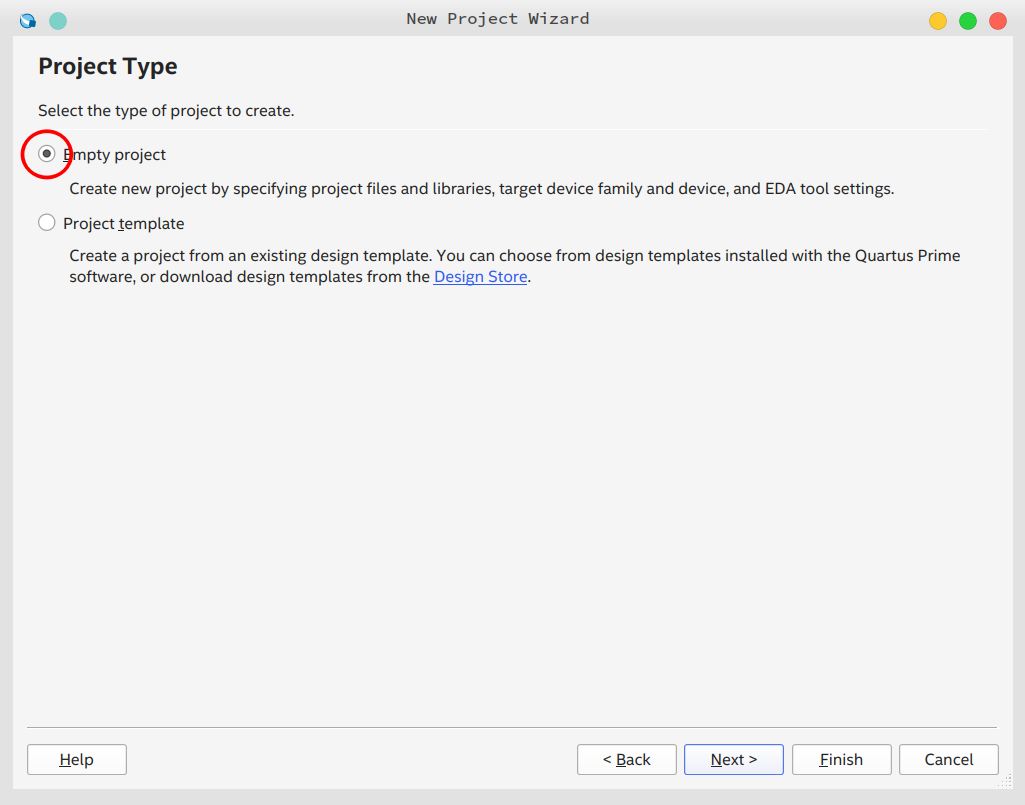

第三步

選擇空專案可

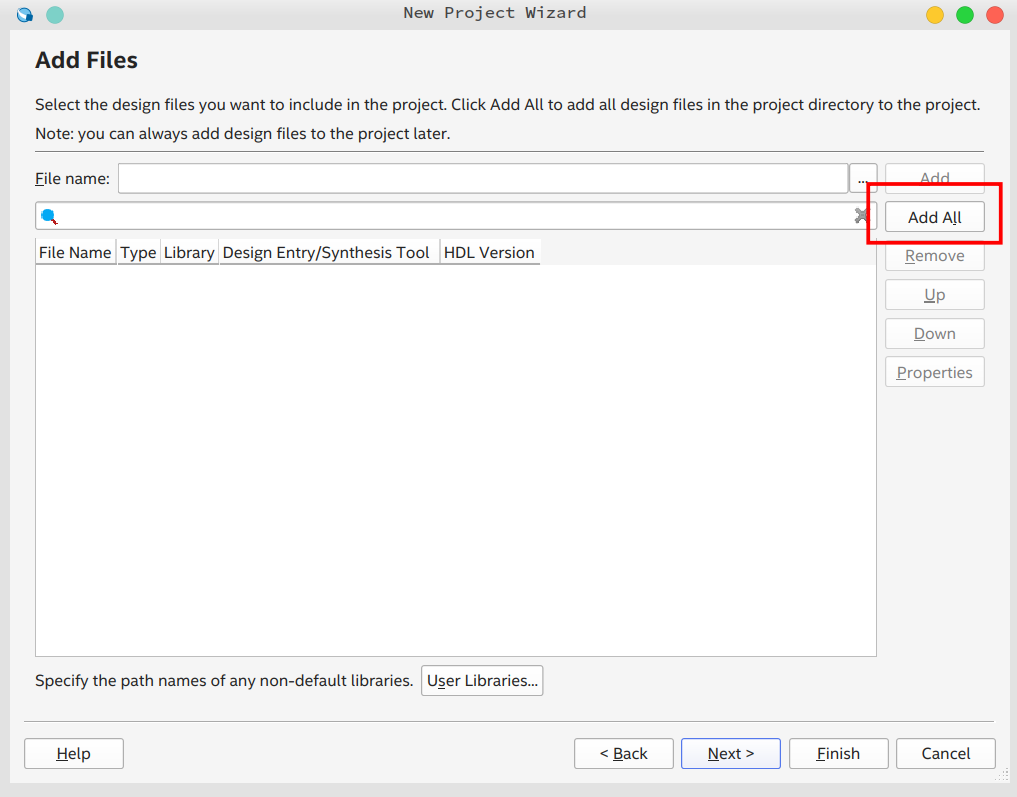

第四步

如果有檔案,Add新增即可,我們這裡跳過

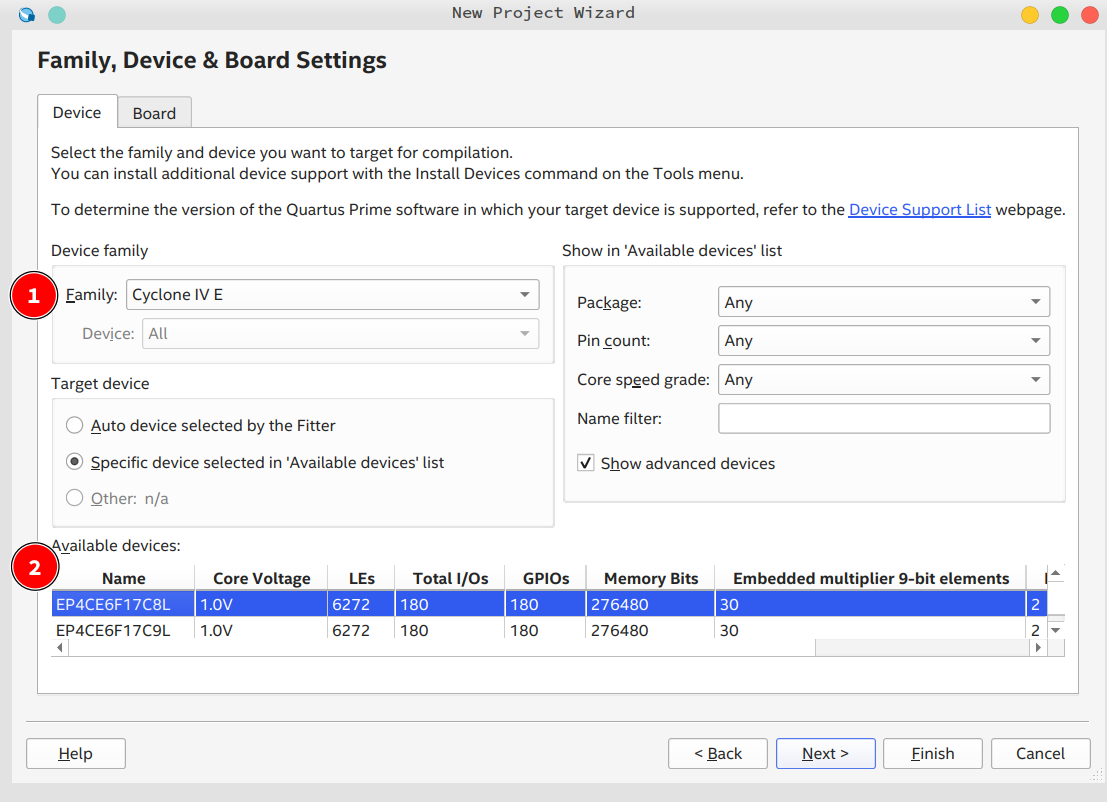

第五步

這裡按照器件選擇,範例為 Cyclone IV E EP4CE6F17C8L。

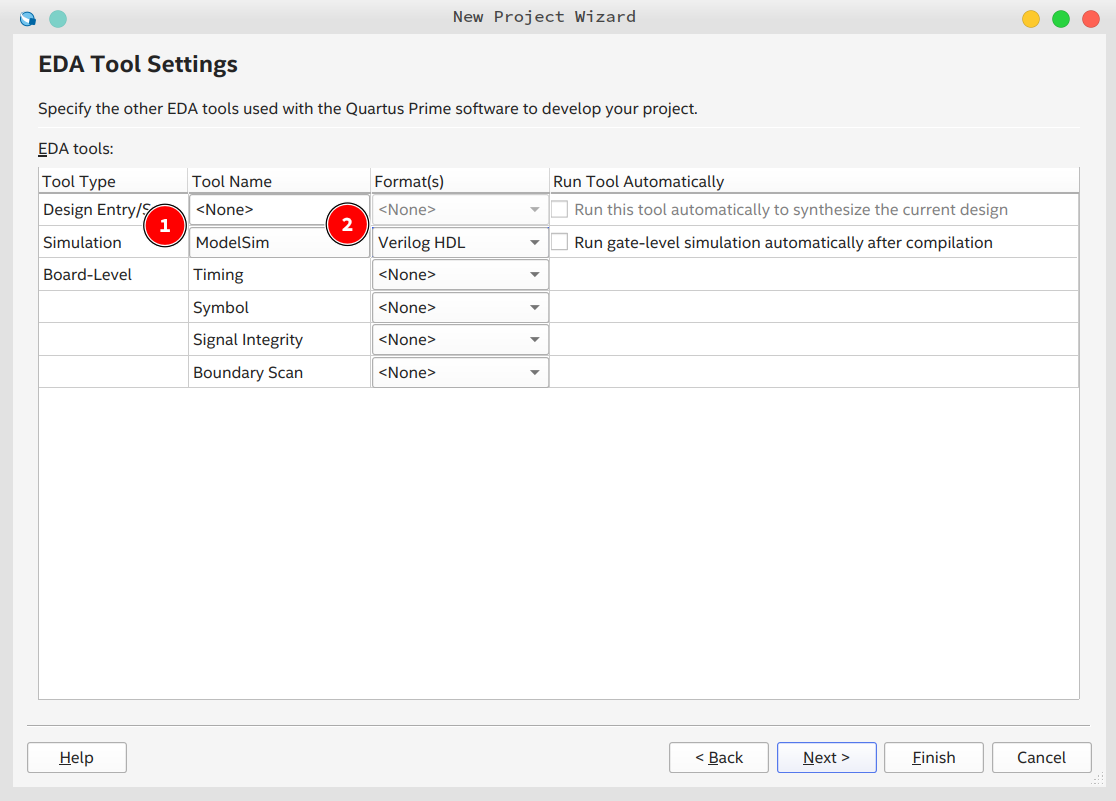

第六步

按照範例把1更改為ModelSim,2更改為Verilog HDL。

第七步

再次確認資訊是否正確,點選Finish。

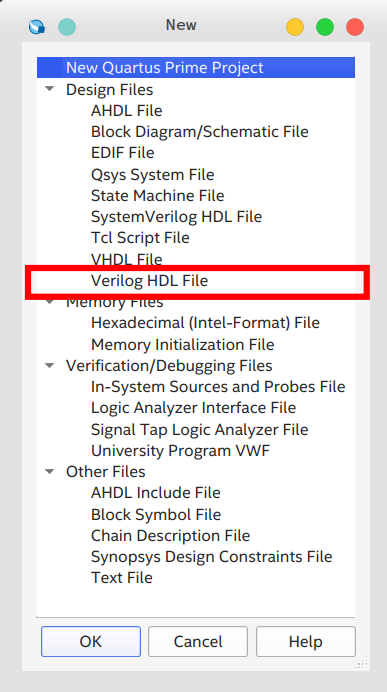

新增 verilog 檔案

File->New...

輸入模組程式碼,然後用同樣的方式建立testbench。

// First_DFF.v

module First_DFF(D, CLK, Q);

input D, CLK;

output Q;

reg Q;

always @(posedge CLK)

begin

Q <= D;

end

endmodule

// First_DFF_tb.v

`timescale 1ns / 10ps

module First_DFF_tb;

reg clk;

reg D;

wire Q;

First_DFF DFF(

.CLK(clk),

.D(D),

.Q(Q)

);

always #10 clk = ~clk;

initial begin

clk = 1'b0;

D = 1'b0;

#20 D = 1'b1;

#20 D = 1'b0;

#20 D = 1'b1;

#20 $stop;

end

endmodule

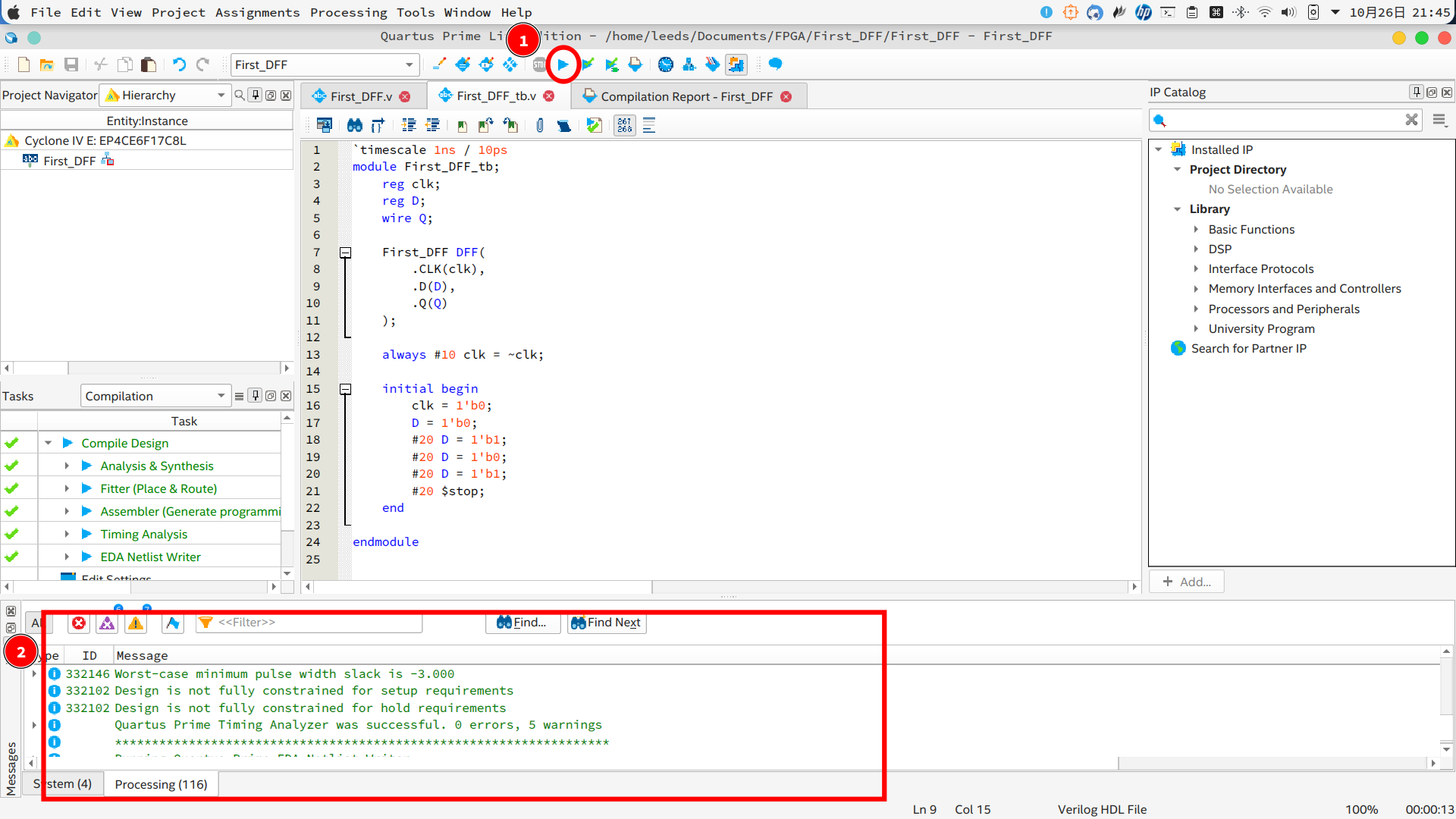

編譯並通過

選擇 testbench

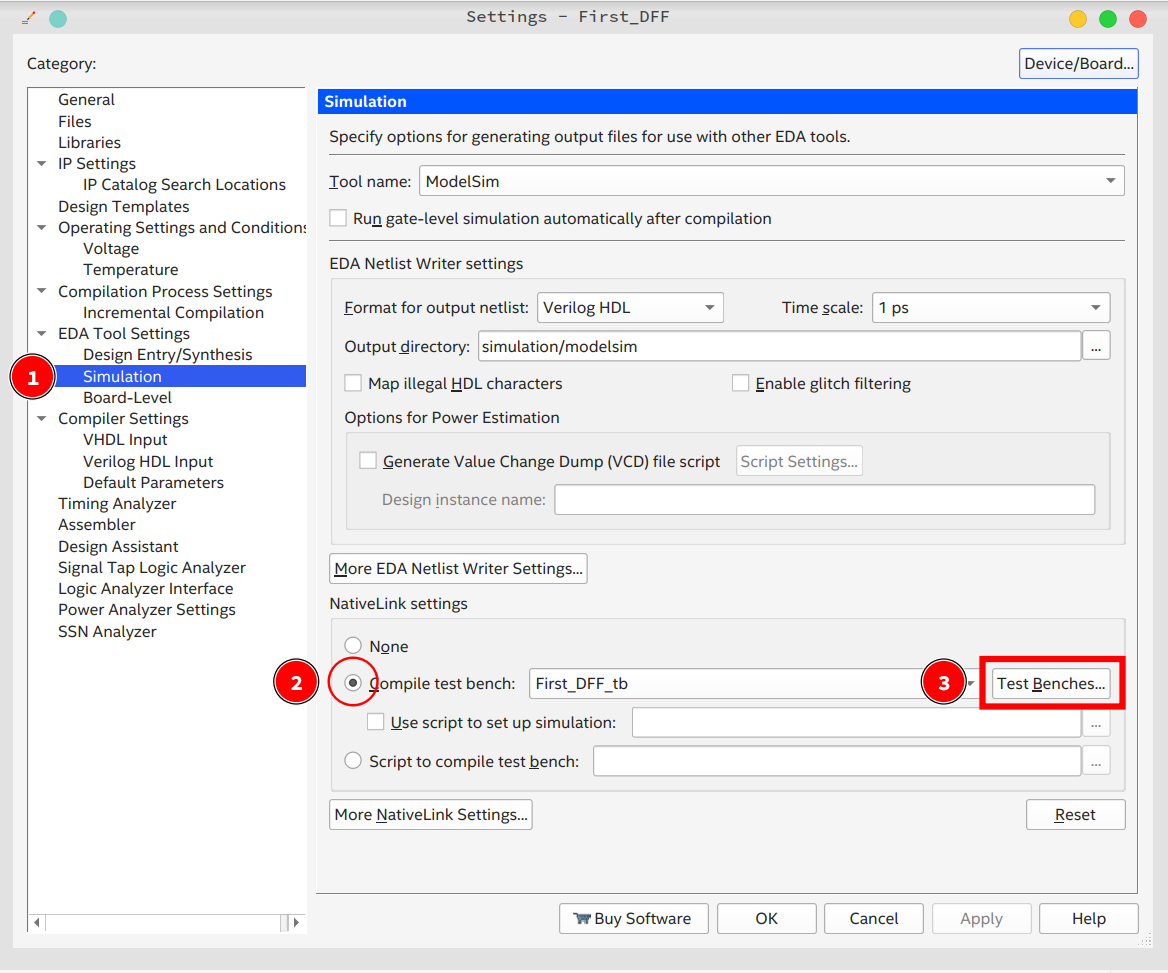

Assignment->Setting...

勾選2,點選 testbench

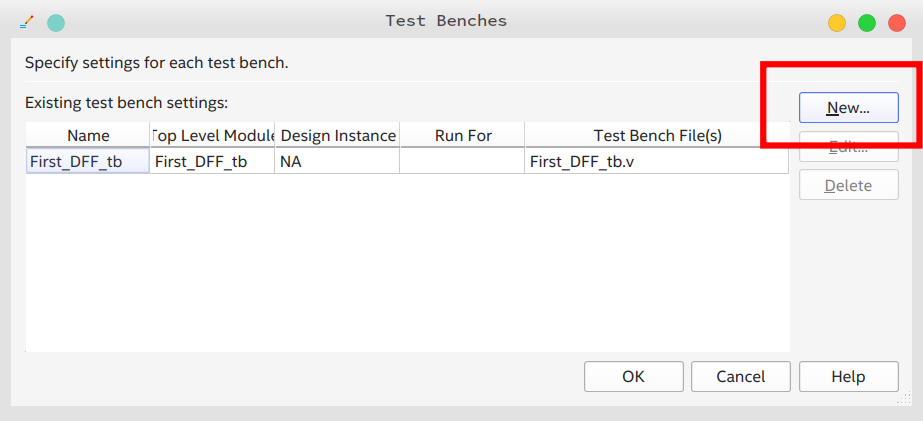

點選New。(表格空白不要慌,我的是已經新增好了的)

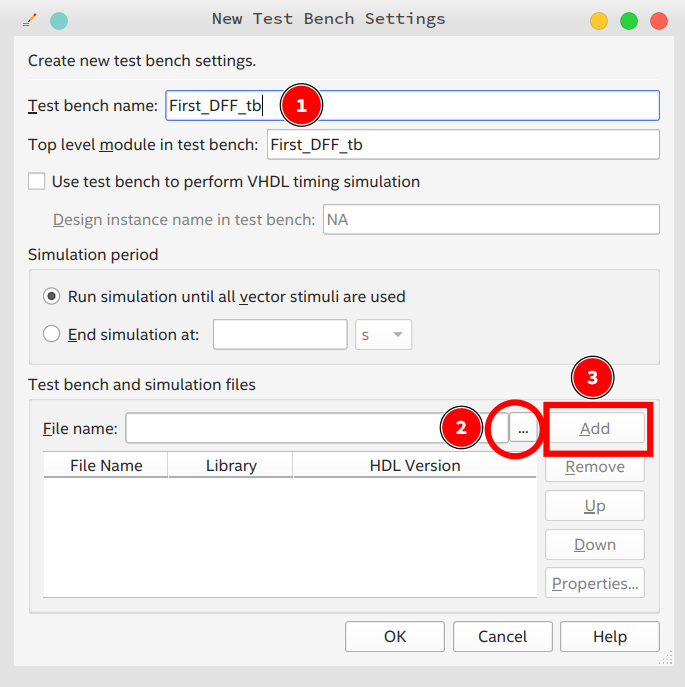

在1輸入testbench檔名,2中選擇檔案,點選Add新增即可。

然後一路 OK 回到主介面。

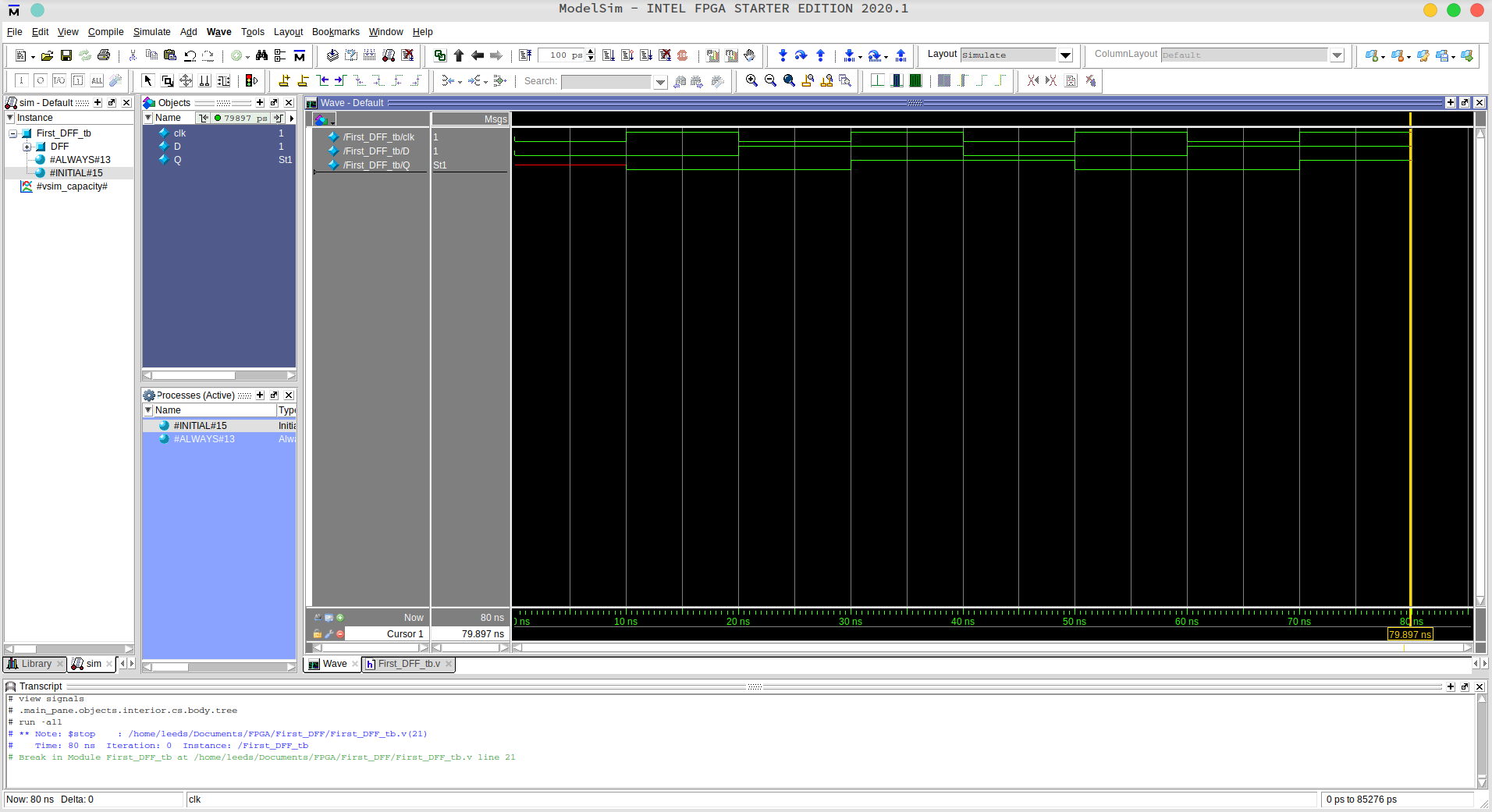

ModelSim 模擬

Tools->Run Simulation Tool->RTL Simulation

彈出 ModelSim 就算成功。