揭祕計算機內部通訊:探祕資料、地址與控制訊號的奧祕

引言

在我們前面的講解中,我們詳細瞭解了計算機系統的核心元件,包括CPU、記憶體和磁碟。然而,匯流排在這個體系中同樣至關重要。匯流排是計算機內部各部件間通訊的橋樑,涉及資料、地址和控制訊號的傳輸。在接下來的內容中,我們將深入探討各種型別的匯流排,為你解析計算機系統的關鍵組成部分。

匯流排

計算機是由五大部件組成的,包括運算器、記憶體、控制器、輸入裝置和輸出裝置。這個概念可能有些抽象,簡單來說就是CPU包含運算器和控制器,記憶體指的是記憶體,而輸入輸出裝置分別指的是鍵盤和顯示器。這幾個部件之間需要共同共同作業完成資訊處理,而它們之間的通訊是通過匯流排來實現的。

在現代的Intel CPU體系結構中,通常有多條匯流排。首先,CPU和記憶體以及快取記憶體之間有兩種匯流排。這種方式被稱為雙獨立匯流排(Dual Independent Bus,DIB)。CPU內部有一個快速的本地匯流排(Local Bus),用於和快取記憶體通訊;還有一個速度相對較慢的前端匯流排(Front-side Bus),用於和主記憶體以及輸入輸出裝置通訊。

在前面的幾講中,我們已經講過,現代的CPU通常配備專門的快取記憶體晶片。本地匯流排用於與快取記憶體通訊,而前端匯流排用於與主記憶體以及輸入輸出裝置通訊。有時候,本地匯流排也被稱為後端匯流排(Back-side Bus),與前端匯流排相對應。前端匯流排還有其他名稱,比如處理器匯流排(Processor Bus)、記憶體匯流排(Memory Bus)。

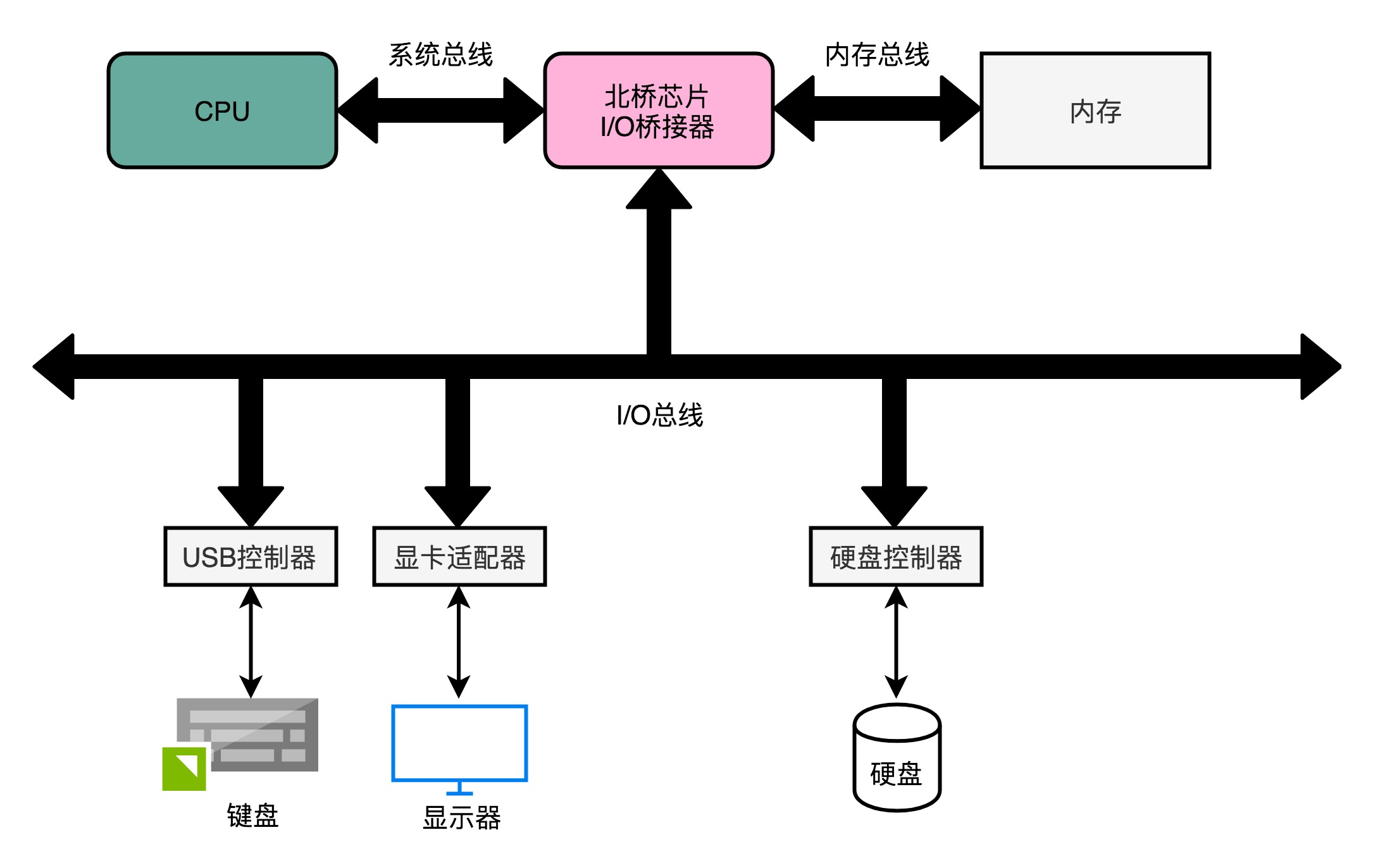

在計算機硬體體系結構中,除了常見的前端匯流排,我們還經常聽到 PCI 匯流排、I/O 匯流排以及系統匯流排(System Bus)等術語。這些匯流排的命名常常讓人感到混淆,容易讓人迷失在技術術語的海洋中。然而,如果我們直接檢視CPU的硬體架構圖,就能一目瞭然地解決所有困擾。

在CPU內部,北橋晶片起到了關鍵作用,將前端匯流排一分為二,形成了三個獨立的匯流排。實際上,前端匯流排就是系統匯流排的一部分。CPU內部的記憶體介面直接與系統匯流排通訊,而系統匯流排再連線到一個I/O橋接器(I/O Bridge)。這個I/O橋接器一側連線了記憶體匯流排,使得CPU能夠與記憶體進行高效通訊;另一側則連線了一個獨立的I/O匯流排,用於連線各種輸入輸出裝置。

事實上,在真實的電腦架構中,匯流排層面的劃分更為精細。根據不同的裝置型別,還會有獨立的PCI匯流排、ISA匯流排等等,這些匯流排的存在進一步豐富了計算機硬體架構,使得不同型別的裝置能夠在計算機系統內部高效協同工作。

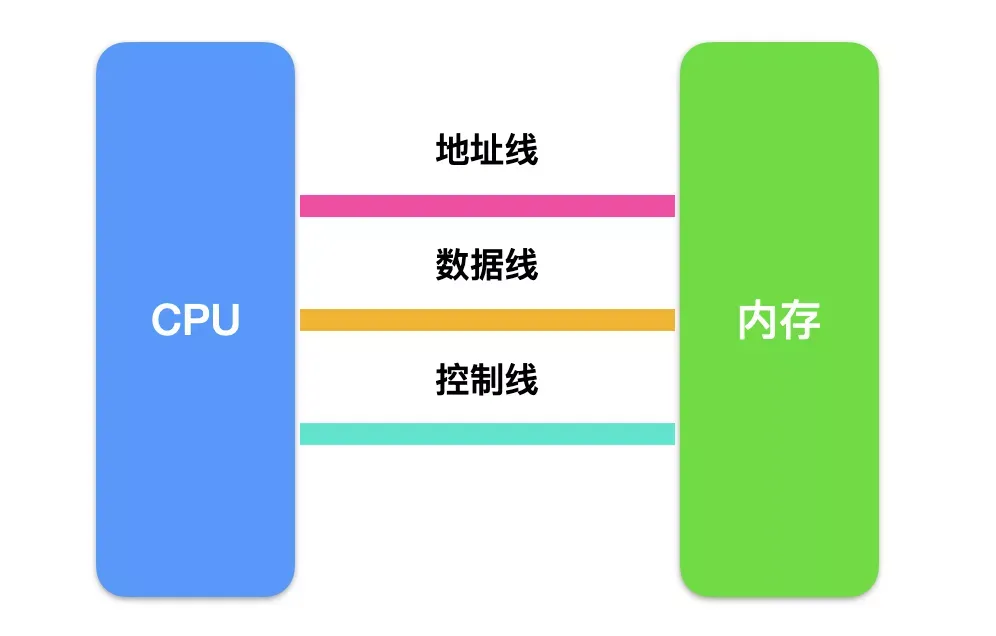

在物理層面,我們可以將計算機匯流排視為一組關鍵的「電線」,這些電線在計算機硬體體系結構中扮演著至關重要的角色。這些電線並非簡單的電子連線,而是精密地分工合作,通常分為三大類線路,每一類線路都有其獨特的功能和任務,構成了計算機內部資訊傳遞的基礎架構。

首先,我們有傳輸線(Data Bus),它負責傳輸實際的資料資訊,可以將其類比為公交車上的「乘客」。這些傳輸線承載著計算機內部各種資訊,使得資料能夠在不同元件之間流動,實現了計算機內部的資訊傳遞和交換。

其次,地址線(Address Bus)起到了一個非常關鍵的作用,它確定了資料傳輸的目的地,就像是為「乘客」寫下上車和下車的站點資訊的紙條。地址線告訴計算機系統資料應該被送往記憶體的哪個具體位置,或者是某個特定I/O裝置的哪個暫存器,從而確保資料能夠準確地被儲存或者被讀取。

最後,控制線(Control Bus)扮演著監管和排程的角色,類似於公交車的「司機」。這些控制線傳遞控制訊號,指示何時讀取或寫入資料,何時進行記憶體或I/O裝置的存取,確保計算機內部各個部件的協調運作。它們是計算機匯流排系統的指揮官,負責確保所有操作在正確的時間和順序下進行。

在計算機系統中,地址匯流排具有關鍵的作用,主要用於傳輸源資料或目的資料在主記憶體單元中的位置資訊。CPU利用地址匯流排來明確指定儲存單元的位置。地址匯流排的寬度決定了它能傳送的資訊量,也就是CPU可以定址的儲存單元數量。

和記憶體之間的資訊交換通過了10條地址匯流排。每一條地址匯流排能夠傳遞的資訊只有0或1,這意味著在一次傳遞過程中,CPU和記憶體可以進行2的10次方(即1024)次資料交換。因此,如果CPU的地址匯流排有N條,那麼我們可以說這個地址匯流排的寬度是N,這樣CPU就能夠定址2的N次方個記憶體單元。

資料匯流排

傳輸線,顧名思義,指的是一次可以傳遞的資料位數。資料匯流排的位數即為資料匯流排的寬度,它定義了一次性可以傳輸的二進位制資料的長度。在計算機系統中,CPU與記憶體以及其他硬體部件之間的資料傳送任務通常由資料匯流排來完成。資料匯流排的寬度對於計算機系統的效能和資料傳輸速度有著直接的影響。8 根資料匯流排可以一次傳送一個 8 位二進位制資料(即一個位元組)。如果資料匯流排增加到16根,那麼每次傳輸的資料長度就變成了兩個位元組。同理,32根資料匯流排可以一次傳輸四個位元組的資料,以此類推。

控制匯流排

控制匯流排,作為連線在計算機系統各個元件之間的關鍵通訊通道,承載著來自CPU的各種控制訊號。這些控制訊號在計算機的正常操作中起到了至關重要的作用,確保了各個硬體部件之間的協調執行。控制匯流排上常見的訊號包括時鐘訊號(用於同步操作)、復位訊號(用於初始化操作)、中斷請求/響應訊號、記憶體讀寫訊號、IO讀寫訊號等。

在計算機系統中,CPU與其他硬體部件之間的控制操作是通過控制匯流排來實現的。控制匯流排的寬度即為其中所包含的傳輸線數量,每一根傳輸線都承載著不同的控制訊號。因此,控制匯流排的寬度決定了CPU對外部部件的控制能力。換句話說,控制匯流排的每一根線路都代表了CPU可以傳送的一種控制訊號型別,而控制匯流排上的訊號種類多少,直接反映了CPU對外部器件進行各種操作的多樣性和複雜性。

總結

本文深入介紹了計算機系統中至關重要的匯流排概念。匯流排是計算機內部各元件間通訊的橋樑,涉及資料、地址和控制訊號的傳輸。文章解釋了不同型別的匯流排,包括傳輸線、地址線和控制線,並詳細探討了它們在CPU、記憶體和其他硬體部件之間的作用。地址匯流排的寬度決定了CPU可以定址的儲存單元數量,資料匯流排的寬度影響資料傳輸速度,而控制匯流排負責傳遞各種控制訊號,確保計算機內部各部件的協調運作。通過對匯流排系統的深入理解,讀者可以更好地瞭解計算機硬體架構,為進一步學習和研究提供了基礎。