Chiplet解決晶片技術發展瓶頸

這是IC男奮鬥史的第38篇原創

本文1776字,預計閱讀4分鐘。

Chiplet封裝是什麼

介紹Chiplet前,先說下SOC。Chiplet和SOC是兩個相互對立的概念,剛好可以用來互為參照。

SOC (System On Chip,系統級晶片)——

是指將多個負責不同型別計算任務的單元,通過光刻的形式製作到同一片晶圓上。

目前主流智慧手機的SOC晶片上,基本都整合了CPU、GPU、DSP、ISP、NPU、Modem等眾多不同功能的計算單元,以及諸多的介面IP與SRAM。

SOC追求的是「高度的整合化」,利用先進位製程對於所有的單元進行全面的提升。

Chiplet (也稱作「芯粒」或者「小晶片」)——

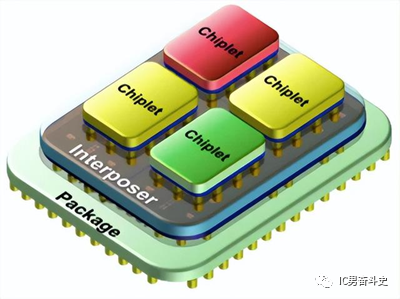

是指將一顆原本較為複雜的SOC晶片,從設計時就按照不同的功能單元進行分解,然後每個單元選擇最適合的半導體制程工藝分別進行製造,再通過先進封裝技術將各個單元彼此互聯,就像搭「樂高積木」一樣封裝為一個系統級晶片組。

目前Chiplet封裝技術已經在CPU、GPU、ASIC等高階晶片領域有所應用。隨著摩爾定律接近極限,為了提高整合度,越來越多的複雜邏輯晶片會採用chiplet封裝。

Chiplet封裝支援每個功能單元使用不同的製程工藝,從而達到效能與成本的相對最優解。

圖1 Chiplet封裝結構示意圖

Chiplet封裝的發展機遇

1 摩爾定律接近物理極限

晶圓製程工藝往3nm/2nm以下推進的難度突然飆升,幾乎已經觸碰到矽材料本身的物理極限;靠升級製程工藝來提升晶片效能的方法按照目前的科技能力已經無法再繼續下去;通過先進封裝技術(例如2.5D/3D/chiplet等)提升晶片效能並延續摩爾定律,已經逐步獲得整個半導體產業界的認可。

2 先進封裝技術取得較大突破

臺積電CoWoS 2.5D封裝技術已經日趨成熟,成為高效能運算晶片的主要選擇;全球前兩大封裝廠日月光和安靠科技在2.5D/3D封裝領域也都建立了自己的技術路線,目前也有幫客戶推出不同型別的產品;國內三大封測廠長電、通富和華天也都在先進封裝領域積極佈局,包括2.5D/3D等技術都取得了一定的發展。

3 AI應用對算力的巨大需求加速Chiplet技術發展

ChatGPT訓練需要消耗3640PFLOPS-days AI算力,AIGC領域將引領新一輪的算力需求風暴;不論是從政府層面還是企業層面,資料中心和超算中心的持續建立都需要巨大的算力支援;隨著自動駕駛技術的逐步落地,AI算力的需求還會進一步加劇。

4 美國晶片制裁政策推動Chiplet在國內的發展

2022年8月,美國政府針對3nm以下先進位製程工藝使用的EDA軟體實施出口限制;2022年9月,美國政府限制英偉達和AMD向中國出售高效能GPU晶片;2022年10月,美國政府出臺政策限制臺積電等全球晶片製造企業為中國加工製造高效能運算晶片。受限於美國製裁,國內AI晶片企業無法使用先進位製程工藝迭代來提升算力,轉而使用Chiplet等先進封裝技術來實現算力的提升與新產品的研發。

Chiplet封裝的優劣勢分析

1 優勢

1.1 提升產品良率:

當需要製造的晶片被拆成小模組分別製造,就可以各自使用最適合的製程工藝;這樣單個模組的die size比較小,良率相對也會比較高;組合在一起後整體的產片良率也會比較高,比目前先進位製程良率不足30%的大晶片節省了很多成本。

1.2 降低對先進位製程的需求:

在晶片內部所包含的模組中,除了計算單元需要應用最先進的製程來達到良好的效能之外,其他模組例如儲存、模擬、射頻等則沒有必要使用最先進的製程;比如儲存模組在14nm、模擬在65/90nm節點會達到比先進工藝更好的效能;過往SOC晶片的設計中,所有模組都用同一個工藝節點製造,不僅會造成大量的浪費,而且也不是最優解。

1.3 設計靈活成本低:

如果按原來的設計模式,雖然自研或者外購的IP看似可以複用,但與其他模組的連線都需要重新設計,也需要重新再做測試,設計流程並沒有簡化;應用了Chiplet技術之後,芯粒在不同晶片之間可以重複使用,晶片設計流程變得簡單靈活,晶片研發的成本將大幅降低。

1.4 研發週期短:

研發一款複雜晶片時只需要把資源投入到核心模組上,其他功能模組可以使用成熟的「小晶片」,這樣可以大幅縮短產品的研發週期。

2 劣勢

2.1 封裝佈線複雜度高:

由於Chiplet技術將複雜的電路拆解成一系列模組,然後再將不同的模組組裝在一起,因此封裝佈線會變得非常複雜,這也成為使用Chiplet技術構建晶片的一個重要環節。

2.2 封裝基板製造難度大、良率低:

使用Chiplet將不同的「芯粒」拼接在一起後,最終組合成的晶片尺寸會比原本的SOC晶片封裝尺寸大,相應的封裝基板的尺寸也會更大;這樣會增加基板的製造難度,降低基板的生產良率,從而增加封裝成本。

2.3 資料處理難度大:

Chiplet技術可以拆解資料處理器的複雜性,但是這需要在每個子模組之間新增一系列互聯介面,以便所有模組之間進行資料交換,這些互聯介面的設計比較複雜。

2.4 可靠性難度加大:

由於Chiplet技術使用不同製程工藝的模組組合在一起,相對於傳統的單一製程工藝的SOC晶片,晶片可靠性方面的難度加大;晶片封裝尺寸變大,對於封裝可靠性的難度也會加大;這些將對系統的整體可靠性產生負面影響。

2.5 維護成本高:

由於Chiplet技術的高度模組化,如果發生故障,就需要將故障點定位到某個具體的子模組。然後再去找子模組的供應商去分析具體的問題,反饋週期會比較長,相應的維護成本也會較高。

未完待續…...