計算機組成原理——總結

2023-03-25 15:00:45

1. 簡單介紹

三月份的一個主要任務是學一門計算機科班的基礎課程————《計算機組成原理》,在學之前對這部分的知識似懂非懂,沒系統學過所以也不清楚它到底包含哪些知識點,但學完之後又能和本科時期學過的一些課程有了聯絡,比如最基礎的模電和數電,想起之前課設的時候大家熬夜在宿舍做LED時鐘顯示器的情形,那個時候真的是平時不學習、期末抱佛腳,稀裡糊塗四年時間就過去了,算是過的最舒服的幾年時光了。但出來混,遲早要還的,現在開始學這些基礎課程了。

計算機是一個複雜的結構,深挖計算機的第一性,從最基礎的物理知識開始:

- 電路:I=U/R,涉及的硬體有電阻、電感、電容,也有電磁學相關的內容,是資訊時代快速發展的基石。

- 模電: 用連續電訊號作為資訊載體,處理的是連續變化的模擬量電訊號(即其幅值可以是任何值),如無線電、收音機等。不做深入瞭解。但基礎元器件還是三極體。

- 數電:主要是針對數位訊號處理的模組。數位積體電路的執行以開關狀態進行運算,它的精度高,適合複雜的計算。數位電路只要能區分高電平和低電平即可,數位電路不僅能完成數值運算,還可以進行邏輯運算和判斷,因此數位電路又稱為數位邏輯電路。基礎元器件還是三極體,也即電晶體,現在晶片中的基本單位就是這個玩意兒,其尺寸已經達到納米尺度了。數電中我們需要理解的是與或非閘電路,這是構建複雜計算邏輯組合電路的基礎。

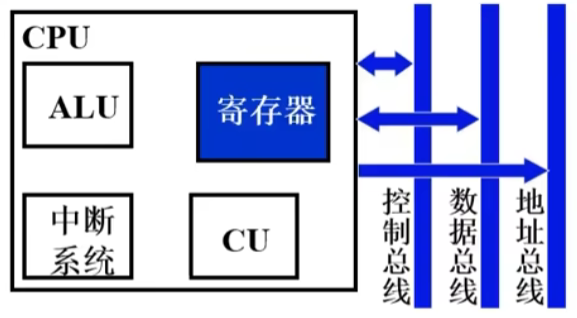

- 計算機組成原理:在數電原理基礎上,構建的複雜電路。主要包含的硬體模組有:匯流排、CPU、主記憶體、I/O裝置。下面分別進行簡要總結

2. 簡單分模組總結

- 匯流排。可以理解為分佈在計算機中用於各模組之間通訊、資料傳輸的線。各模組發出或者可以接受從匯流排上傳輸的資料,資料傳輸的速度和匯流排的頻率和寬度相關。一般我們說的匯流排是系統匯流排,這裡面又分為控制匯流排、地址匯流排和資料匯流排。此外,CPU內部也可能有用於在cpu內部進行資料和命令傳輸的匯流排,可稱為內部匯流排。此外,I/O裝置也可以擁有獨立的io匯流排。總之,這些匯流排都是為傳輸訊號工作的,為了使傳輸訊號更快,匯流排的連線通路會更多,導致系統看起來非常複雜。

- 主記憶體:在計算機執行期間儲存資料和程式碼,CPU在執行期間直接從主記憶體中存取指令和資料。將其理解為一個非常大的陣列即可,且可以根據地址高速隨機存取。

- CPU:這是整個計算機的控制計算中心,所有的任務都是在這裡執行的。邏輯上主要包含四個元件:暫存器、ALU、CU和中斷系統。

- 暫存器是用來臨時儲存一些從記憶體中拿來或者ALU計算結果的儲存單元,如通用暫存器,還有一些是專用暫存器,如PC用於儲存下一條指令在記憶體中的地址,還有狀態暫存器。各種cpu其暫存器設定不盡相同,功能都是用來儲存的,是計算機中最快的記憶體;

- ALU用做算數邏輯運算,包括浮點、定點的加減乘除和邏輯與或非等能力,這個模組只要理解為按照既定的電路做算數邏輯計算即可,內部設計的組合邏輯電路各個晶片大同小異,有的還複用電路即可用做浮點計算也可以做整形計算,至於對輸入的資料做何種運算,是由CU給出的訊號(+-*/ &|!)決定的。

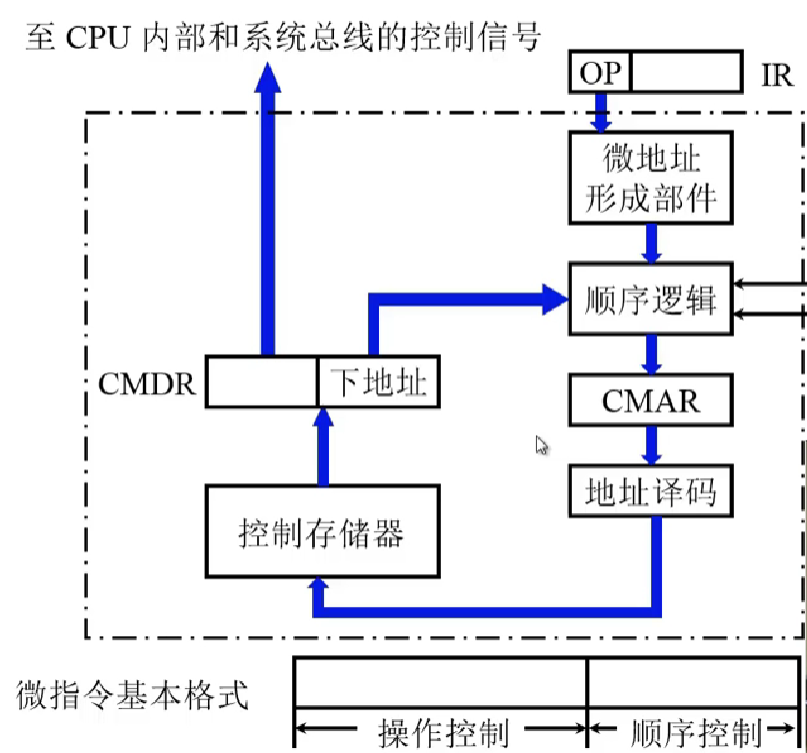

- CU是核心部件,用於將PC中的指令進行解析,講指令由操作碼+運算元組成,CU會將操作碼解析為硬體命令訊號,將運算元從記憶體中載入到約定好的暫存器並按照命令運算。這個過程細分為取指+間址(option)+執行+中斷(option)。其中執行過程最複雜也最耗時。這些步驟細分還會分為微指令等更細微的操作,涉及到時鐘、流水化,微程式控制器等較細的模組,簡單瞭解有這個東西就行。簡言之,最簡單的計算機就是一直在迴圈做取指+執行。組合指令和機器指令是一一對應的,如果有需要做指令級優化的話,掌握相應CPU架構的指令集,寫組合程式碼即可。

- 中斷系統:中斷系統是為相應系統的中斷訊號設計的,一般由硬體實現和軟體實現兩種,是速度和靈活性之間權衡的結果。在系統執行過程中,執行的程式本身或者IO裝置都有可能發出中斷請求,中斷程式根據請求的種類不同,在保護現場後,去呼叫對應的中斷程式來處理請求,結束後再返回到之前的程式斷點繼續執行,類似於函數呼叫。

3. 雜項

- 數的表示和計算。

計算機顧名思義是用來計算的,那就涉及到資料的儲存和計算,資料是如何編碼為2進位制並儲存到記憶體或硬碟上的,大端法小端法等。ALU裡面的加法器是如何實現的,乘法是如何利用加法器工作的等等。其實這些都是組合邏輯電路實現的,和電子時鐘原理差不多。當實現了最基本的加減乘除邏輯電路後,複雜的超越函數可以通過泰勒展開等近似方法簡化為加減乘除運算,只不過不能一次性在ALU中完成計算,需要通過軟體的方式,執行很多個指令才能求解出一個近似值。對於那些專用的計算晶片,可能會將常用的非線性函數如sin/cos/log/e^x等以硬體實現模擬,計算速度會大大提高。當然需要有配套的編譯器和指令支援才可以。 - 微程式控制單元。取到一條指令後,會被解析為很多粒度更細的指令按照嚴格順序執行,是在cpu內部硬體實現的,相當於一個指令解碼部件。

- 流水線。多個指令並行執行且不干擾執行結果,基本原則是下一條指令使用上一條指令使用過的內部運算或儲存體,該儲存體或運算單元是當前指令使用完並在指令結束前不會再使用。跳轉指令和耗時不均勻的指令會打亂流水、影響效率。流水邏輯是嚴格保證邏輯和序列執行一致的,在寫組合程式碼的時候按照序列寫即可。

4. 結語

這門課是在計算機組成原理-劉宏偉-B站跟著視訊學的,中間太深太細的沒有深究,畢竟工作中用不到,只把組成原理的整體結構和知識點看完了,也做了這篇總結,主要是為了建立計算機組成原理的基本知識點範疇,並把硬體知識和上層程式碼聯絡起來,也把計算機硬體和之前學的數電建立了連結。接下來,還有一門作業系統,是重中之重。下個月主攻CS,道阻且長行則將至。