pcie3.0x4最大速度是多少

PCIe3.0x4理論最大讀或者寫的速度為4GB/s,不考慮協定開銷,每秒可以傳輸4GB/4K個4K大小的IO,該值為1M,即理論上最大IOPS為1000K。因此,一個SSD不管底層用什麼媒介,flash還是3d xpoint,介面速度就這麼塊,最大IOPS是不可能超過這個值的。

本教學操作環境:windows7系統、Dell G3電腦。

PCIe介面介紹

PCIe發展到現在,速度一代比一代快。

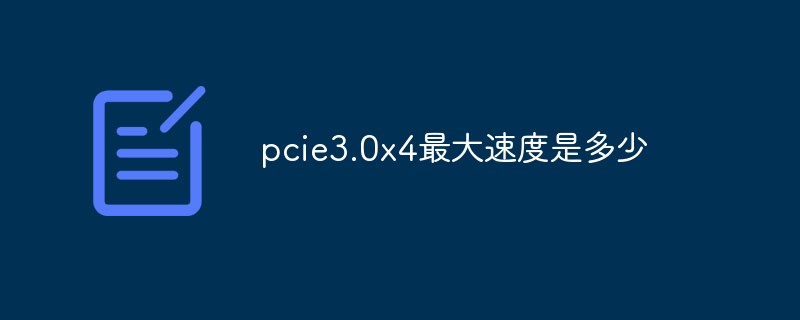

Link Width這一行,我們看到X1,X2,X4…,這是什麼意思?這是指PCIe連線的通道數(Lane)。就像高速一樣,有單根道,有2根道的,有4根道的,不過像8根道或者更多道的公路不常見,但PCIe是可以最多32條道的。

兩個裝置之間的PCIe連線,叫做一個Link,如下圖所示:

從A到B,之間是個雙向連線,車可以從A駛向B,同時,車也可以從B駛向A,各行其道。兩個PCIe裝置之間,有專門的傳送和接收通道,資料可以同時往兩個方向傳輸,PCIe spec稱這種工作模式為雙單工模式(dual-simplex),可以理解為全雙工模式。

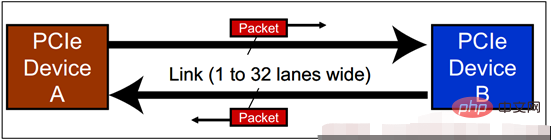

SATA是什麼工作模式呢?

和PCIe一樣,SATA也有獨立的傳送和接收通道,但與PCIe工作模式不一樣:同一時間,只有一條道可以進行資料傳輸,也就是說,你在一條道上傳送資料,另外一條道上不能接收資料,反之亦然。這種工作模式應該是半雙工模式。PCIe猶如我們的手機,雙方可以同時講話,而SATA就是對講機了,一個人在說話,另外一個人就只能聽不能說。

回到前面PCIe頻寬那張表,上面的頻寬,比如PCIe3.0x1,頻寬為2GB/s,是指雙向頻寬,即讀寫頻寬。如果單指讀或者寫,該值應該減半,即1GB/s的讀速度或者寫速度。

我們來看看錶裡面的頻寬是怎麼算出來的。

PCIe是序列匯流排,PCIe1.0的線上位元傳輸速率為2.5Gb/s,物理層使用8/10編碼,即8位元的資料,實際在物理線路上是需要傳輸10位元的,因此:

PCIe1.0 x 1的頻寬=(2.5Gb/s x 2(雙向通道))/ 10bit = 0.5GB/s

登入後複製這是單條Lane的頻寬,有幾條Lane,那麼整個頻寬就0.5GB/s乘以Lane的數目。

PCIe2.0的線上位元傳輸速率在PCIe1.0的基礎上翻了一倍,為5Gb/s,物理層同樣使用8/10編碼,所以:

PCIe2.0 x 1的頻寬=(5Gb/s x 2(雙向通道))/ 10bit = 1GB/s

登入後複製同樣,有多少條Lane,頻寬就是1GB/s乘以Lane的數目。

PCIe3.0的線上位元傳輸速率沒有在PCIe2.0的基礎上翻倍,不是10Gb/s,而是8Gb/s,但物理層使用的是128/130編碼進行資料傳輸,所以:

PCIe3.0 x 1的頻寬=(8Gb/s x 2(雙向通道))/ 8bit = 2GB/s

登入後複製同樣,有多少條Lane,頻寬就是2GB/s乘以Lane的數目。

由於採用了128/130編碼,128位元的資料,只額外增加了2bit的開銷,有效資料傳輸比率增大,雖然線上位元傳輸率沒有翻倍,但有效資料頻寬還是在PCIe2.0的基礎上做到翻倍。

這裡值得一提的是,上面算出的資料頻寬已經考慮到8/10或者128/130編碼,因此,大家在算頻寬的時候,沒有必要再考慮線上編碼的問題了。

和SATA單通道不同,PCIe連線可以通過增加通道數擴充套件頻寬,彈性十足。通道數越多,速度越快。不過,通道數越多,成本越高,佔用更多空間,還有就是更耗電。因此,使用多少通道,應該在效能和其他因素之間進行一個綜合考慮。單考慮效能的話,PCIe最高頻寬可達64GB/s,PCIe 3.0 x 32對應的頻寬,很恐怖的一個資料。不過,現有的PCIe介面SSD,一般最多使用4通道,如PCIe3.0x4,雙向頻寬為8GB/s,讀或者寫頻寬為4GB/s。

幾個GB/s的傳輸速度,讀寫小電影那是槓槓的。

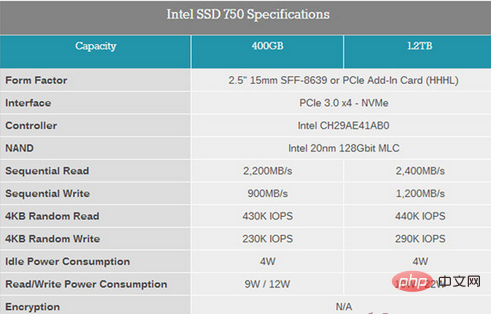

在此,順便來算算PCIe3.0x4理論上最大的4K IOPS。PCIe3.0x4理論最大讀或者寫的速度為4GB/s,不考慮協定開銷,每秒可以傳輸4GB/4K個4K大小的IO,該值為1M,即理論上最大IOPS為1000K。因此,一個SSD,不管你底層用什麼媒介,flash還是3d xpoint,介面速度就這麼塊,最大IOPS是不可能超過這個值的。

PCIe是從PCI發展過來的,PCIe的」e」是express的簡稱,快的意思。PCIe怎麼就能比PCI(或者PCI-X)快呢?PCIe在物理傳輸上,跟PCI有著本質的區別:PCI使用並口傳輸資料,而PCIe使用的是串列埠傳輸。我PCI並行匯流排,單個時鐘週期可以傳輸32bit或者64bit,怎麼就比不了你單個時鐘週期傳輸1個bit資料的序列匯流排呢?

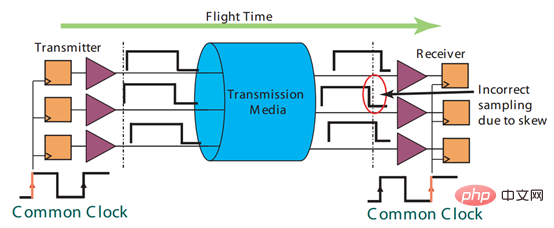

在實際時脈頻率比較低的情況下,並口因為可以同時傳輸若干位元,速率確實比串列埠快。隨著技術的發展,資料傳輸速率要求越來越快,要求時脈頻率也越來越快,但是,並行匯流排時脈頻率不是想快就能快的。

在傳送端,資料在某個時鐘沿傳出去(左邊時鐘第一個上升沿),在接收端,資料在下個時鐘沿(右邊時鐘第二個上升沿)接收。因此,要在接收端能正確採集到資料,要求時鐘的週期必須大於資料傳輸的時間(從傳送端到接收端,flight time)。受限於資料傳輸時間(該時間還隨著傳輸線長度的增加而增加),因此時脈頻率不能做得太高。另外,時鐘訊號線上上傳輸的時候,也會存在相位偏移(clock skew ),影響接收端的資料採集;還有,並行傳輸,接收端必須等最慢的那個bit資料到了以後,才能鎖住整個資料 (signal skew)。

PCIe使用序列匯流排進行資料傳輸就沒有這些問題。它沒有外部時鐘訊號,它的時鐘資訊通過8/10編碼或者128/130編碼嵌入在資料流,接收端可以從資料流裡面恢復時鐘資訊,因此,它不受資料線上上傳輸時間的限制,你導線多長都沒有問題,你資料傳輸頻率多快也沒有問題;沒有外部時鐘訊號,自然就沒有所謂的clock skew問題;由於是序列傳輸,只有一個bit傳輸,所以不存在signal skew問題。但是,如果使用多條lane傳輸資料(序列中又有並行,哈哈),這個問題又回來了,因為接收端同樣要等最慢的那個lane上的資料到達才能處理整個資料。

PCIe匯流排的基礎知識

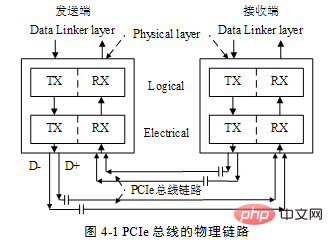

與PCI匯流排不同,PCIe匯流排使用端到端的連線方式,在一條PCIe鏈路的兩端只能各連線一個裝置,這兩個裝置互為是資料傳送端和資料接收端。PCIe匯流排除了匯流排鏈路外,還具有多個層次,傳送端傳送資料時將通過這些層次,而接收端接收資料時也使用這些層次。PCIe匯流排使用的層次結構與網路協定棧較為類似。

PCIe鏈路使用「端到端的資料傳送方式」,傳送端和接收端中都含有TX(傳送邏輯)和RX(接收邏輯),其結構如圖所示。

由上圖所示,在PCIe匯流排的物理鏈路的一個資料通路(Lane)中,由兩組差分訊號,共4根訊號線組成。其中傳送端的TX部件與接收端的RX部件使用一組差分訊號連線,該鏈路也被稱為傳送端的傳送鏈路,也是接收端的接收鏈路;而傳送端的RX部件與接收端的TX部件使用另一組差分訊號連線,該鏈路也被稱為傳送端的接收鏈路,也是接收端的傳送鏈路。一個PCIe鏈路可以由多個Lane組成。

高速差分訊號電氣規範要求其傳送端串接一個電容,以進行AC耦合。該電容也被稱為AC耦合電容。PCIe鏈路使用差分訊號進行資料傳送,一個差分訊號由D+和D-兩根訊號組成,訊號接收端通過比較這兩個訊號的差值,判斷傳送端傳送的是邏輯「1」還是邏輯「0」。

與單端訊號相比,差分訊號抗干擾的能力更強,因為差分訊號在佈線時要求「等長」、「等寬」、「貼近」,而且在同層。因此外部干擾噪聲將被「同值」而且「同時」載入到D+和D-兩根訊號上,其差值在理想情況下為0,對訊號的邏輯值產生的影響較小。因此差分訊號可以使用更高的匯流排頻率。

此外使用差分訊號能有效抑制電磁干擾EMI(Electro Magnetic Interference)。由於差分訊號D+與D-距離很近而且訊號幅值相等、極性相反。這兩根線與地線間耦合電磁場的幅值相等,將相互抵消,因此差分訊號對外界的電磁干擾較小。當然差分訊號的缺點也是顯而易見的,一是差分訊號使用兩根訊號傳送一位資料;二是差分訊號的佈線相對嚴格一些。

PCIe鏈路可以由多條Lane組成,目前PCIe鏈路可以支援1、2、4、8、12、16和32個Lane,即×1、×2、×4、×8、×12、×16和×32寬度的PCIe鏈路。每一個Lane上使用的匯流排頻率與PCIe匯流排使用的版本相關。

第1個PCIe匯流排規範為V1.0,之後依次為V1.0a,V1.1,V2.0和V2.1。目前PCIe匯流排的最新規範為V2.1,而V3.0正在開發過程中,預計在2010年釋出。不同的PCIe匯流排規範所定義的匯流排頻率和鏈路編碼方式並不相同,如表41所示。

PCIe匯流排規範與匯流排頻率和編碼的關係

| PCIe匯流排規範 | 匯流排頻率[1] | 單Lane的峰值頻寬 | 編碼方式 |

|---|---|---|---|

| 1.x | 1.25GHz | 2.5GT/s | 8/10b編碼 |

| 2.x | 2.5GHz | 5GT/s | 8/10b編碼 |

| 3.0 | 4GHz | 8GT/s | 128/130b編碼 |

如上表所示,不同的PCIe匯流排規範使用的匯流排頻率並不相同,其使用的資料編碼方式也不相同。PCIe匯流排V1.x和V2.0規範在物理層中使用8/10b編碼,即在PCIe鏈路上的10 bit中含有8 bit的有效資料;而V3.0規範使用128/130b編碼方式,即在PCIe鏈路上的130 bit中含有128 bit的有效資料。

由上表所示,V3.0規範使用的匯流排頻率雖然只有4GHz,但是其有效頻寬是V2.x的兩倍。下文將以V2.x規範為例,說明不同寬度PCIe鏈路所能提供的峰值頻寬,如表42所示。

PCIe匯流排的峰值頻寬

| PCIe匯流排的資料位寬 | ×1 | ×2 | ×4 | ×8 | ×12 | ×16 | ×32 |

|---|---|---|---|---|---|---|---|

| 峰值頻寬(GT/s) | 5 | 10 | 20 | 40 | 60 | 80 | 160 |

由上表所示,×32的PCIe鏈路可以提供160GT/s的鏈路頻寬,遠高於PCI/PCI-X匯流排所能提供的峰值頻寬。而即將推出的PCIe V3.0規範使用4GHz的匯流排頻率,將進一步提高PCIe鏈路的峰值頻寬。

在PCIe匯流排中,使用GT(Gigatransfer)計算PCIe鏈路的峰值頻寬。GT是在PCIe鏈路上傳遞的峰值頻寬,其計算公式為匯流排頻率×資料位寬×2。

在PCIe匯流排中,影響有效頻寬的因素有很多,因而其有效頻寬較難計算。儘管如此,PCIe匯流排提供的有效頻寬還是遠高於PCI匯流排。PCIe匯流排也有其弱點,其中最突出的問題是傳送延時。

PCIe鏈路使用序列方式進行資料傳送,然而在晶片內部,資料匯流排仍然是並行的,因此PCIe鏈路介面需要進行串並轉換,這種串並轉換將產生較大的延時。除此之外PCIe匯流排的資料包文需要經過事務層、資料鏈路層和物理層,這些資料包文在穿越這些層次時,也將帶來延時。

在基於PCIe匯流排的裝置中,×1的PCIe鏈路最為常見,而×12的PCIe鏈路極少出現,×4和×8的PCIe裝置也不多見。Intel通常在ICH中整合了多個×1的PCIe鏈路用來連線低速外設,而在MCH中整合了一個×16的PCIe鏈路用於連線顯示卡控制器。而PowerPC處理器通常能夠支援×8、×4、×2和×1的PCIe鏈路。

PCIe匯流排物理鏈路間的資料傳送使用基於時鐘的同步傳送機制,但是在物理鏈路上並沒有時鐘線,PCIe匯流排的接收端含有時鐘恢復模組CDR(Clock Data Recovery),CDR將從接收報文中提取接收時鐘,從而進行同步資料傳遞。

值得注意的是,在一個PCIe裝置中除了需要從報文中提取時鐘外,還使用了REFCLK+和REFCLK-訊號對作為本地參考時鐘

更多相關知識,請存取欄目!

以上就是pcie3.0x4最大速度是多少的詳細內容,更多請關注TW511.COM其它相關文章!