手把手教你蜂鳥e203移植(以Nexys4DDR為例)

準備工作:(網路硬碟連結:)

1.蜂鳥e203的RTL原始碼;

2.一段分頻程式碼;

3.頂層設計檔案(system.v)

4.開發板檔案;

5.Nexys4DDR電路圖;

6.Nexys4DDR管腳約束模板;

7.Nexys4DDR官方檔案。

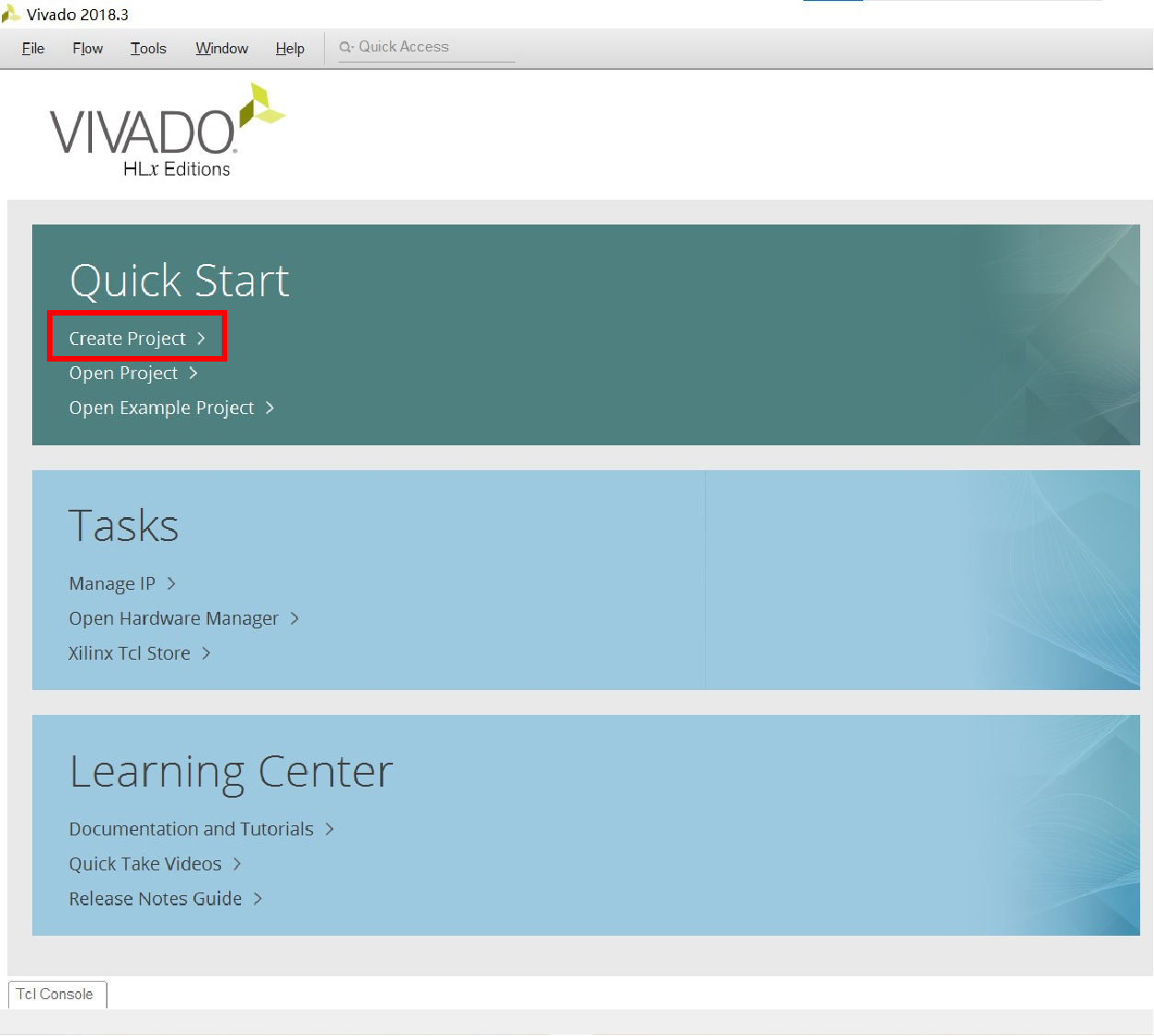

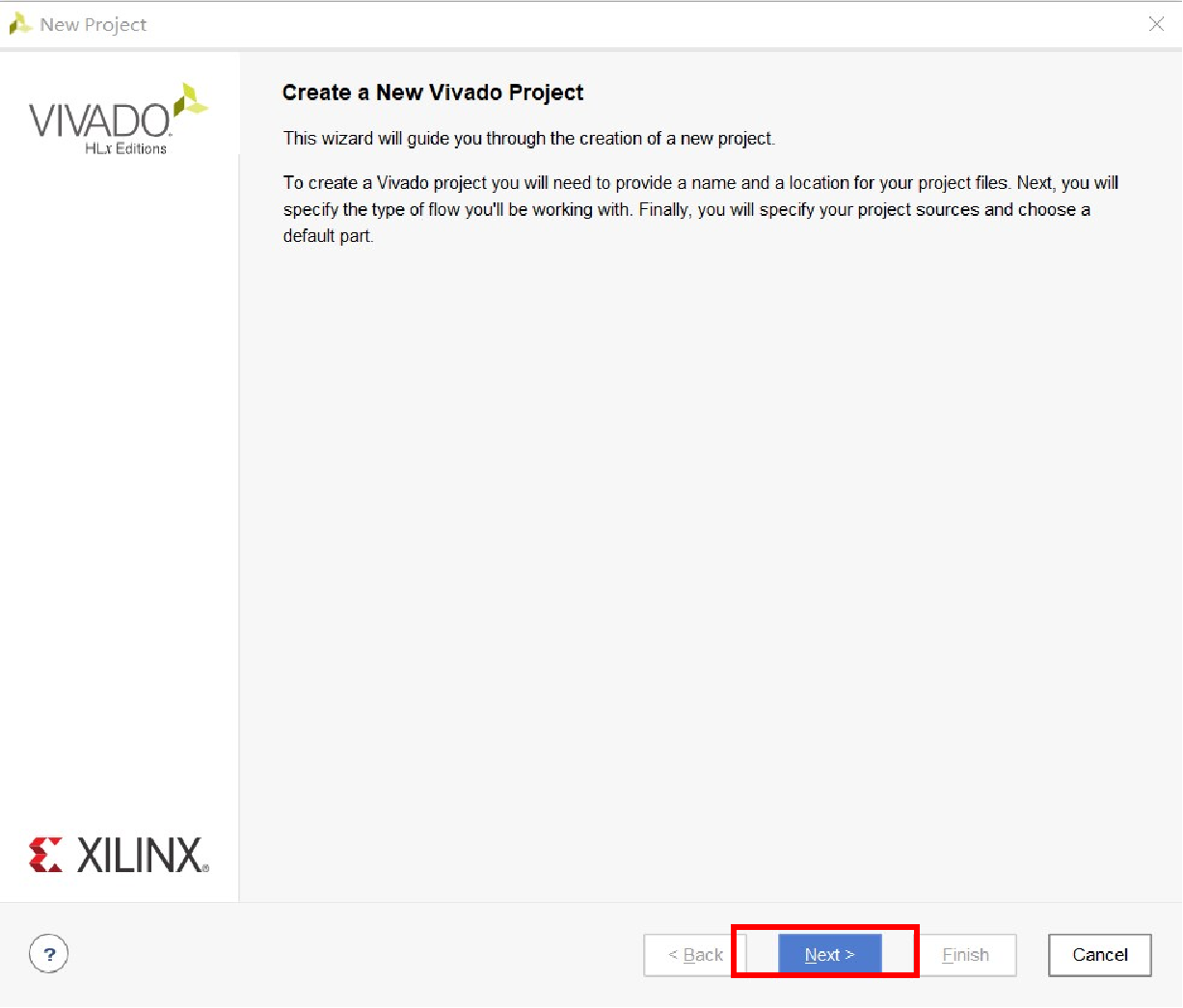

1.

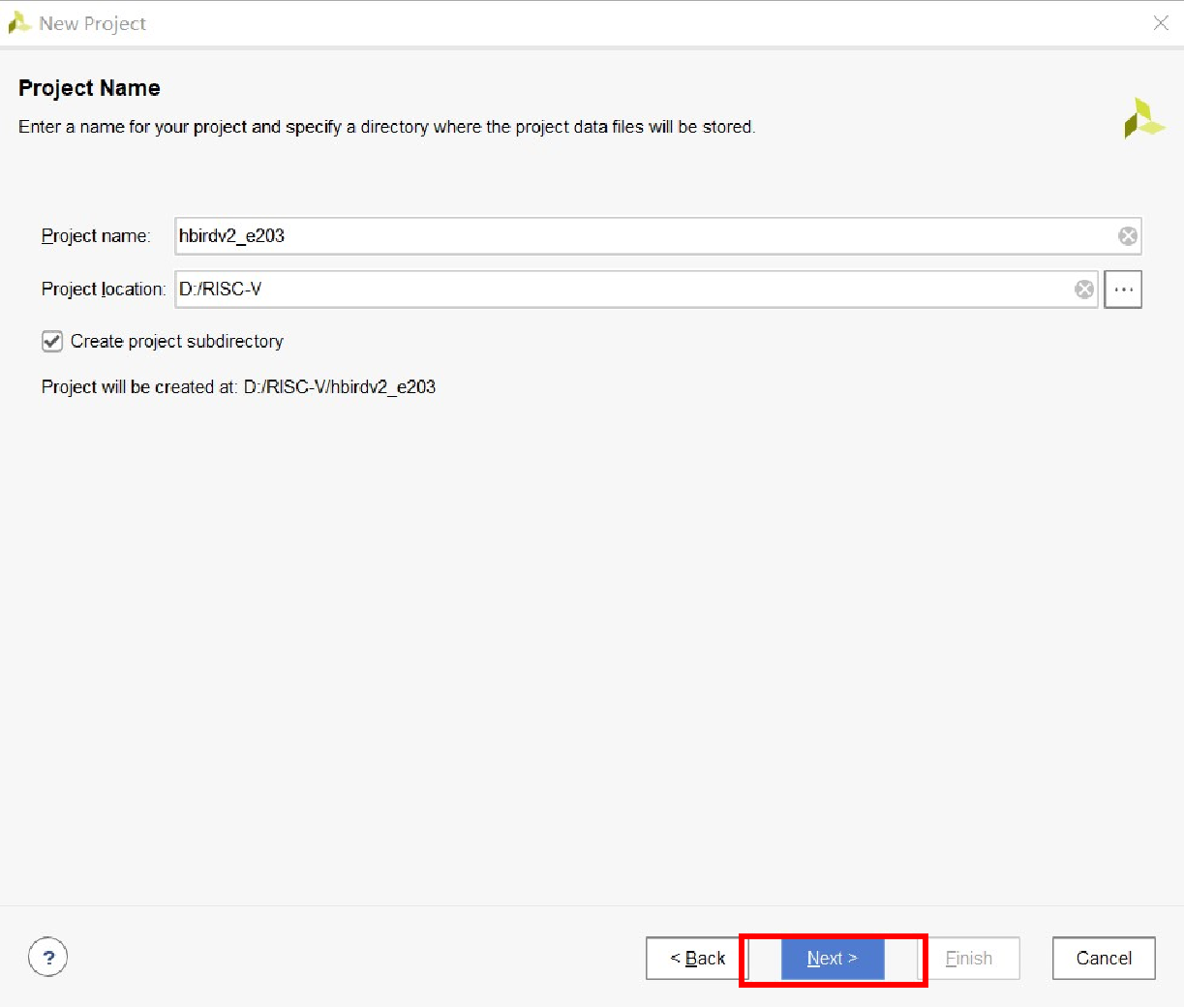

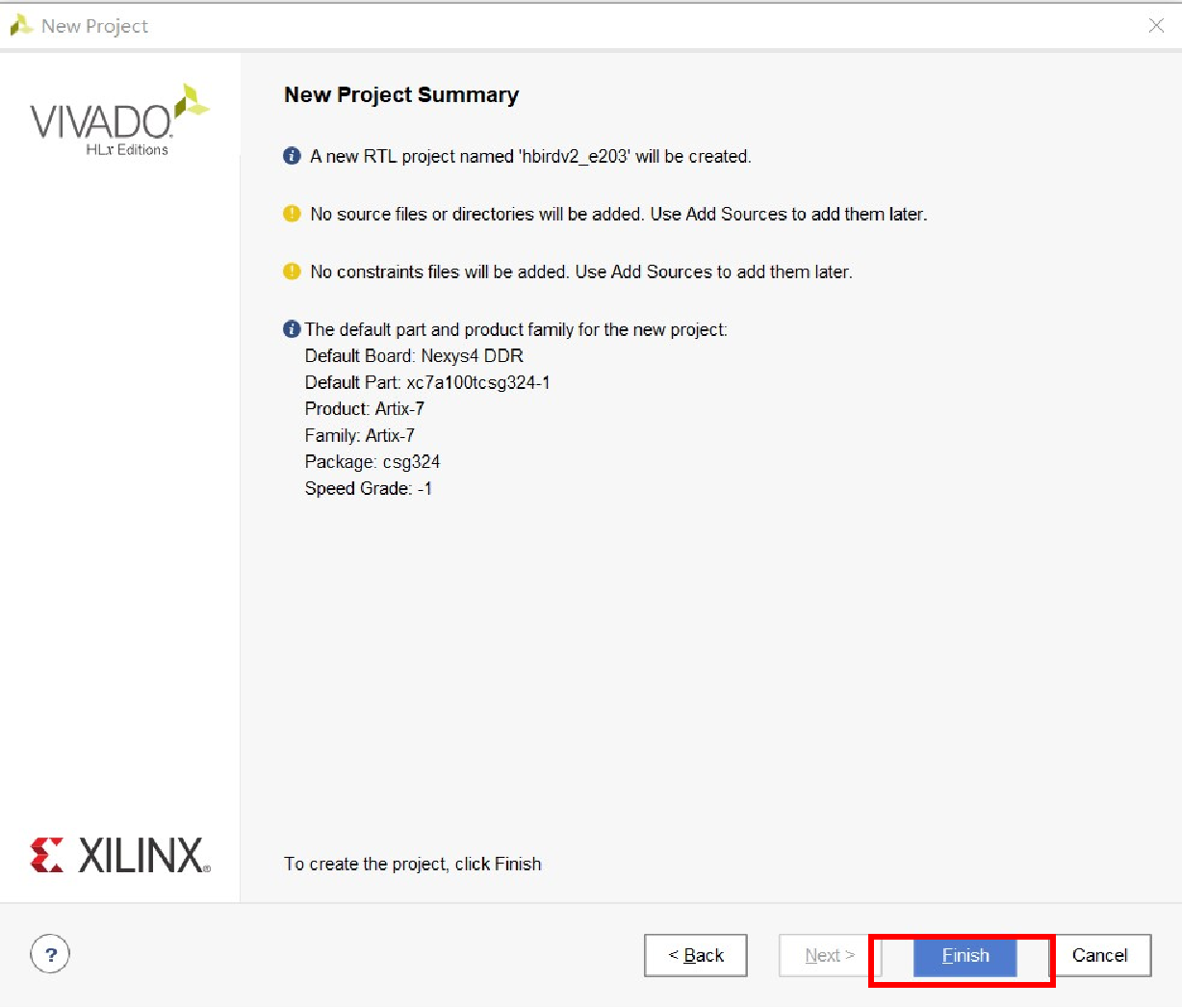

在Vivado中建立工程,命名隨意,路徑隨意;

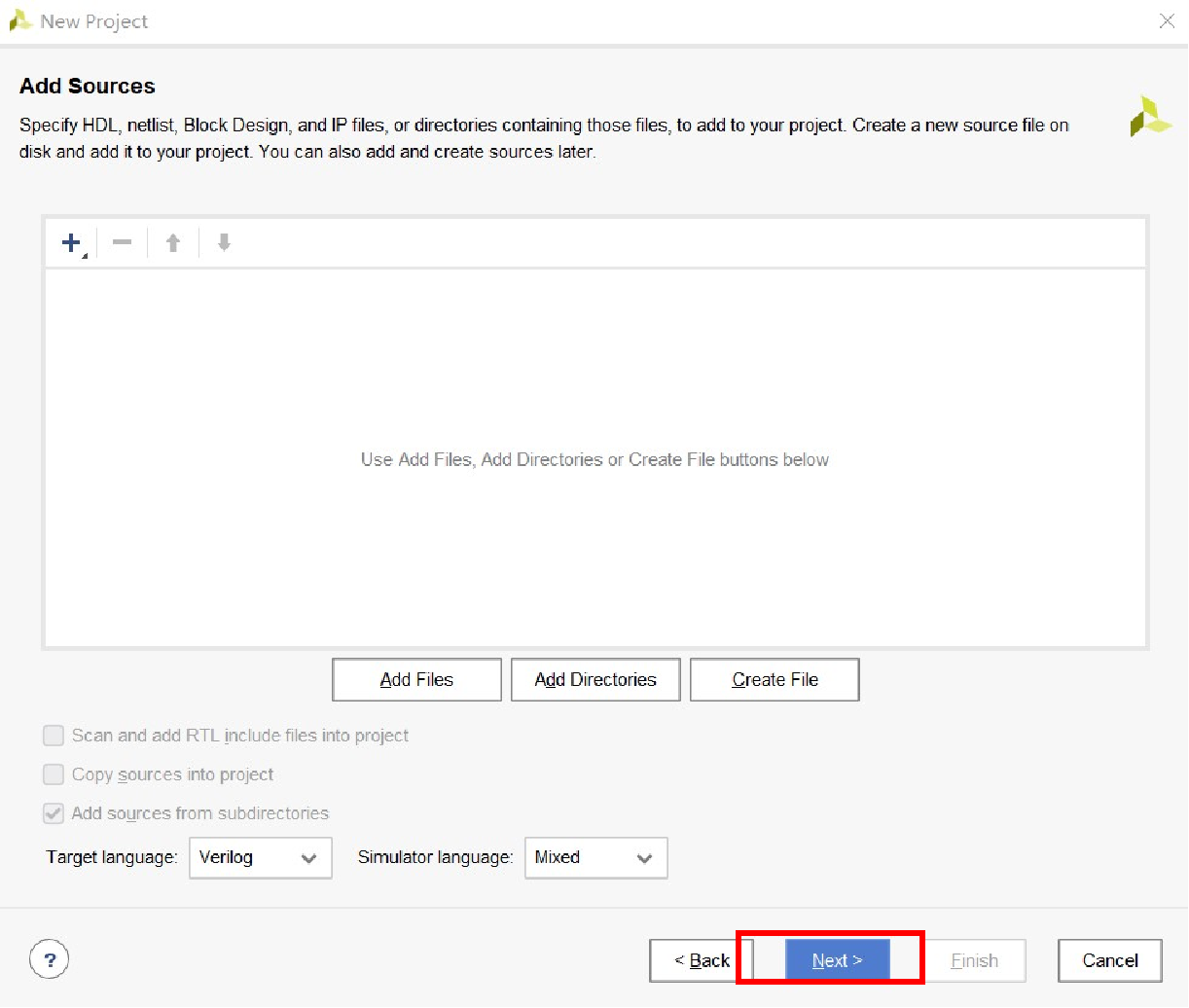

2.

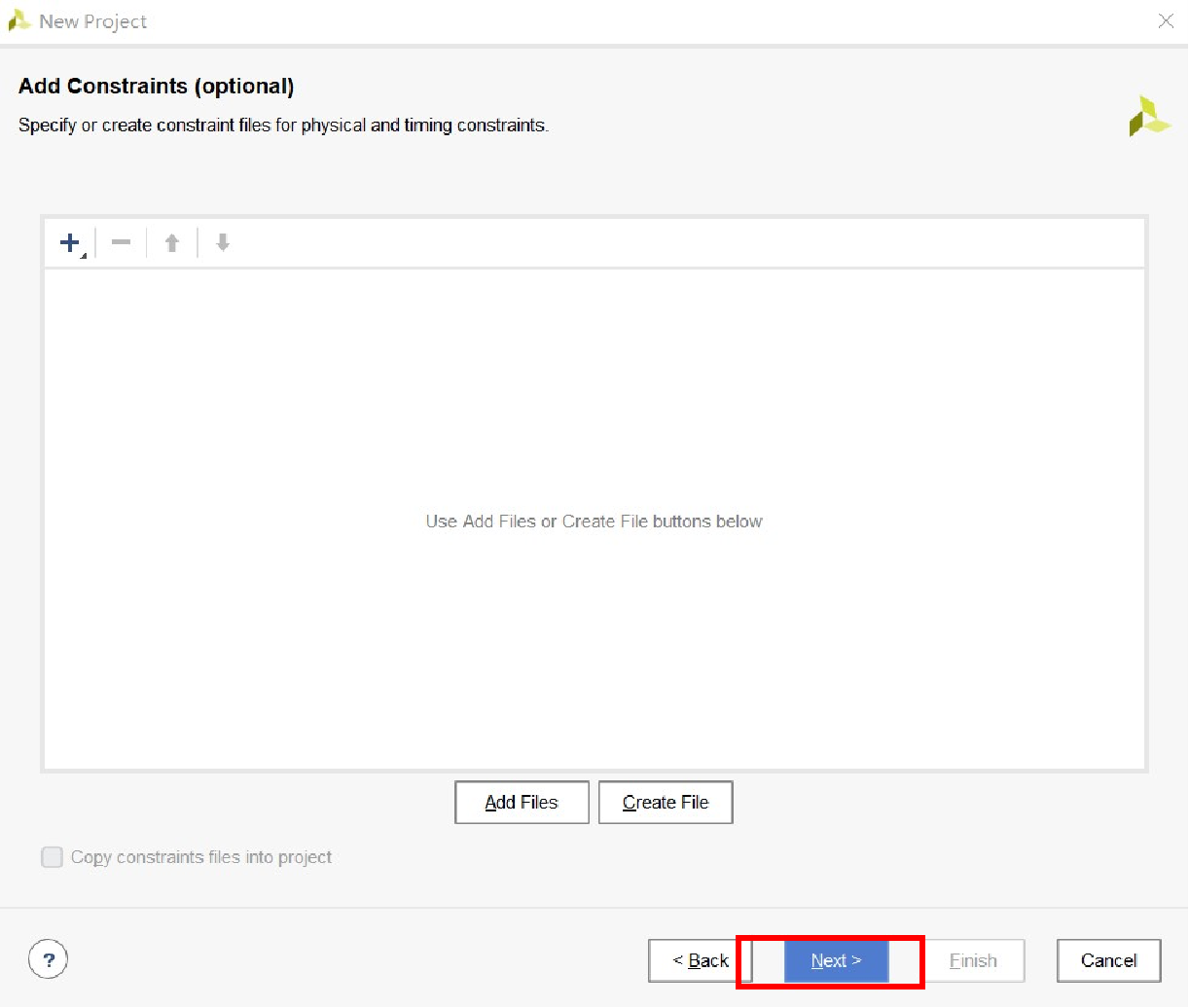

這裡可以選擇是否新增原始檔等,我們先不新增;

3.選擇我們目標要移植到的板子:

這裡我們選擇的是Nexys4DDR,若Vivado庫中沒有此板載檔案,可以新增對應板載檔案到Vivado\2018.2\data\boards\board_files目錄下,這裡我們給出了Nexys4DDR的開發板檔案;

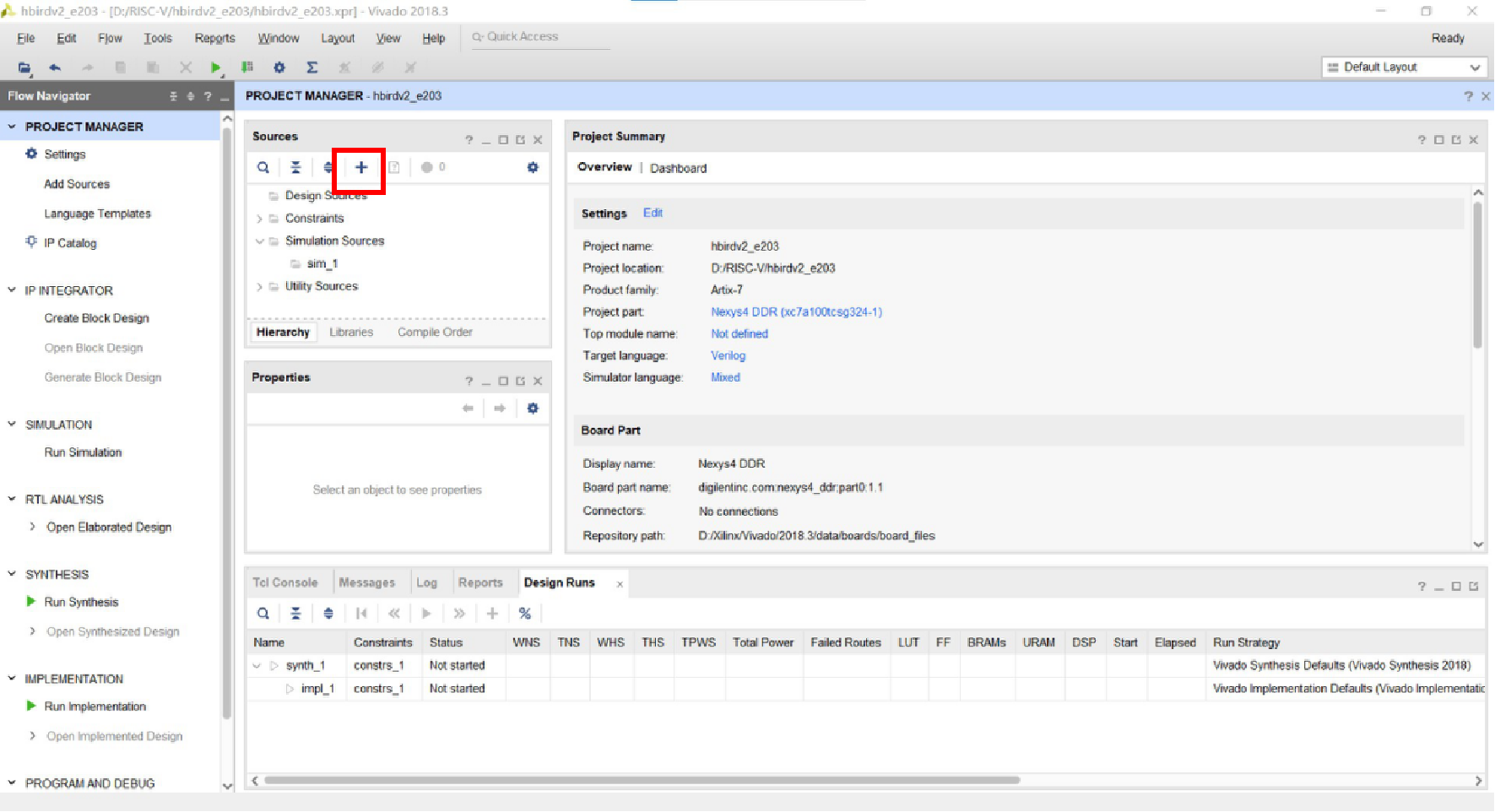

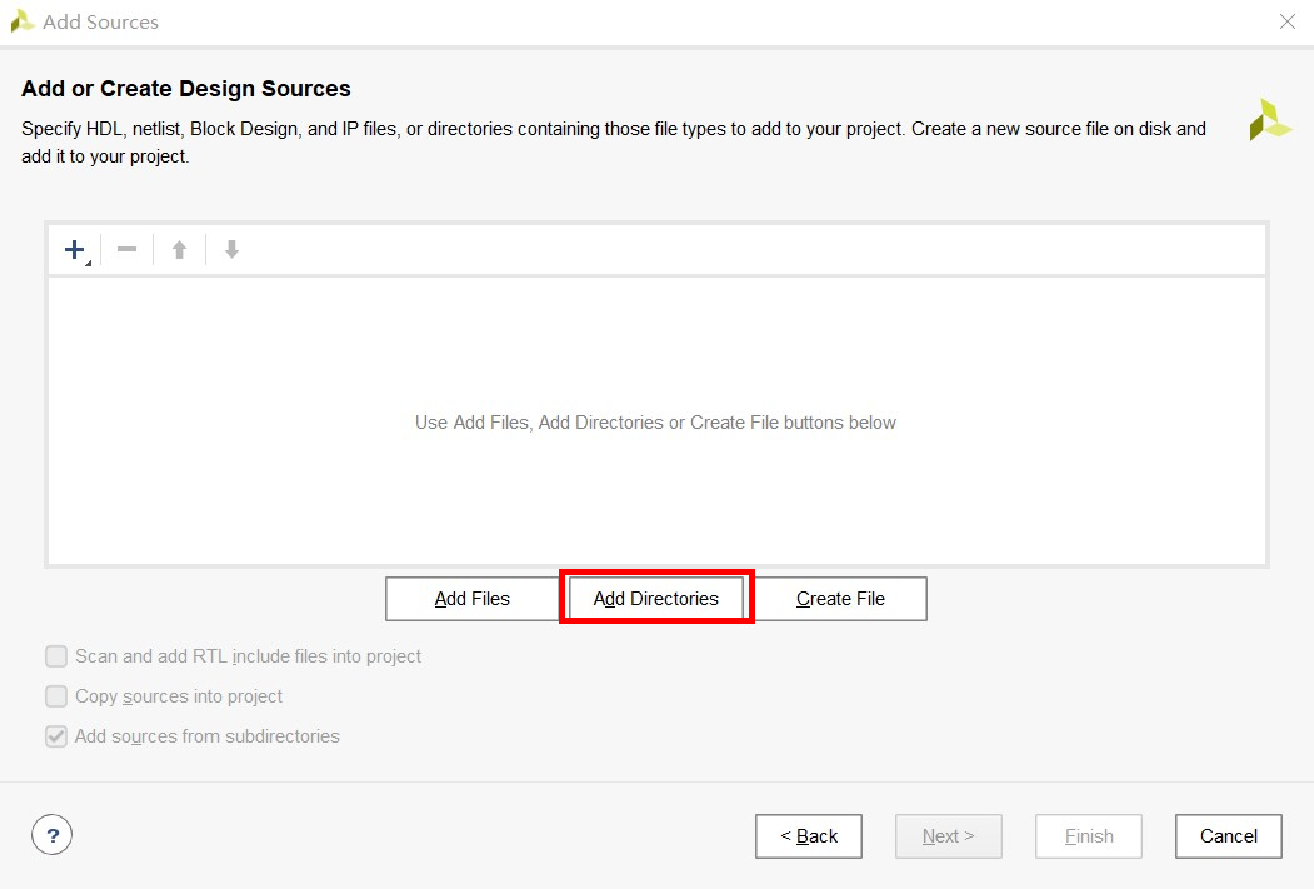

4.新增原始檔:

建立工程完成後,單擊"+",新增原始檔,這裡我們選擇新增的是資料夾e203(路徑為e203_hbirdv2/rtl/e203),Finish完成新增,那兩個勾建議可以勾選,會將新增的原始檔拷貝到我們的工程目錄下,防止對原始檔案造成改動;

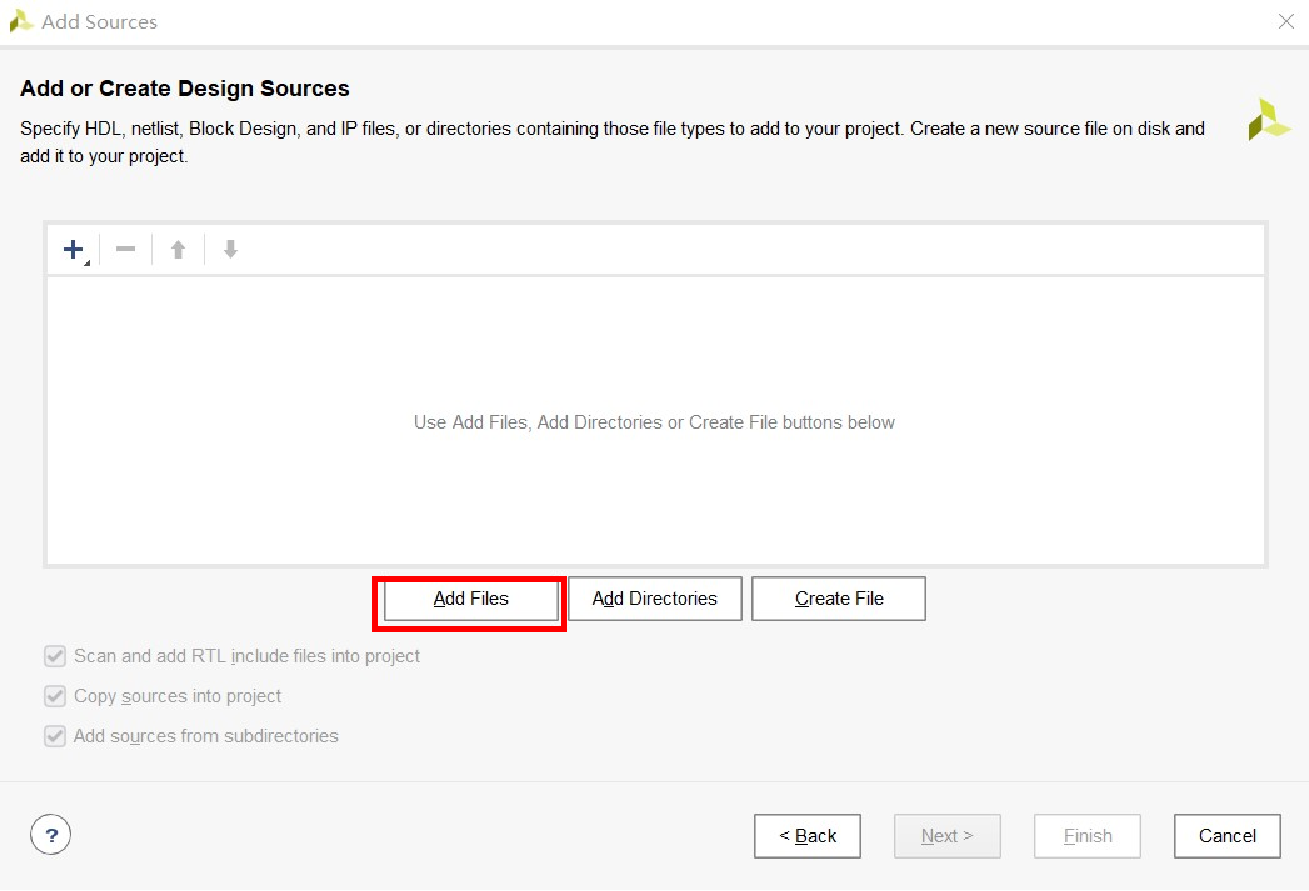

5.新增標頭檔案:

同上操作,找到對應想要移植板子的system.v檔案(路徑為e203_hbirdv2-master\fpga\mcu200t\system.v),這裡選擇的是MCU;

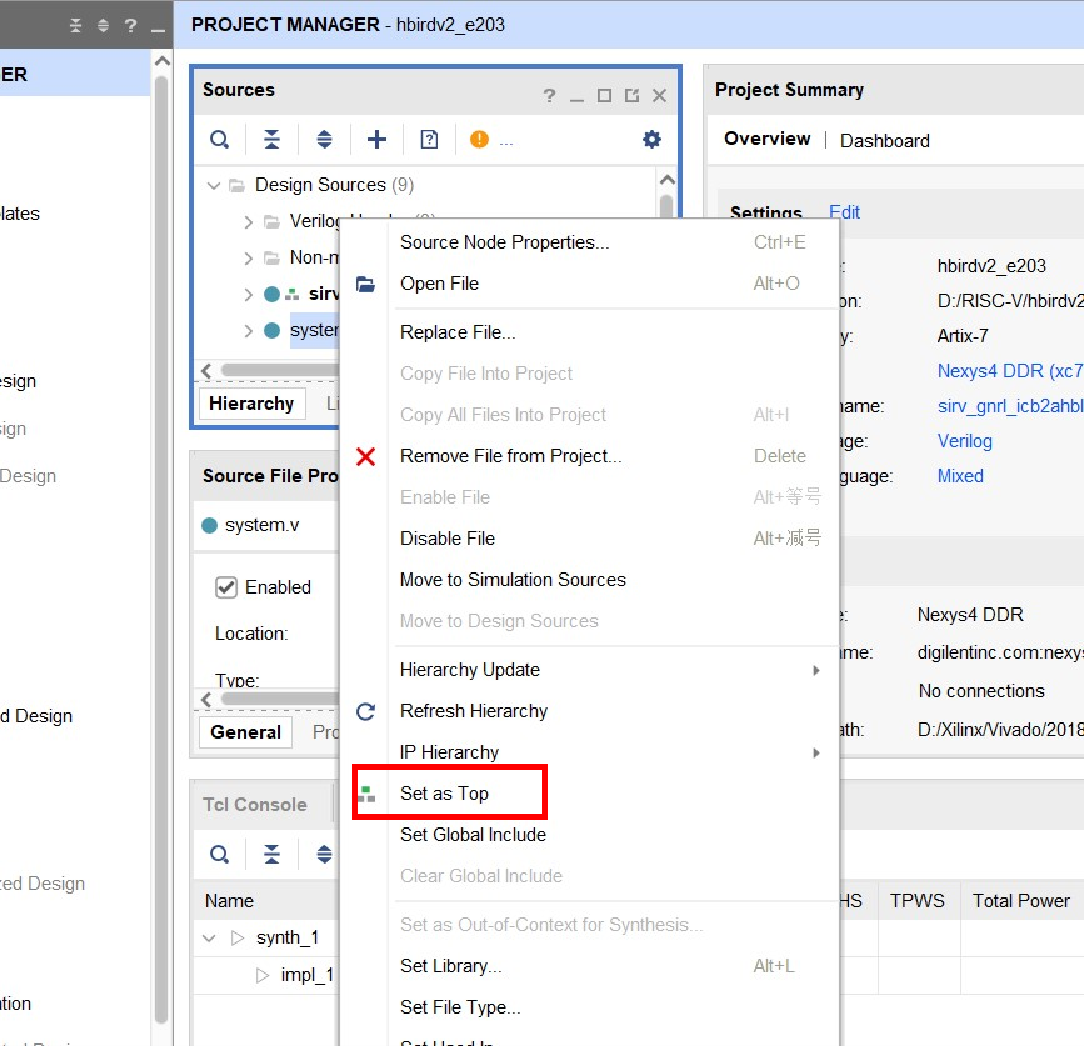

6.設定標頭檔案:

新增完成後,右鍵點選system.v將其設定為標頭檔案;

7.呼叫IP核:

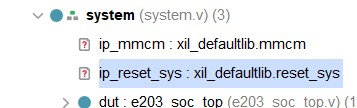

這時,我們會觀察到有兩個檔案有問題,這是由於e203中呼叫了相應的IP核,我們也要在工程中對應新增;

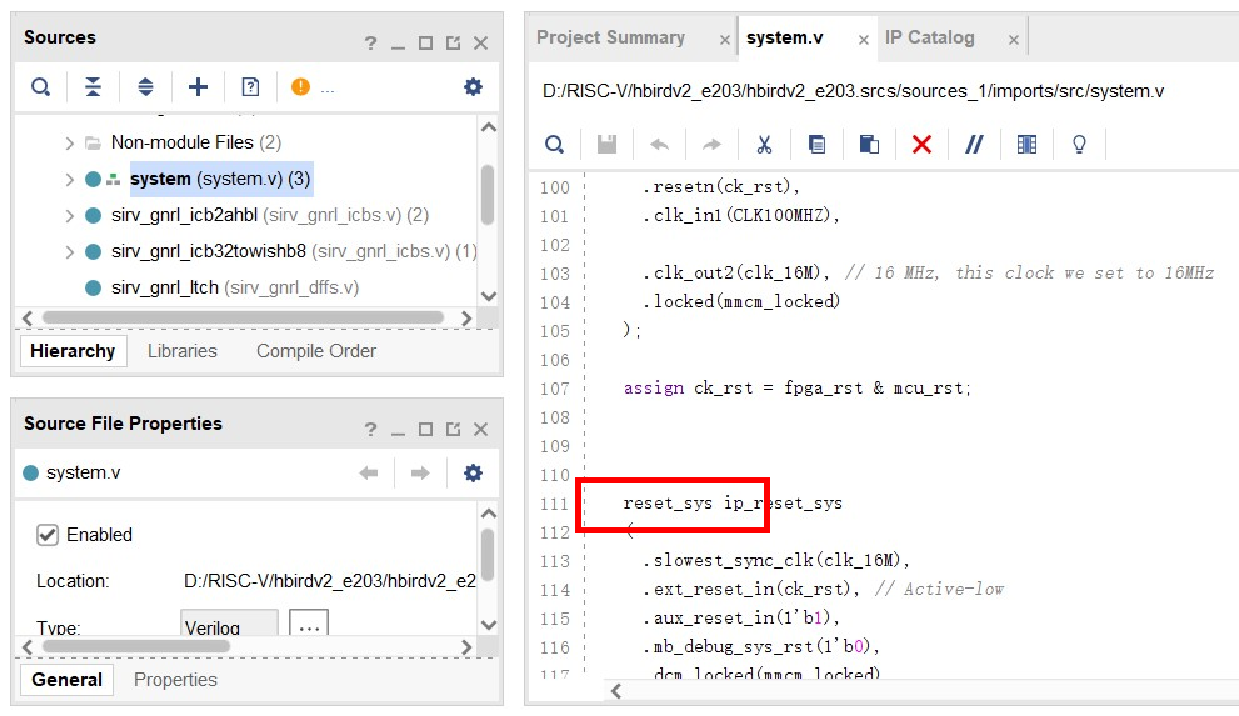

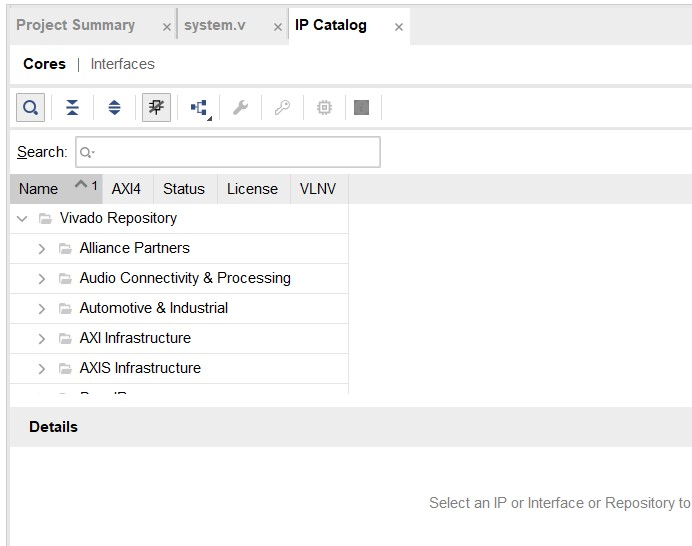

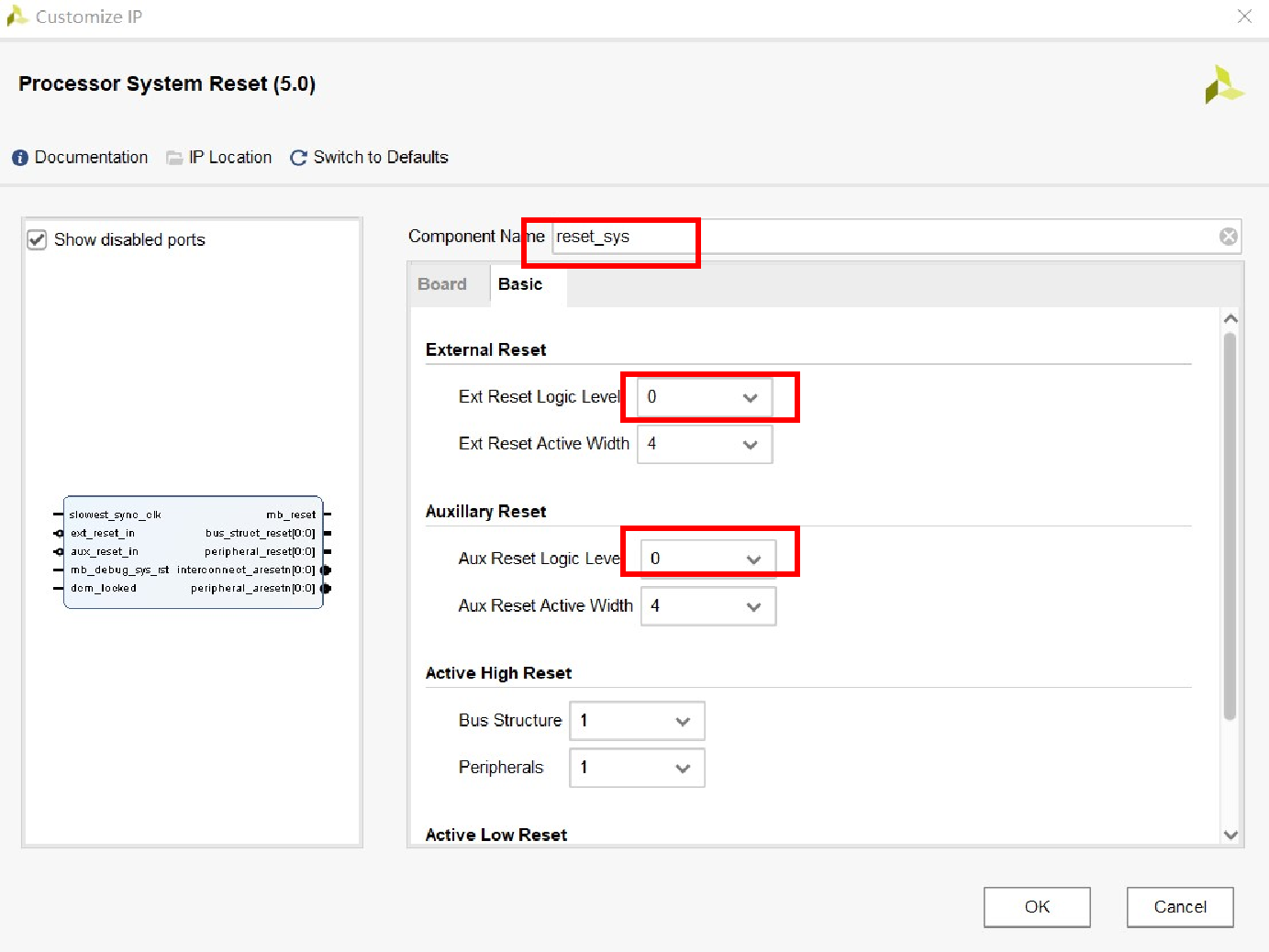

8.新增reset_sys:

在IP目錄中找到對應IP核Processor System Reset,雙擊將名字改為system.v中的對應名字reset_sys。注意!這裡一定要保持名稱一致!後修改其復位的優先順序為最高,即可完成IP核的呼叫;

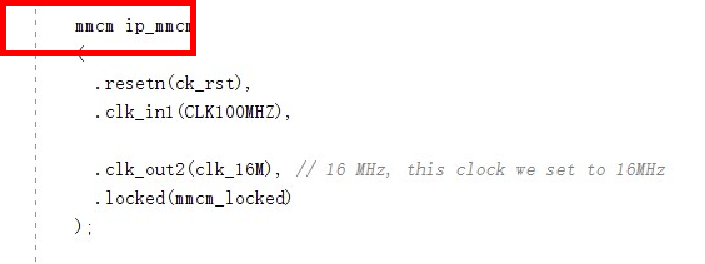

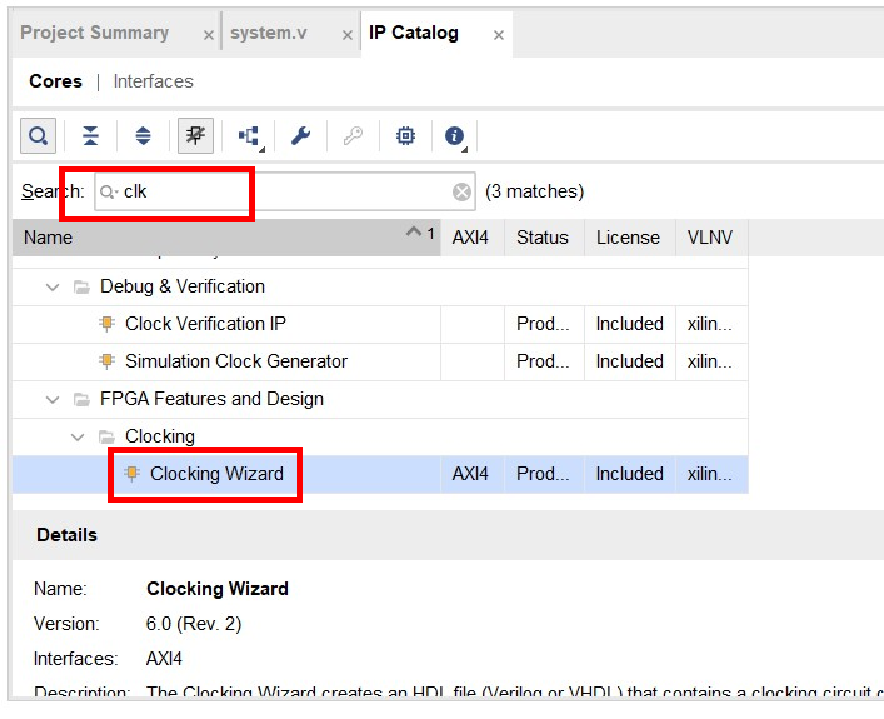

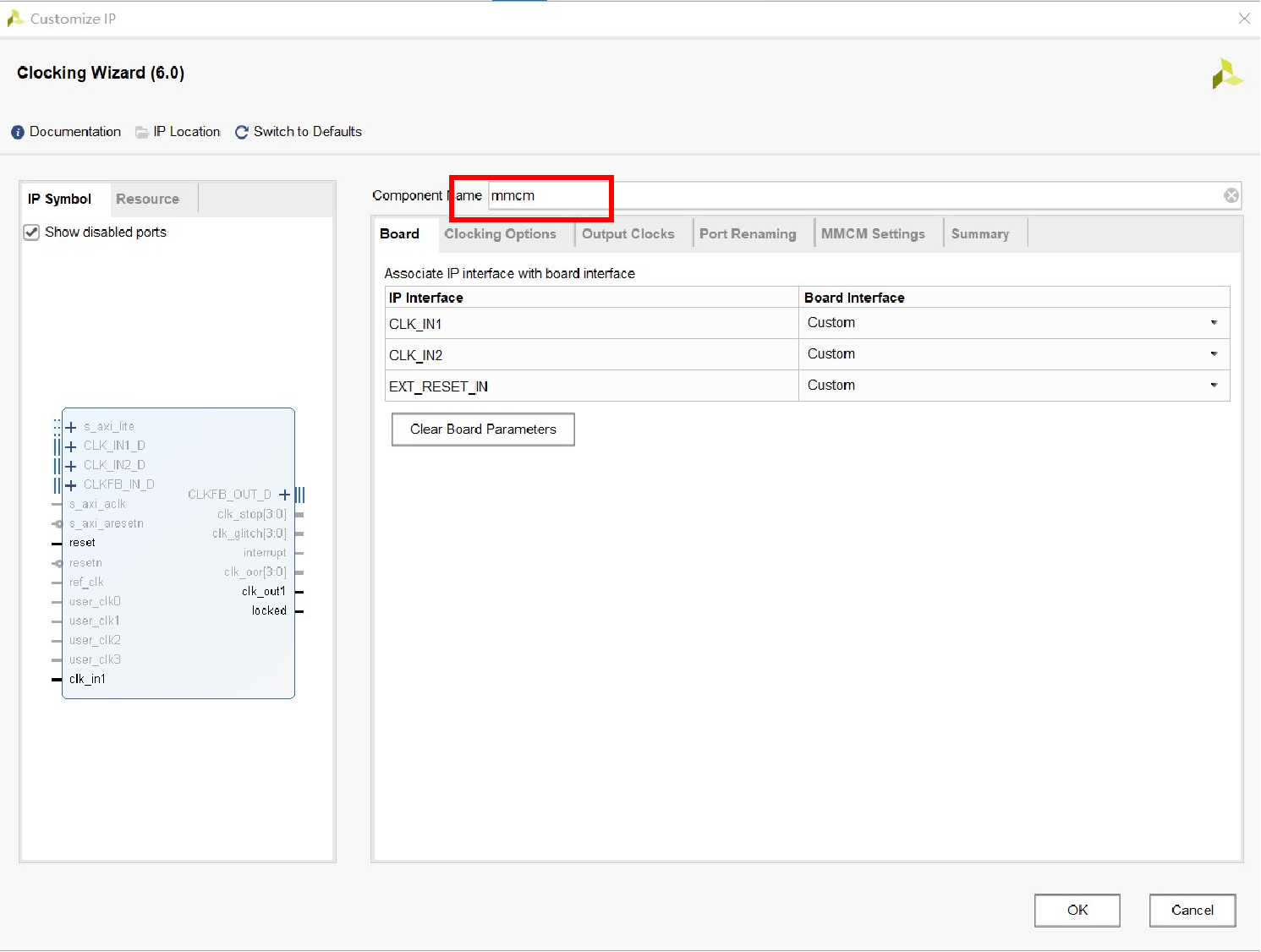

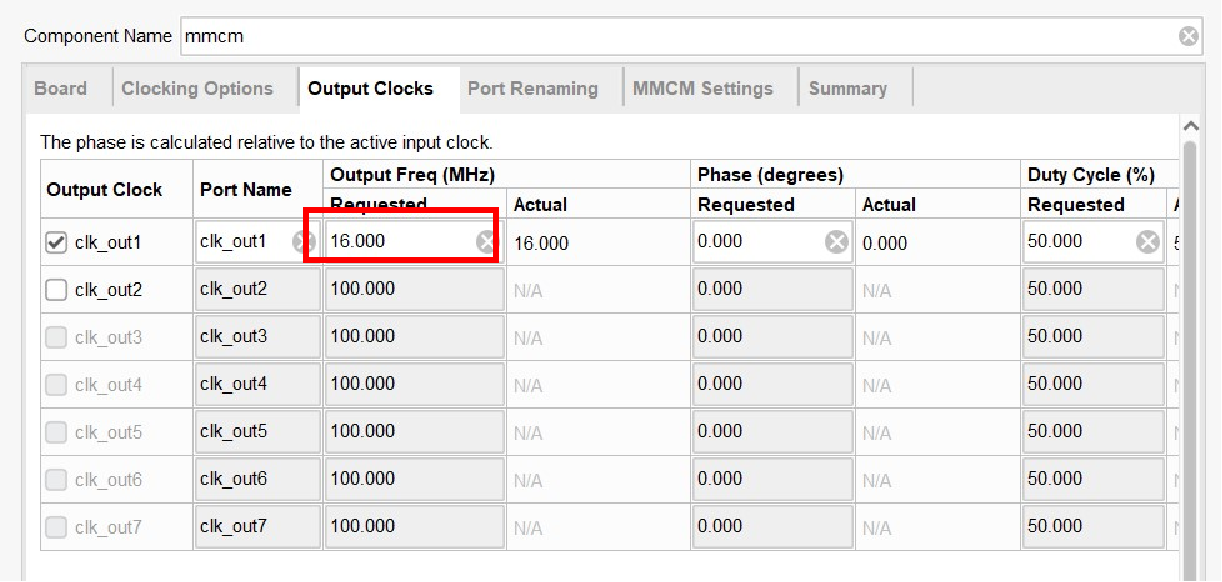

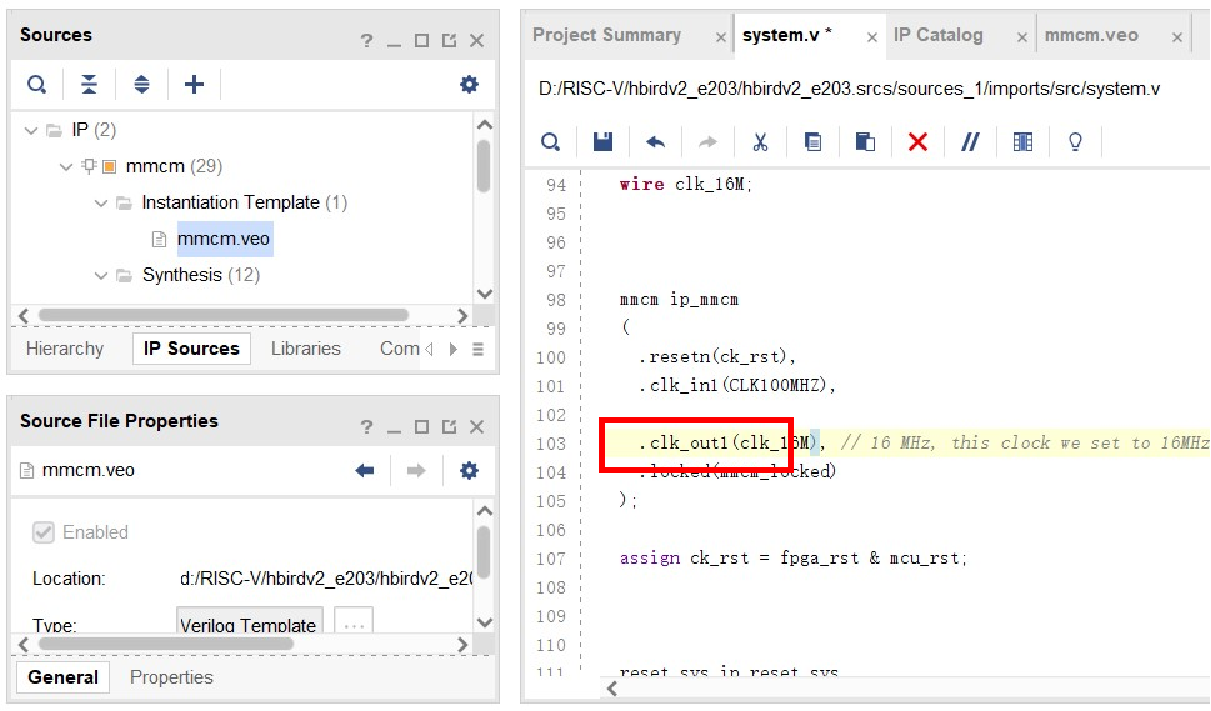

9.新增clk:

在IP目錄中找到對應IP核Clocking Wizard,同上操作,將名改為mmcm,修改生成時脈頻率為16M,改變復位方式為低電平復位,即可完成IP核的呼叫;同時應注意這裡IP核呼叫的例化名稱應與system.v中保持一致。

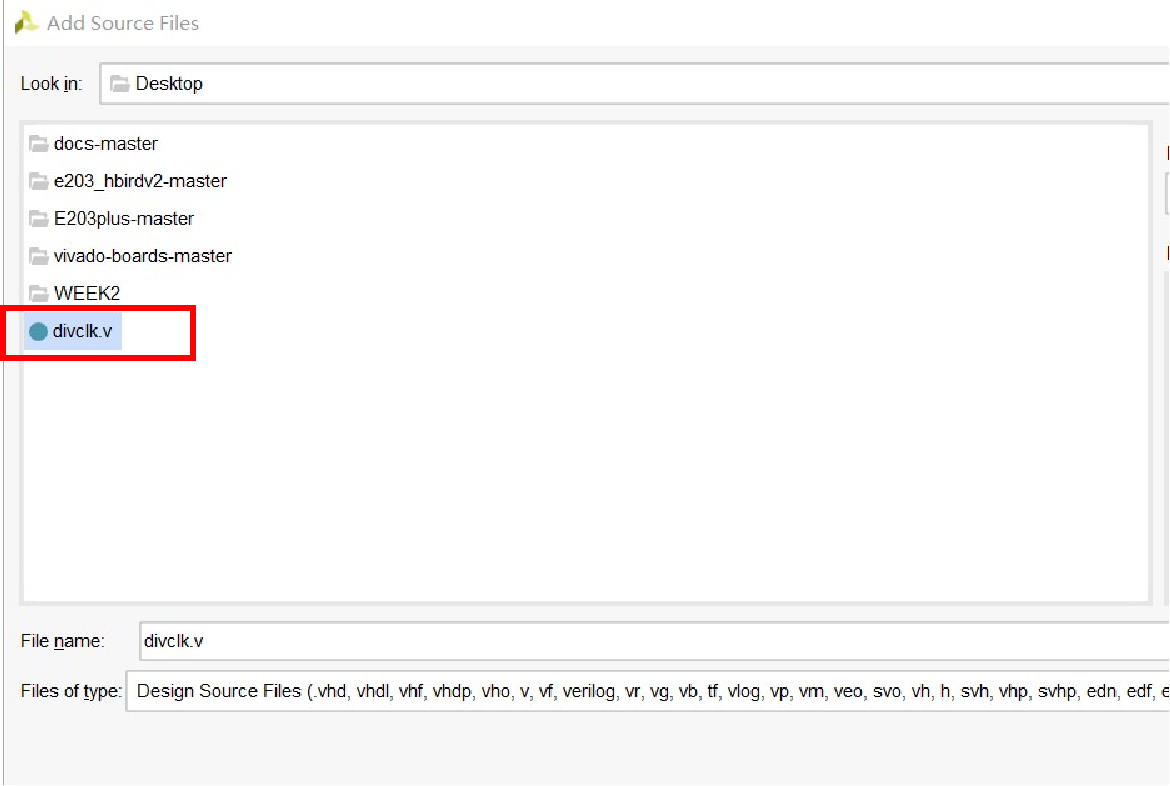

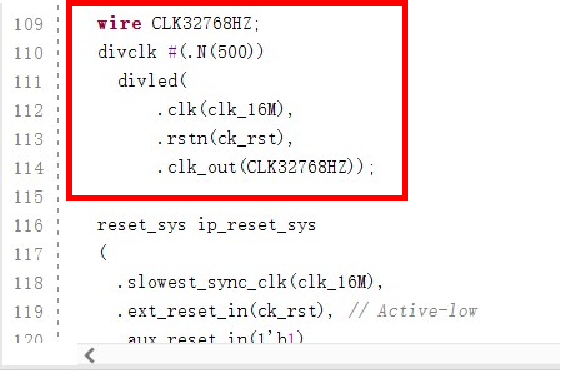

10.新增分頻時鐘模組:

新增原始檔程式碼,若無可以在資料中找到對應的,呼叫該模組生成CLK32768KHZ的時鐘

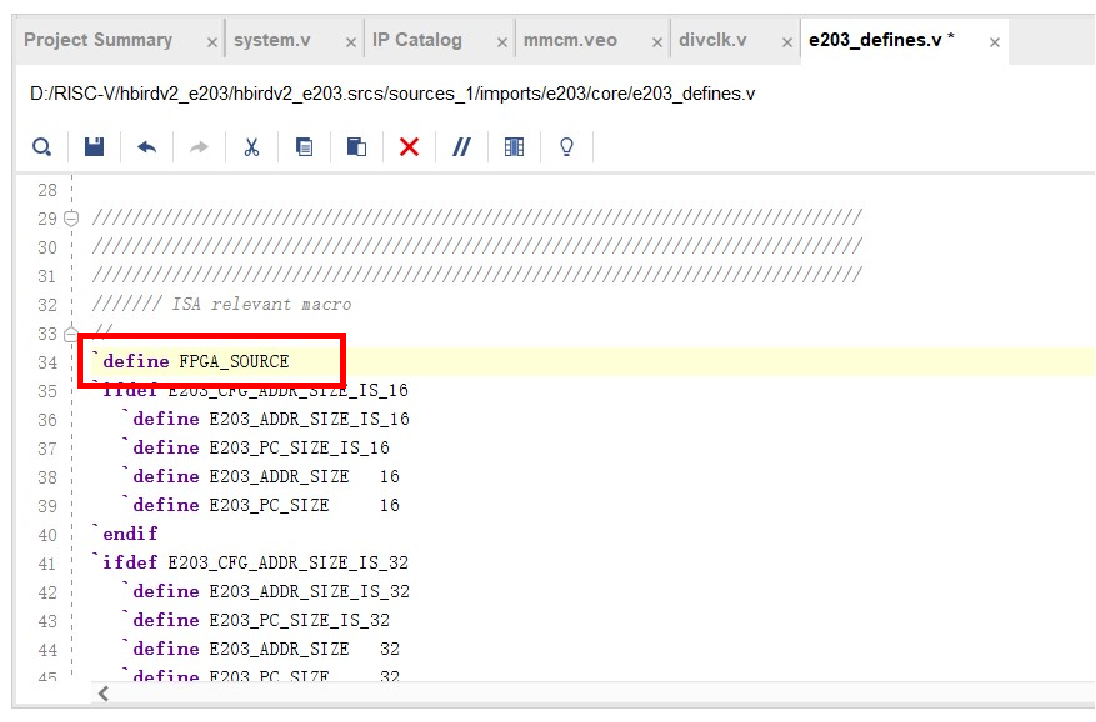

11.修改頂層定義檔案:

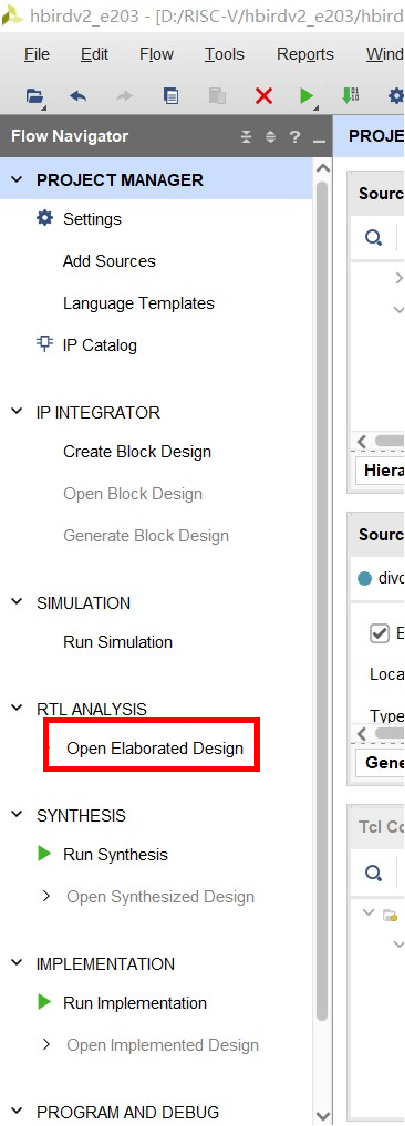

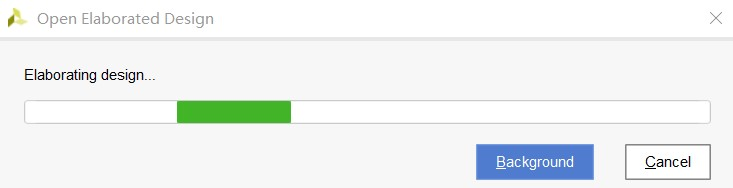

右鍵單擊e203_defines.v,將其設為global define,並在其檔案頭新增語句:`define FPGA_SOURCE。完成後檢視Elaborated Design,若此時報錯無法開啟e203_defines.v檔案,可以在SourceFileProperties中將其對應檔案型別改為Verilog Header

12.完成管腳約束:

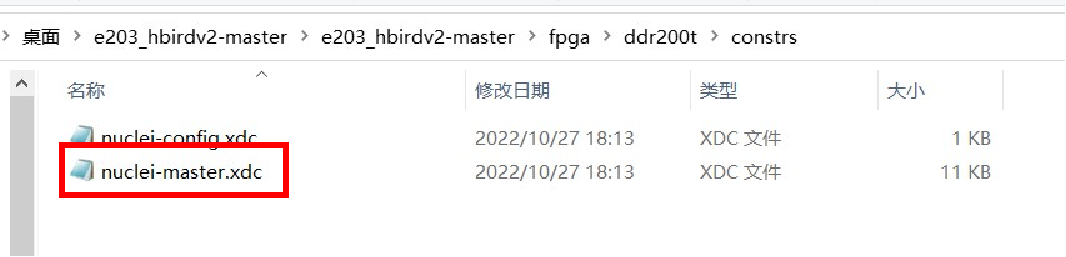

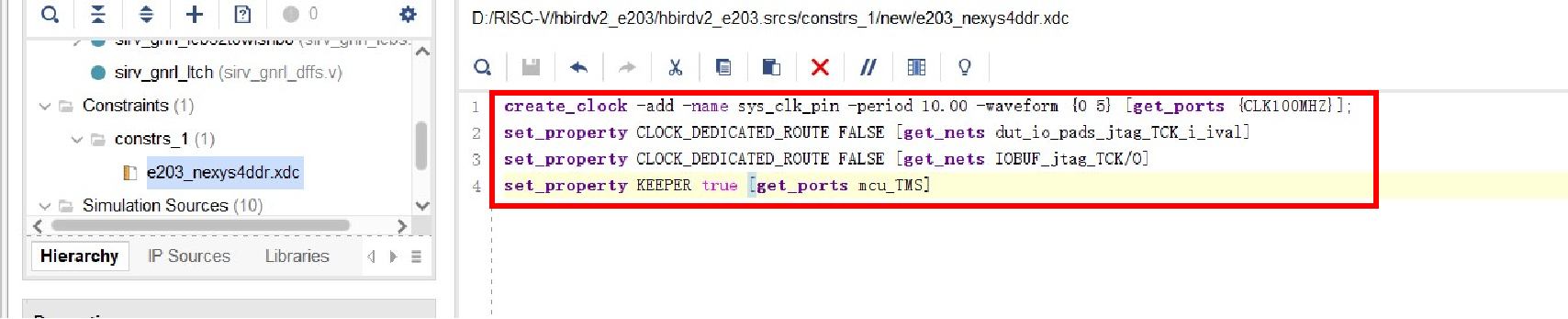

這裡提供資料有Nexys4DDR的電路原理圖及其約束檔案模板,可據此對時鐘管腳,SPI引腳,PMU引腳等必要的引腳進行一定約束來簡單驗證我們能否移植成功。對於管腳約束的完成,我們可以劃分成兩個模組:xdc約束檔案的編寫、system.v頂層檔案的對應修改。

- xdc約束檔案的修改: 主要模組包括:時鐘生成及引腳繫結、電源PMU、SPI、JTAG偵錯,也就是說只要保證了這四個基本模組的引腳約束,就能夠實現最基礎核心的移植,後續外設的新增可以再自行修改,這裡給出約束程式碼範例如下:

# Clock signal

set_property -dict {PACKAGE_PIN E3 IOSTANDARD LVCMOS33} [get_ports CLK100MHZ]

# set_property -dict { PACKAGE_PIN F15 IOSTANDARD LVCMOS33 } [get_ports { CLK32768KHZ }];

create_clock -period 10.000 -name sys_clk_pin -waveform {0.000 5.000} -add [get_ports CLK100MHZ]

# set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets dut_io_pads_jtag_TCK_i_ival]

# set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets IOBUF_jtag_TCK/O]

# Reset

set_property -dict {PACKAGE_PIN C12 IOSTANDARD LVCMOS33} [get_ports fpga_rst]

set_property -dict {PACKAGE_PIN M18 IOSTANDARD LVCMOS33} [get_ports mcu_rst]

# QSPI interface

set_property -dict {PACKAGE_PIN K17 IOSTANDARD LVCMOS33} [get_ports {qspi0_dq[0]}]

set_property -dict {PACKAGE_PIN K18 IOSTANDARD LVCMOS33} [get_ports {qspi0_dq[1]}]

set_property -dict {PACKAGE_PIN L14 IOSTANDARD LVCMOS33} [get_ports {qspi0_dq[2]}]

set_property -dict {PACKAGE_PIN M14 IOSTANDARD LVCMOS33} [get_ports {qspi0_dq[3]}]

set_property -dict {PACKAGE_PIN L13 IOSTANDARD LVCMOS33} [get_ports qspi0_cs]

# JTAG connection

# set_property -dict { PACKAGE_PIN E13 IOSTANDARD LVCMOS33 } [get_ports { mcu_TDO }];

# set_property -dict { PACKAGE_PIN E10 IOSTANDARD LVCMOS33 } [get_ports { mcu_TCK }];

# set_property -dict { PACKAGE_PIN E11 IOSTANDARD LVCMOS33 } [get_ports { mcu_TDI }];

# set_property -dict { PACKAGE_PIN E12 IOSTANDARD LVCMOS33 } [get_ports { mcu_TMS }];

# pmu_wakeup

set_property -dict {PACKAGE_PIN H17 IOSTANDARD LVCMOS33} [get_ports pmu_paden]

set_property -dict {PACKAGE_PIN K15 IOSTANDARD LVCMOS33} [get_ports pmu_padrst]

set_property -dict {PACKAGE_PIN N17 IOSTANDARD LVCMOS33} [get_ports mcu_wakeup]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.SPI_FALL_EDGE YES [current_design]

-

system.v中對應檔案的修改:頂層模組中程式碼功能劃分十分規整,對於不需要的模組如GPIO等直接註釋掉即可。

-

如恰好我們移植的是同一塊板子,那麼恭喜你,我已經在資料包裡準備好了兩份檔案,直接匯入工程即可