微機原理與系統設計筆記6 | 記憶體系統設計

-

打算整理組合語言與介面微機這方面的學習記錄。本部分介紹記憶體及其擴充套件方法。

-

參考資料

- 西電《微機原理與系統設計》周佳社

- 西交《微機原理與介面技術》

- 課本《組合語言與介面技術》王讓定

- 小甲魚《組合語言》

1. 記憶體的分類

-

外存:磁碟、U盤、光碟等,外存嚴格來說屬於IO裝置。

順序記憶體和隨機記憶體:讀寫資料的方式不同。

-

記憶體:本文主要講記憶體。

-

唯讀記憶體:存放系統管理程式,比如計算機主機板ROM裡的BIOS程式。

-

ROM:一次性寫,唯讀。

-

PROM:一次性可程式化、唯讀;

每個新的晶片為空片:如果以位元組為單位,則為FFH。

-

EPROM:常用,紫外線可擦除ROM,藉助專用寫入器可以將程式寫入(寫入的時候要先擦乾淨)。

目前常用型號:2716(2K乘8位元組==2KB),2732,2764,27128。

後兩者目前常用。

-

E2PROM:電可擦除ROM。可以反覆寫入,先擦除乾淨後寫,且掉電後資訊不丟失

常用是28系列。

-

-

隨機讀寫記憶體RAM:能讀能寫,但是掉電後資訊丟失。

-

SRAM:靜態,像暫存器/鎖存器。

常用型號6264(8k×8bit==8KB)、62128、62256、2114(1K乘半位元組,需要用兩個2114併成一個位元組--位擴充套件)

-

DRAM:動態,像電容,存1相當於給電容充電,所以需要反覆給DRAM上電重新整理(讀出來再寫入,重新整理週期要滿足一定條件,太長就不能讓系統辨認原有資料了)。

應用DRAM需要設計地址重新整理電路,而這個重新整理電路很複雜,所以自己設計系統一般使用SRAM。

DRAM整合度更高(雖然較於SRAM速度慢一點點),而計算機使用的都是DRAM。

本章主要是記憶體中ROM和SRAM的設計。

-

-

-

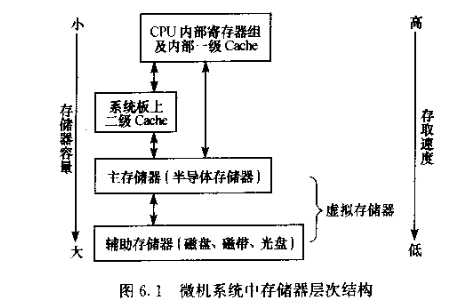

從結構角度的分類/微機系統中記憶體的層次結構:

2. 記憶體主要技術指標

-

容量

如果要設計32KB,62256(32K乘8bit==32KB)需要1片,2114需要64片

這裡儘量選擇接近的晶片來做,比如2114的話佔用面積大且對電源要求高。

-

速度

-

存取時間:啟動一次記憶體操作到完成此次操作的時間

-

儲存週期:兩次獨立的記憶體單元操作的最小時間間隔

可以從半導體公司手冊查到。

-

要求:(針對8086讀寫週期需要4個clk週期這一點)

下面的公式應該不會考,瞭解吧:

-

記憶體晶片的最小讀出時間:\(t_{cyc}(R)<4T-t_{da}-t_D-T\)

- T:8086時鐘週期

- tda:8086的地址匯流排延時時間

- tD:各種因素引起的匯流排附加延時。匯流排長度、附加邏輯電路、匯流排驅動器等之和、

減去一個T是因為工程上的要求。

-

記憶體晶片的最小寫入時間:\(t_{cyc}(W)<4T-t_{da}-t_D-T\)

-

-

-

儲存頻寬:單位時間傳輸資料容量的大小。

頻寬(B,MB/s)==記憶體時脈頻率(F,MHZ)*記憶體資料匯流排位數(D)/8

\(B=F\times D/8\)

-

非易失性:是選擇ROM還是RAM。

-

可靠性:平均故障時間間隔。

-

功耗、成本等

3. 幾種常用記憶體晶片介紹

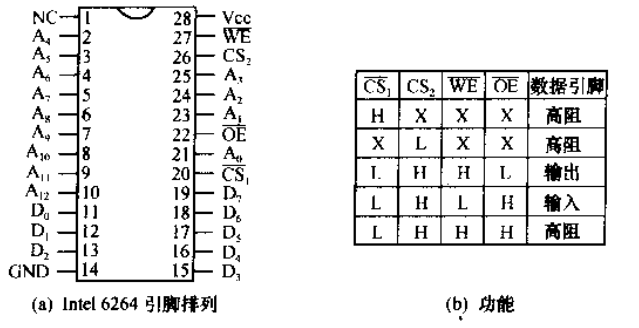

3.1 SRAM 6264

8K×8bit,有13根地址線(編碼8k),資料引腳8根(引腳8bit),此外還需要片選訊號。

6264有兩個片選訊號CS1fei和CS2:

- CS2高電平,CS1fei低電平則為選中。根據13根地址線選中的單元進行寫或讀操作

- 未選中則8根傳輸線呈現高阻態,與系統匯流排隔離。

- 也可以將CS1常接+5V來改造為單片選。

還有一個輸出允許腳OEfei,片選有效且輸出允許有效時,可以輸出資料。一個寫允許腳WEfei,與片選結合可以寫入資料。

注意不能同時寫或讀。OE和WE只能一個有效。

與8088CPU的地址匯流排結合起來來看,則8086的低13位地址線A12A0直接定址6264內部,這叫片內定址;而高位地址線A19A13,片外定址,也就是決定是1MB的哪一個8KB,引出譯碼作為控制訊號,作為片選訊號。這一點比較好理解。

注意這裡8088沒有奇偶地址的概念,比較簡單。

8086CPU的地址匯流排。則A1A13來片內定址,A0決定是奇還是偶地址,高位A14A19片外定址。

- 如果A0=0,則取出A13~A0的16KB位元組的8K偶位元組,與系統資料匯流排的低8位元相連。

- A0=1,則取出A13~A0的16KB位元組的8K奇位元組,與系統資料匯流排的高8位元相連。

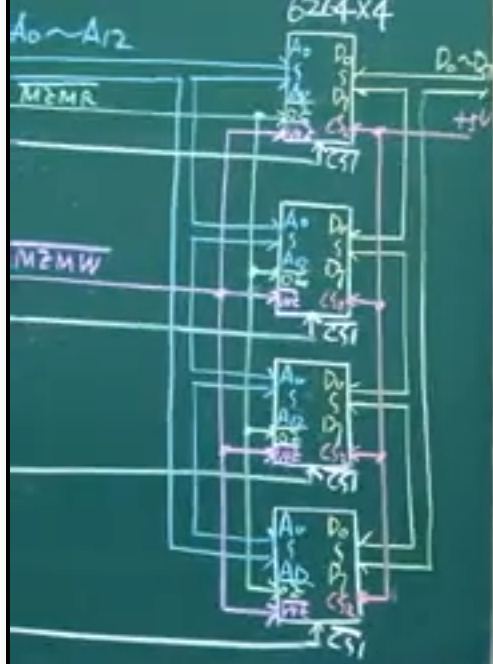

而如果用6264給8088微機系統設計32KB的SRAM:

- 需要4片

- 地址線對聯8088地址線,傳輸線也對聯。

- 使CS2常有效

- OEfei,讀允許。在最大方式下,與MEMRfei相連;最小方式下,與RDfei相連。

- WEfei,寫允許。最大方式下,與MEMWfei相連。最小方式下,與WRfei相連。

- CS1fei片選訊號。地址線的高位(接入譯碼電路產生控制訊號,再接過來片選。

上述思路是位元組擴充套件,P198 6.4.2

注意譯碼電路不僅是地址,還有控制訊號。比如8088最小方式中有IO/Mfei,表示對記憶體操作。

這裡實際只需要兩位A13和A14來選擇晶片塊,同時也可以再加上其他不變的高位地址線,參與譯碼

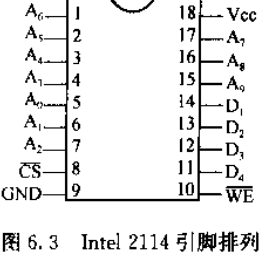

3.2 SRAM:Intel 2114

1K×4bit。有10根地址線,4位元傳輸線。

- CSfei,低電平選中

- WEfei,管理讀寫,低電平寫入記憶體,高電平輸出。

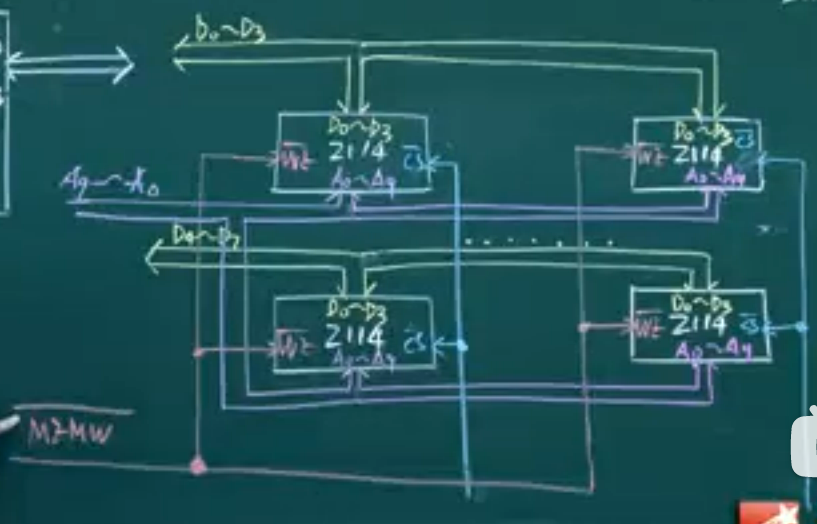

使用2114給8088系統擴充4KB儲存系統:

-

需要8片

-

先兩兩相併位擴充套件,再串聯位元組擴充套件。

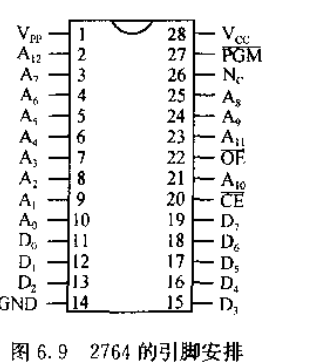

3.4 EPROM 2764

8K×8,所以13根地址線,8根傳輸線

- CEfei:片選訊號

- OEfei:片選有效且低電平,讀出資料(也就是唯讀狀態)

- VCC:工作電壓

- VPP:程式設計電壓輸入,需要查公司型號手冊

- PGMfei:低電平(負脈衝),程式設計允許引腳

要對2764先擦除後寫入資料:

-

擦除。

-

OEfei無效,CEfei有效。

-

不是直接接到地址線和傳輸線,兩邊各需要一個鎖存。將地址和資料都鎖存起來

-

當上層命令來到,VPP電壓加上,PGM加負脈衝,在這個負脈衝期間,鎖存也解除,向選中地址寫入相應資料

-

CE OE有效,將寫入的資料讀出(無鎖存器的通道),比較是否符合預期,如果符合,則寫入完成。

如果不相等,可重新操作,如果多次操作不行,可能地址單元損壞。

hhh,學了這個可以做程式設計器了...

2764的正常工作/唯讀模式:

- 只需要考慮地址(奇偶等等)、資料(單向輸出)、CE片選訊號、OE連線MEMRfei,不考慮VPP和PGM(接+5V即可)

4. 記憶體擴充套件設計

4.1 記憶體地址譯碼方法

- 全地址譯碼方法:全部地址線來譯碼,浪費硬體設計資源(因為地址線都要引過來),但是可以唯一確定一個儲存單元的地址。

- 部分地址譯碼方法:譯碼電路簡單,但會發生地址空間重疊。

例題見書P200 6.1

4.2 8088系統記憶體擴充套件

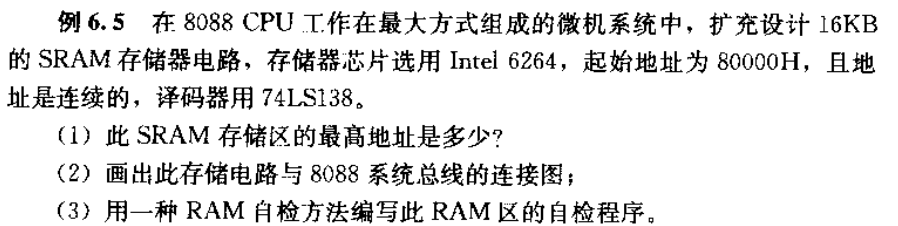

P205 例6.5

-

第一題,簡單,16KB為2的14次方,16進位制是4000H,地址範圍就是80000H~83FFFH

-

第二題:

-

進行地址分析:

- 需要兩片6264

- 低13位片內選址,A13選擇兩片之一

- A19~A14六根線,在此題不變,且為10_0000

- 這樣就保證了連續地址。

-

邏輯電路(不用型號):

- 需要加入控制訊號,表明是對記憶體操作。

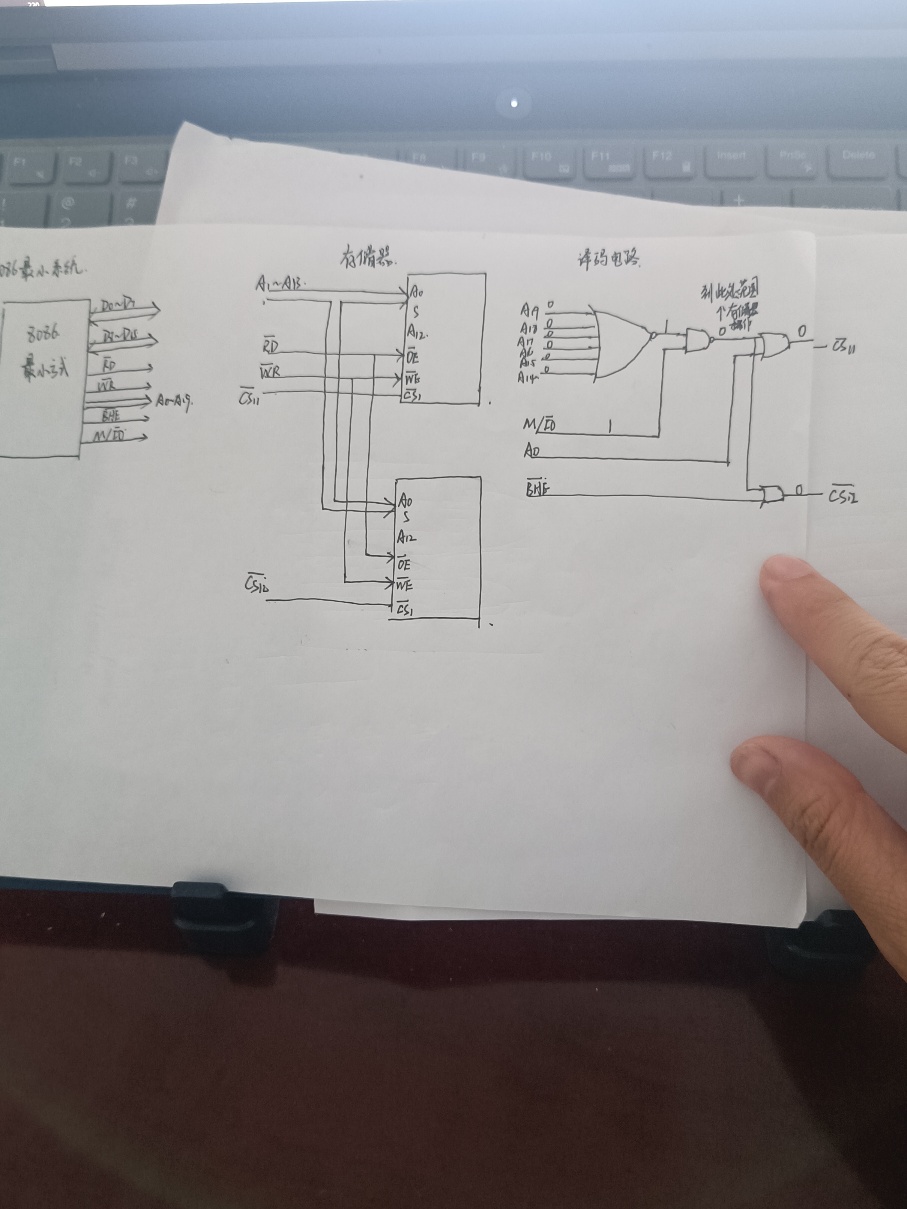

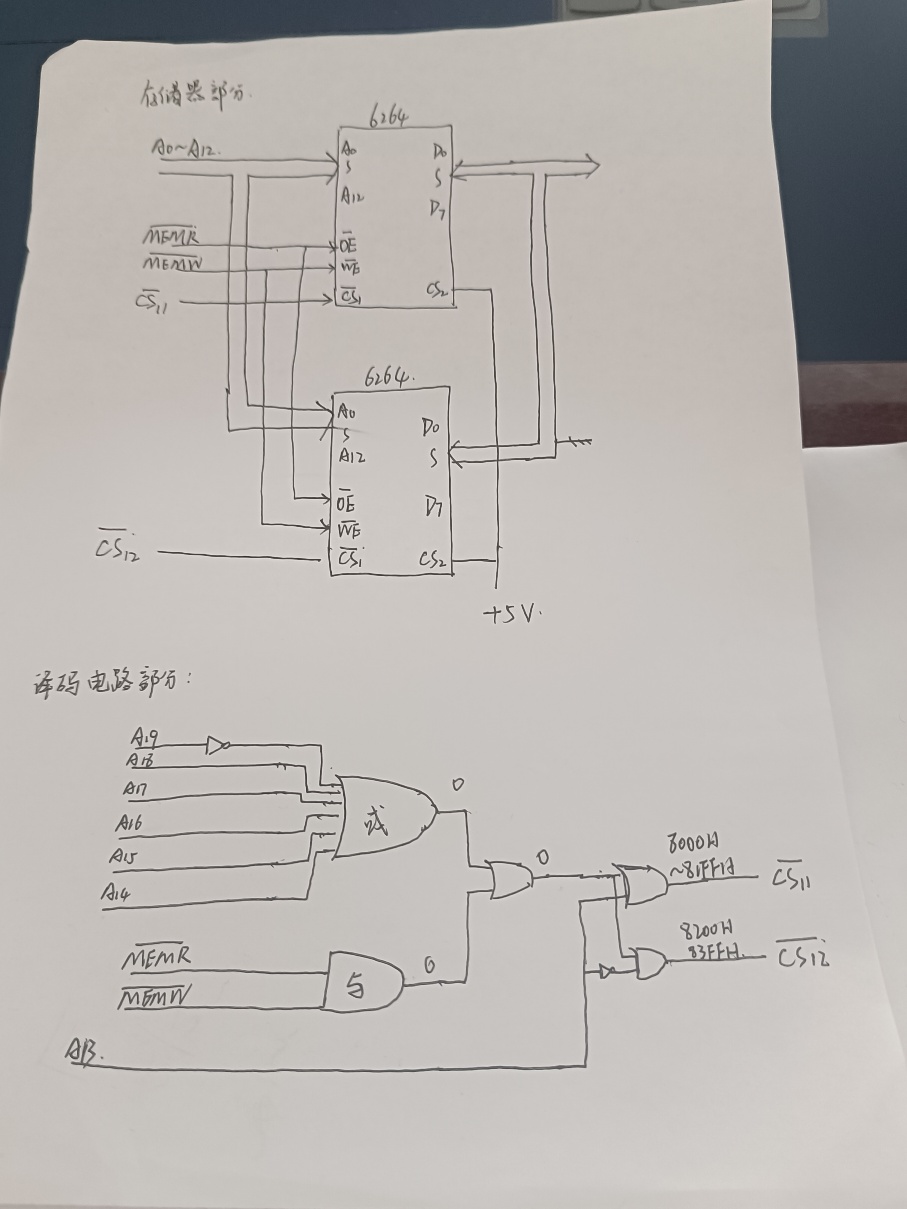

整體設計如下圖所示:

如果使用74LS138來做譯碼器(這個我沒有學,跟上圖原理相同,只不過封裝了一些東西)

-

-

第三題:用到一點點組合知識。這裡55H和AAH資料圖案檢測,給要檢測的RAM儲存區每個地址單元分別寫入55H(0101_0101)和AAH(1010_1010),並讀出比較是否符合預期,如果符合,則讀寫正常。如果不正常,則應作出相應出錯報警提示。

MOV AX,8000H MOV DS,AX MOV SI,0 MOV CX,16*1024 MOV AL,55H NEXT1: MOV [SI], AL MOV BL, [SI] CMP BL, AL JNE ERROR ;不相等則轉到ERROR INC SI ;地址增加繼續比較 LOOP NEXT1 MOV SI,0 MOV CX,16*1024 MOV AL, 0AAH NEXT2: MOV [SI],AL MOV BL,[SI] CMP BL,AL JNE ERROR INC SI LOOP NEXT2 ... ERROR: ...- 傳輸線粘連故障:檢測思路就是55H和AAH

- 地址線鏈橋故障:先把記憶體刷成00H,然後向00H處寫入01H,檢測其他地址單元是否改變,00H地址單元左移為02H,看其他地址單元內容是否改變......這樣就可以找出地址線粘連發生的不同地址內容的重寫問題。

- BIOS中自檢就是排除這些故障,程式會更加豐富。

4.3 8086系統記憶體擴充套件

擴充套件原理基本相同,相較於8088,多的是奇偶地址的片選:

- 上圖沒有體現出來的是,A0和BHEfei還要跟相應控制訊號一起進行邏輯運算才行,比如最大方式下MEMRfei、MEMWfei和M/IOfei,最小方式下RDfei、WRfei和M/IOfei

- 此外512k的晶片上還應有CE和OE,分別是

- CEfei:片選訊號,

- OEfei:讀允許

- WEfei:寫允許

P208 例6.6:

-

上圖改為74LS138,但這個器件我不總結了,我沒學。

-

設計圖如下圖所示:

-