微機原理與系統設計筆記1 | 緒論與數製表示

- 打算整理組合語言與介面微機這方面的學習記錄。

- 參考資料

- 西電《微機原理與系統設計》周佳社

- 西交《微機原理與介面技術》

- 課本《組合語言與介面技術》王讓定

- 小甲魚《組合語言》

1. 介紹

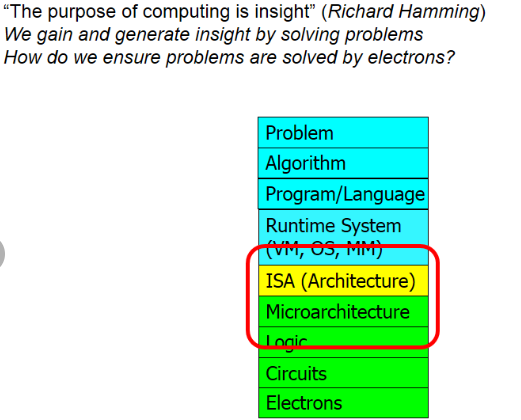

2022年春學習了MIPS視角下的電腦架構與組成原理,同年夏自學了作業系統(科普級別的瞭解),組合語言是學習作業系統的時候,基於學過的計組強行吃下來的,並沒有單獨學過。

秋天學學校的OS(比較深入),同時我也報了組合語言與介面技術這門選修課。在這門選修課上我感覺組合相關內容還是十分豐富的,並且在系統、底層、安全這些方面用處很多。

這個系列是對這方面知識的整理。打算在這個系列的最後進行課程內容的複習。

2. 概覽

課程10章,前四章為組合語言,後6章為微機硬體介面電路。

2.1 電子資訊系統

-

有了CPU的電子資訊系統功能更為豐富。

-

電子資訊系統的輸入是物理量

-

物理量轉化為電量:感測器

轉化後的電量為 mv 級

-

電量放大並濾波:前端調理電路

模電課程(本人不學),到伏特級,留偵錯點。

-

模擬訊號到數位訊號:A/D轉化

可以根據需求選擇A/D晶片轉化的精度和速度。

-

數位訊號提交給CPU處理:CPU型號也是根據需求選擇。

-

CPU應當可以向A/D轉化器件和前段調理電路傳送控制訊號,控制一些處理速度。CPU處理後的數位訊號應有記憶體儲存。

-

需要輸出的數位結果:D/A轉化

-

與前端調理對稱地,需要後端調理電路,其輸出量來控制外部器件/裝置;

實驗時這裡後端調理結束後通過測試點引出到示波器了。

-

另一些應用場合,輸出要顯示(電視機)、列印(印表機)。

我們需要給CPU程式設計序(組合語言),來決定整個系統怎麼工作,這就是前4章的主要內容。不同的I/O裝置的型別也有差異,裝置接受資訊的格式不同(如序列並行、模擬量數位量),所以CPU和裝置之間要設計一段介面電路,這是後半部分硬體部分的內容(時序、記憶體、I/O裝置介面)。

2.2 微型計算機系統組成

A. 軟體子系統

不是本課程的講解內容。也可以簡單再分為系統軟體和應用軟體。

B. 硬體子系統

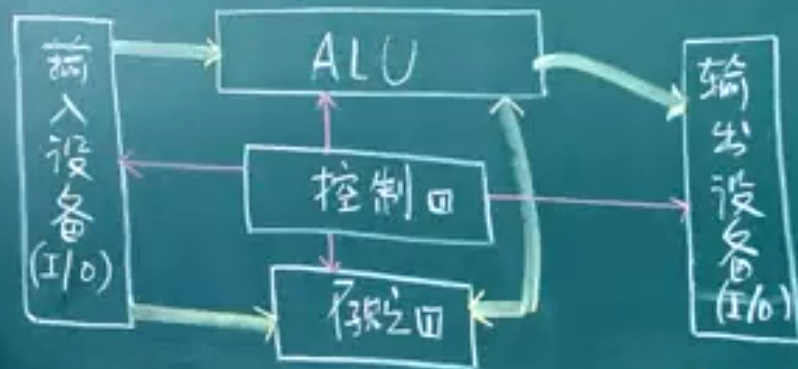

早期計算機硬體組成

控制器控制ALU運算:ALU運算的資料在控制器控制下送往記憶體;

記憶體中的資料被控制器控制器送到ALU;

輸入裝置(IO)控制器控制輸入裝置輸入資料到記憶體或ALU。

-

隨著積體電路發展,將ALU和控制器整合在一起,成為中央處理器CPU(也稱微處理器)。

-

上述部件之間傳遞資訊:

-

資料資訊、控制資訊、地址資訊

(這點很好理解)

-

對應的傳送資訊的線/通道:資料匯流排、控制匯流排、地址匯流排。

-

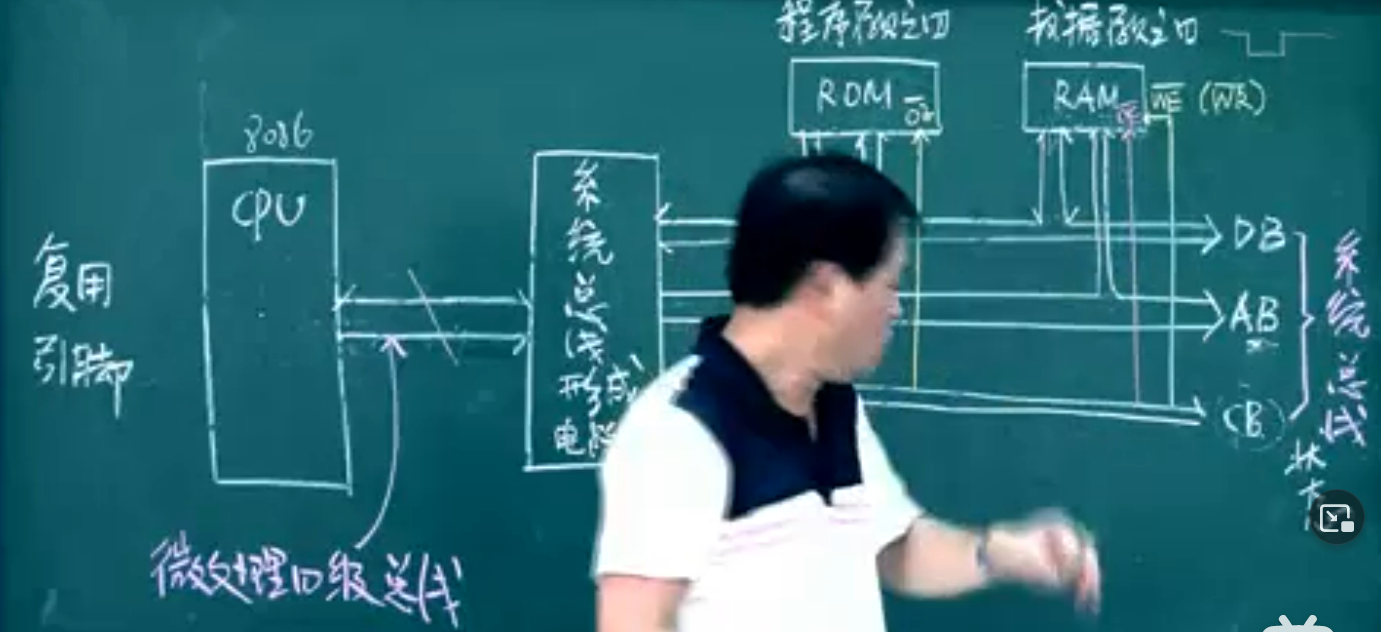

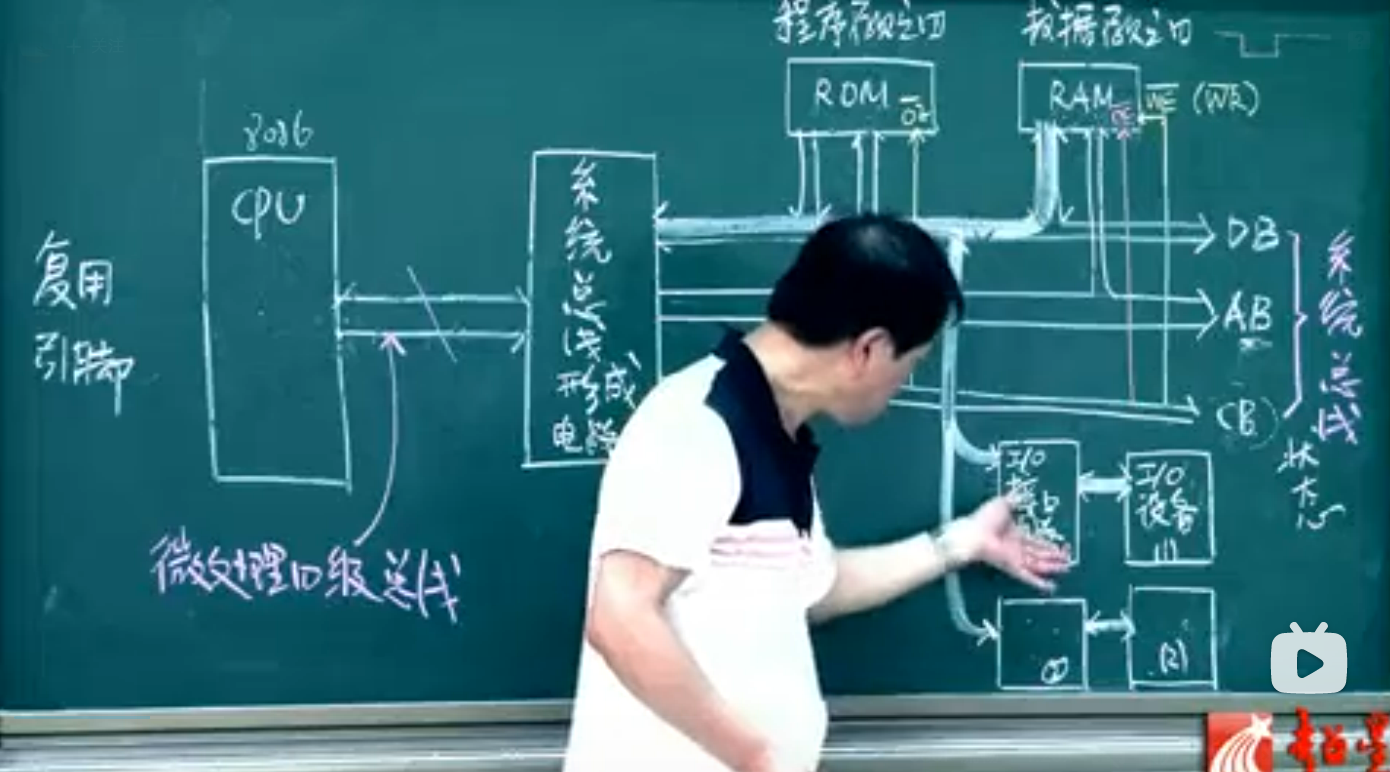

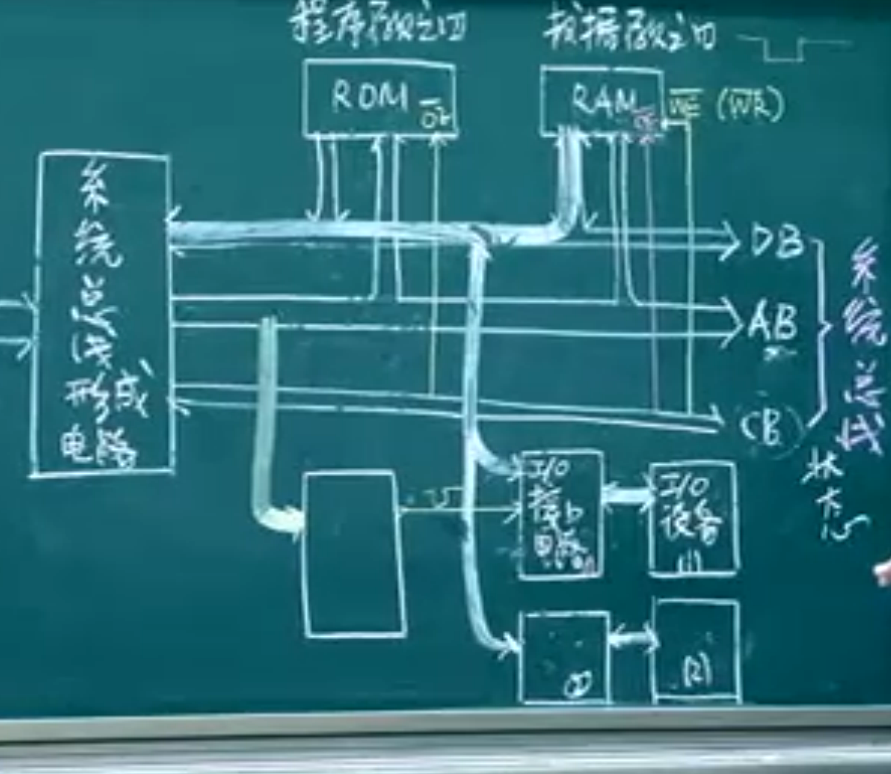

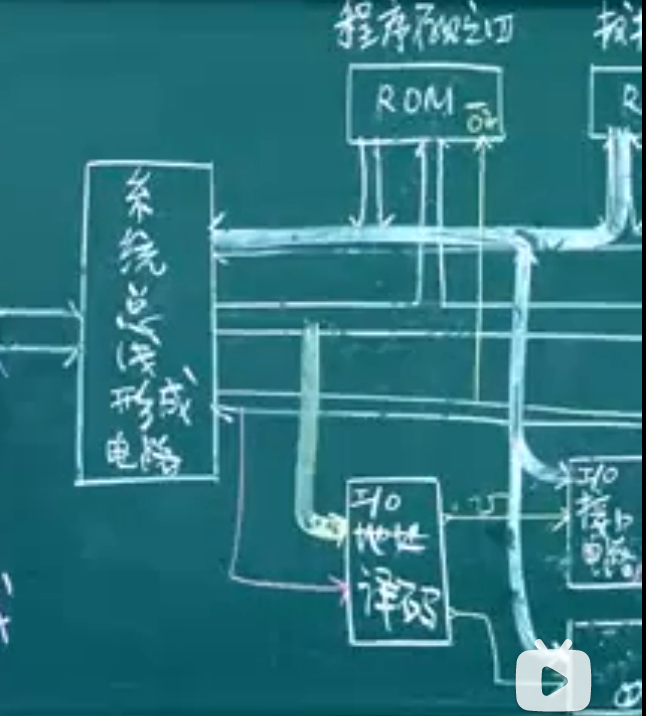

現代微型計算機硬體組成

-

以微處理器/CPU為核心來組成。CPU通過引腳來跟外部記憶體、I/O實現地址、資料、控制資訊互動。而8位元CPU8個引腳,16位元CPU16個引腳,是無法同時滿足三條匯流排分開接入的。

8086CPU有16根資料匯流排,20條地址匯流排和16條控制匯流排。

-

因此實現了一種分時複用技術,部分引腳分時複用。

因此需要設計一個電路(系統匯流排形成電路),鑑別複用的部分引腳此時到底輸出/入的是什麼資訊,並輸出輸入。

要想設計這個電路需要了解CPU引腳的時序(第五章)。

引腳也稱微處理器級匯流排。

轉化後形成的三匯流排稱為系統匯流排。外設就掛接在系統匯流排上。

-

CPU具體如何與外設互動:

- CPU要給記憶體寫資料,需要通過CPU的寫控制引腳傳送寫控制命令,同時傳送地址資訊,寫入對應地址,控制匯流排還要接收外設的狀態資訊。

-

硬體子系統中的儲存子系統,由ROM和RAM組成。對於內部不含儲存電路的CPU電子系統而言,必須用這兩樣ROM和RAM,在三匯流排上擴充套件設計記憶體。

計組實驗匯流排資訊這裡講挺清楚的,組合與介面這課詳細講了怎麼設計記憶體。

ROM又稱程式記憶體,用專用裝置寫入,接入系統電路時是唯讀的。

2.3 組合簡介

指令的概念

- 指令是一組二進位制程式碼。用於明確指示上述系統中CPU的工作。組合語言是二進位制程式碼的符號化描述。

2.4 介面簡介

前面提到了,I/O裝置不會直接接到CPU上,要通過一段介面電路來完成標準化並與CPU連線。

介面電路也就是常說的介面。

I/O介面是連線CPU和I/O裝置的控制電路。比如顯示器與CPU之間通訊有顯示卡電路,音響與CPU之間有音效卡。

當然,CPU要想向I/O裝置讀寫資料,需要地址來引導。這就提出了I/O介面地址。這是為I/O裝置對應的I/O介面電路分配的地址,這就完成了從介面電路進行讀寫操作到從介面地址進行讀寫操作的轉化。

這一點跟記憶體的轉化是相通的。

這裡有一個問題,如何對I/O介面編址?

-

8086系統中,是通過地址線來統一編址。即既編址記憶體地址,也編址I/O介面。這時讀寫記憶體和I/O的指令相同。

當然,對於記憶體地址空間和I/O地址空間,也有很多微處理器採用兩個獨立地址空間。這時儲存單元地址和I/O埠的地址值可能相同,所以需要採用記憶體讀寫訊號和I/O讀寫訊號來區分。這樣CPU讀寫記憶體和I/O的指令是不同的。

-

對於一個I/O介面來說,地址碼通常只有一個,這裡需要設計一個電路來完成從16根地址線(16位元二進位制)+控制線上的有效位 到一個控制命令(高低電平0/1)的轉化。

其實也就是一個I/O地址譯碼器。這是數電/數位邏輯課的內容。

記憶體相應也有類似的結構。

這部分課程後續會再詳細介紹。

2.5 有關微機系統

上述硬體結構還不能工作,只是一個微型計算機,而不是微型計算機系統。需要配上I/O裝置、電源、軟體等,才能正常工作。

2.6 記憶體簡介

前面已經提到過很多次記憶體,這裡再簡單整理下。

記憶體有幾個要素,地址單元大小,地址號碼。一個地址單元內是一個位元組8bit=1byte。而地址號則決定地址單元的邏輯位置,地址線編碼了地址號,CPU通過地址線定址記憶體。所以大空間的記憶體也要求著地址線條數要多。

地址線和傳輸線寬度的區別:

傳輸線的寬度決定一次傳送的資料規模。

8086CPU傳輸線16位元,所以一次可以取兩個位元組的內容。

因此,兩個相鄰的地址單元(位元組),可以組成一個字單元(也就是16位元)。字分為高八位和第八位。

大端位元組序和小端位元組序。而8086系統是高位元組存放在高地址空間,低位元組存放在低地址空間。

讀/寫一個字時,讀/寫的地址是低位元組的地址號。

設計記憶體時我們需要對晶片進行相關組織而達到相關儲存要求。

3. 數制碼制快速複習

這部分各個課(C、數位邏輯、計組)都講,實在重複。

3.1 數制

-

程式設計中的二進位制->十進位制的一種方法:

-

除十取餘法

二進位制除十的二進位制,然後餘數變成十進位制,這樣就是十以內的轉化

-

比較法

後面組合部分會實現這裡的簡單轉換演演算法

-

-

程式設計中的十進位制->二進位制:

比如要從鍵盤輸入95,CPU中9*10得到的結果就是二進位制,再加5,得到的就是二進位制95.

這個想法根本原因是:CPU只認識二進位制。

mov AL, 96add AL, 89中的96、89就是二進位制的形式被CPU識別的。

3.2 二進位制算術運算

首先要搞清楚運算的物件是8位元二進位制(位元組)還是16位元二進位制(字)。

-

在現在大多數情況的組合語言中數位是十六進位制的, 如果最開頭的一位是A~F, 仍然要求在前面加零.

-

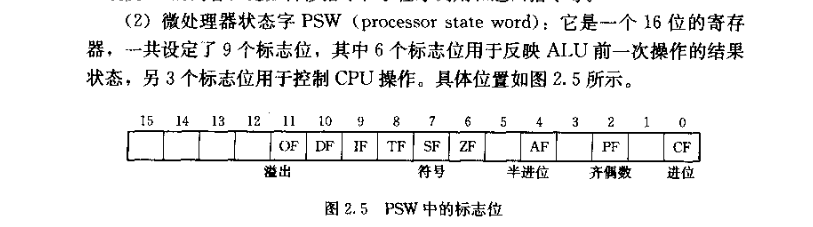

處理器狀態字暫存器/標誌暫存器:

只有運算才能影響標誌暫存器。包括下面的邏輯運算。

補充:

- PF是奇偶校驗,只看低八位,如果1個數為偶數則為1,奇數為0.可以用於資料序列通訊過程中的奇偶校驗的硬體實現。

- AF是輔助進位,管理四位間的進位借位,有進位為1。

3.3 二進位制邏輯運算

- 邏輯與 AND:

- 可以用於清零某些位,更寬泛說可以規範化資料(如作業系統中查頁表時的操作)

- 邏輯或 OR:

- 同上,規範化資料,將某些位置為1而其他位不變,置1的位為1即可。

- 互斥或 XOR:

- 這裡我經常記錯,兩運算物件對應位不同則為1,相同為0.

- 可以用於某些位取反而其他位不變,取反的位置為1即可。

3.4 表示範圍和溢位問題

- 無符號數表示範圍:

- 8位元:00H~FFH

- 16位元:0000H~FFFFH

- 有符號數表示範圍:

- 機器數表示法:0--正,1--負數

- 有符號數原碼:

- 符號位+正常二進位制表示

- 缺點,+0和-0的機器數表示並不同,這在計算機中是矛盾的

- 表示範圍:

- 8位元:+127+0,-0-127

- 16位元:+32767+0,-0-32767

- 有符號數反碼:

- 正數就是原碼

- 負數:符號數+原碼其餘位取反

- 有符號數二補數:

- 正數就是原碼

- 負數:反碼+1==符號位不變,原碼按位元取反+1

- 表示範圍:

- 8位元,+127~-128

- 16位元:+32767~-32768

- 計算機中用的就是二補數

最近遇到了一個C程式上的問題,從埠中拿出的狀態碼是char型別的,但是用char接收會溢位,所以向上適用int型別就會正常。

3.5 二補數的運算

公式1:[X+Y]補 = [X]補+ [Y]補

公式2:[X-Y]補 = [X]補- [Y]補

公式3:[X-Y]補 = [X]補+ [-Y]補

- 看結果時不看最高位溢位的(第九位),只看八位

- 公式三由公式2發展而來,思路更簡單,並且節省了硬體電路。

由二補數的運算結果(二補數)求原碼:對二補數求二補數(符號位不變,取反+1)。所以有公式4.

公式4:[X]=[X補]補

在上面公式3的情境中,需要實現一個操作:已知[Y]補,求[-Y]補。這時需要包括符號位在內全部取反,再加1。

3.6 BCD碼

用四位二進位制描述0~9十個十進位制數

-

對應關係

- 0000---0

- 0001---1

- ..........

- 1001---9

-

也稱8421碼

-

更復雜的表示

- 組合BCD數,兩個BCD碼放在記憶體的一個位元組中。

- 分離BCD數,兩個BCD碼分別放在兩個位元組的低四位,高四位為0.

- 加減法有以上兩種表示,而乘除只有分離BCD數。

-

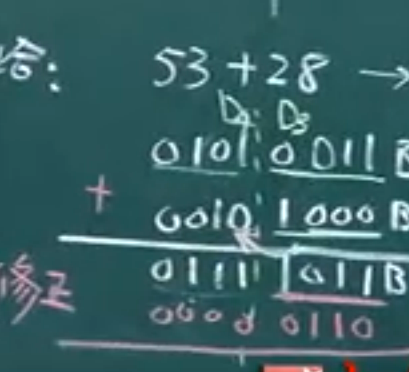

BCD碼的運算:主要是換算進位問題。

如下圖,53+28的運算中需要判斷是否超過9,如果超過9而未達16,需要+6強制轉化。

這時就用到了AF。

程式實現中

mov AL,53

add AL,28

DAA;如果設計BCD計算,+6調整

;如果是分離BCD,需要AAA指令

3.7 字元表示 ASCII碼

-

'0''9':30H39H

-

字元到數位轉化:-30H

-

'A''F':41H46H

- 字元到數位轉化:-37H

-

'a''f':61H66H

-

大小寫轉化:

;假設將AL中轉換為大寫 ;大寫和小寫僅在第五位有區別 ;;大寫:0100_xxxx ;;小寫:0110_xxxx AND AL,0DFH ;;由於第七位必然為0 AND AL,5FH ;AL中轉換為小寫 OR AL,20H

-