剖析虛幻渲染體系(19)- 計算機硬體體系

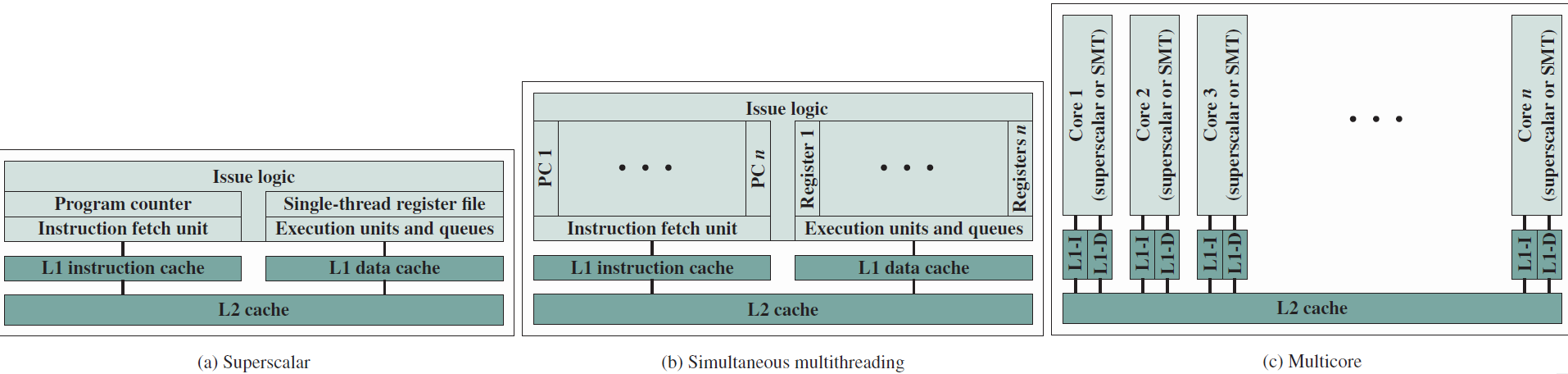

- 19.1 計算機概述

- 19.2 計算機硬體基礎

- 19.3 計算機架構和組織

- 19.4 ISA

- 19.5 處理器

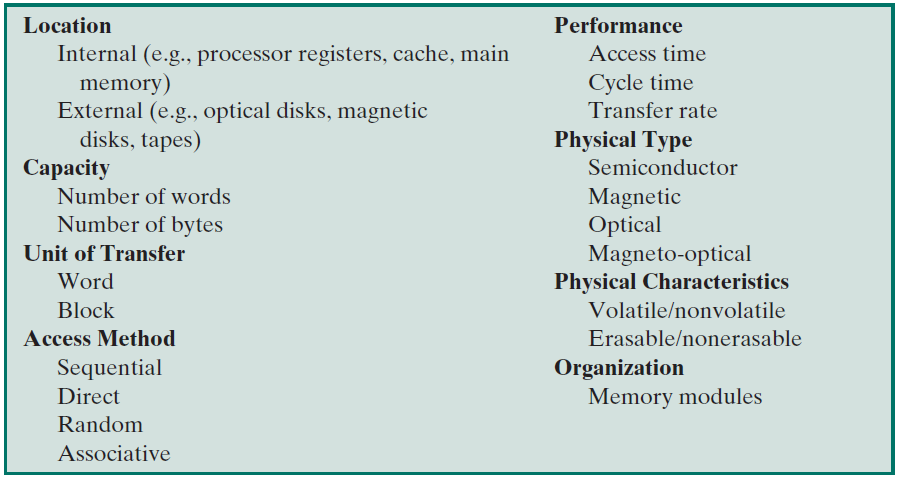

- 19.6 記憶體系統

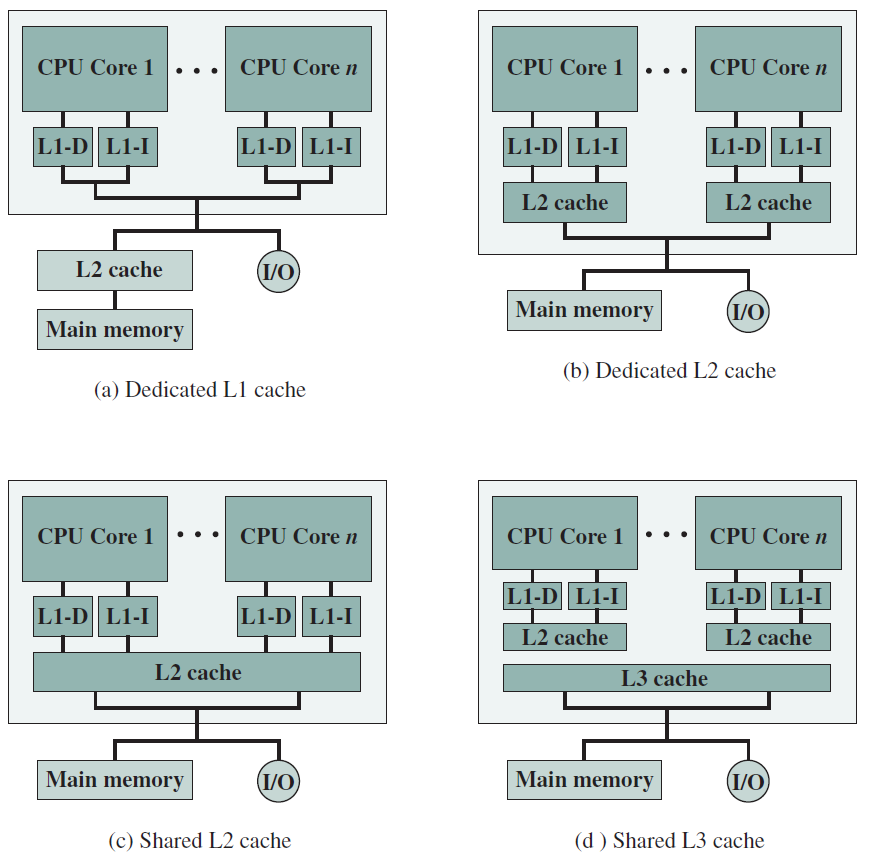

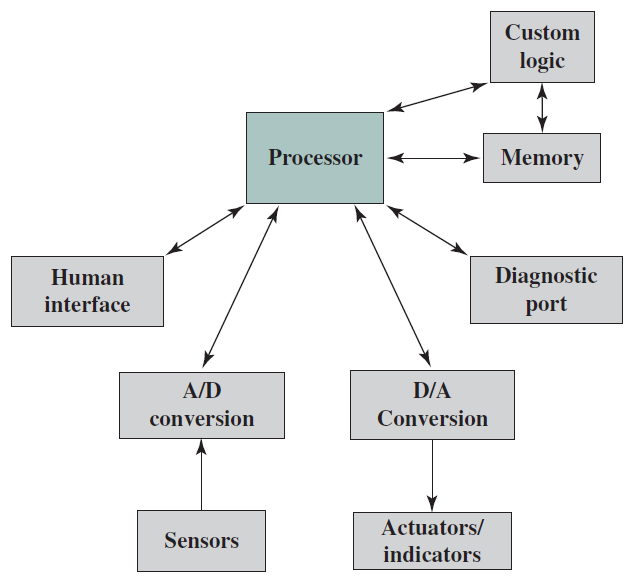

- 19.7 多處理器系統

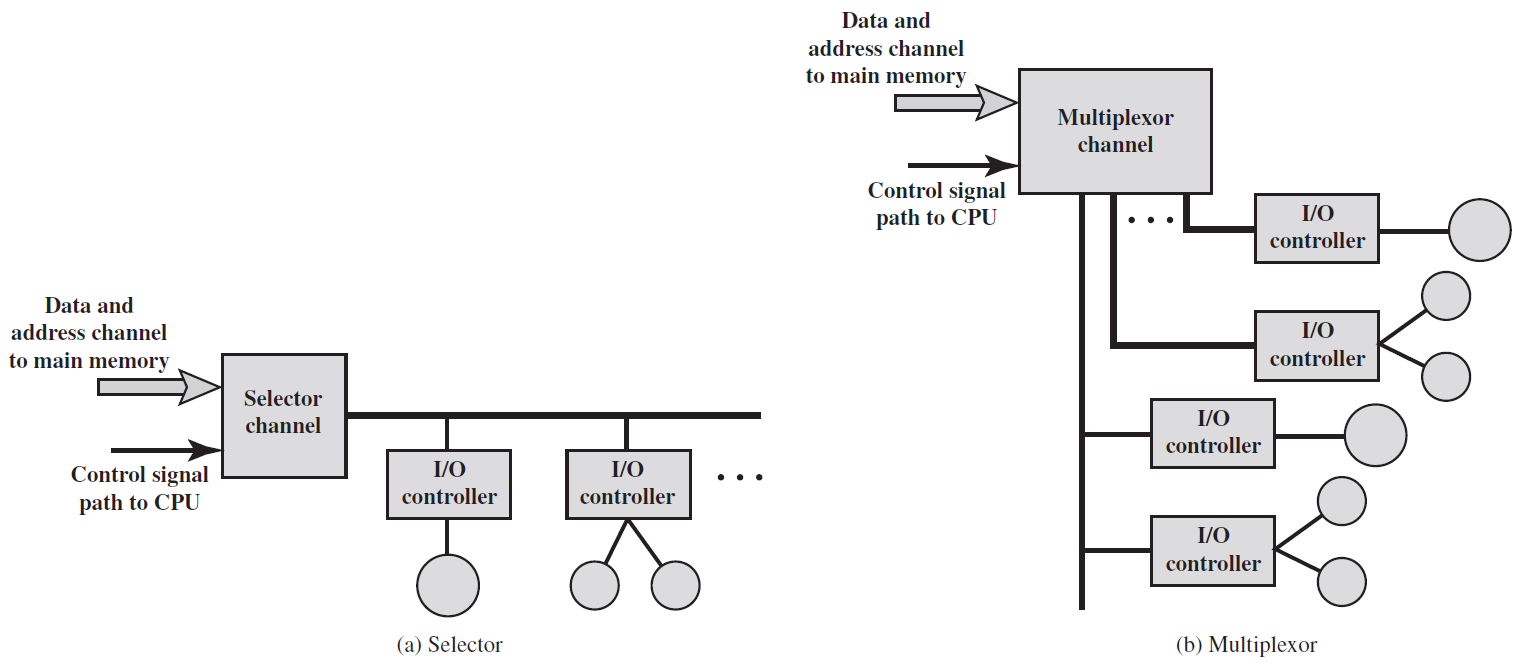

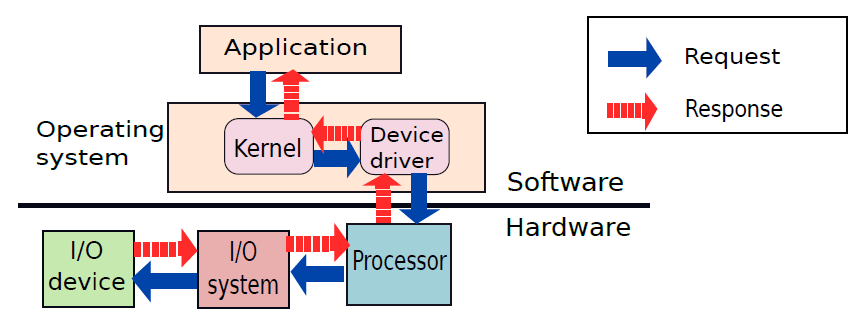

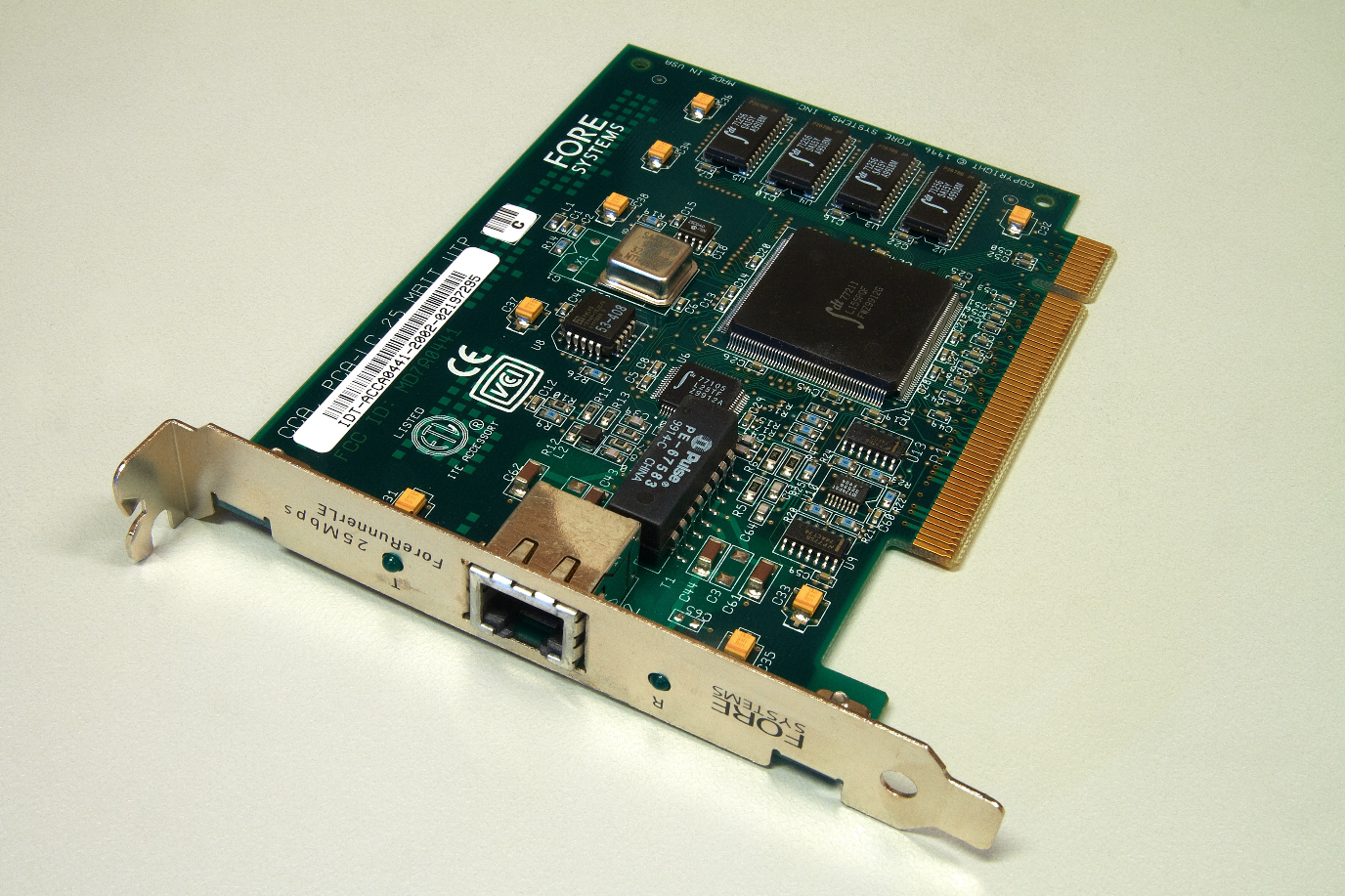

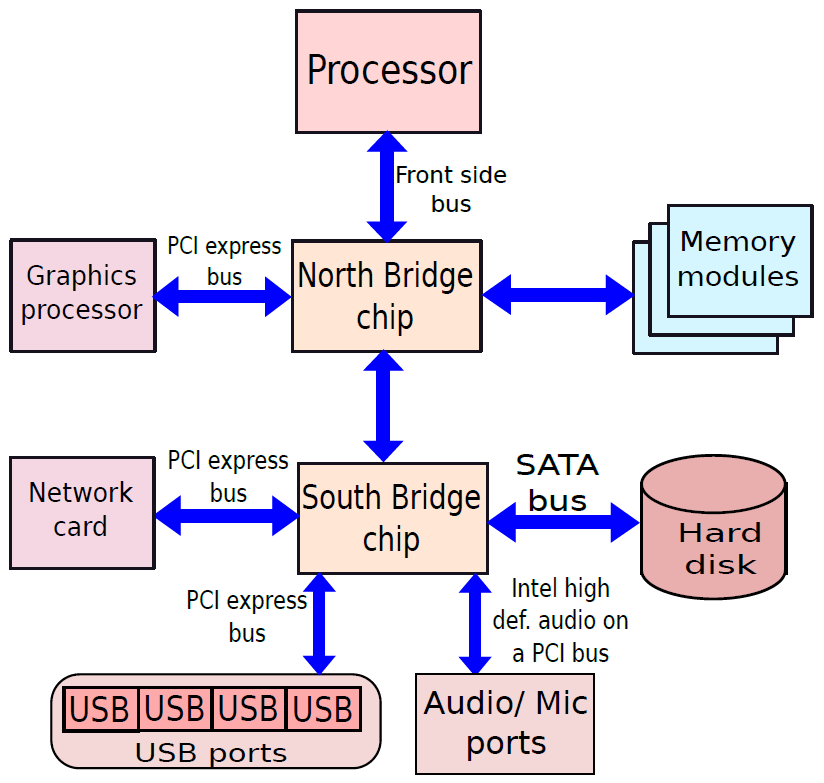

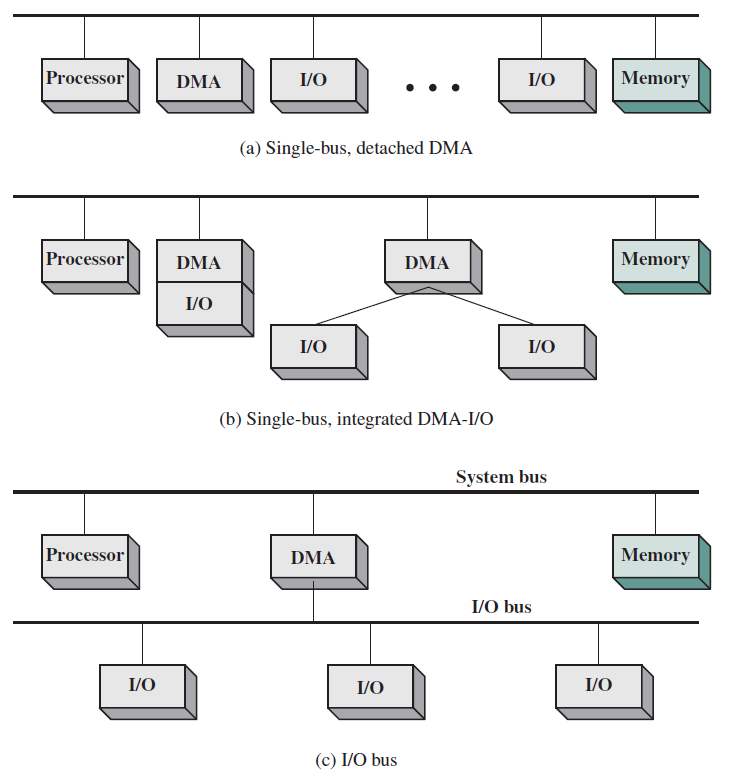

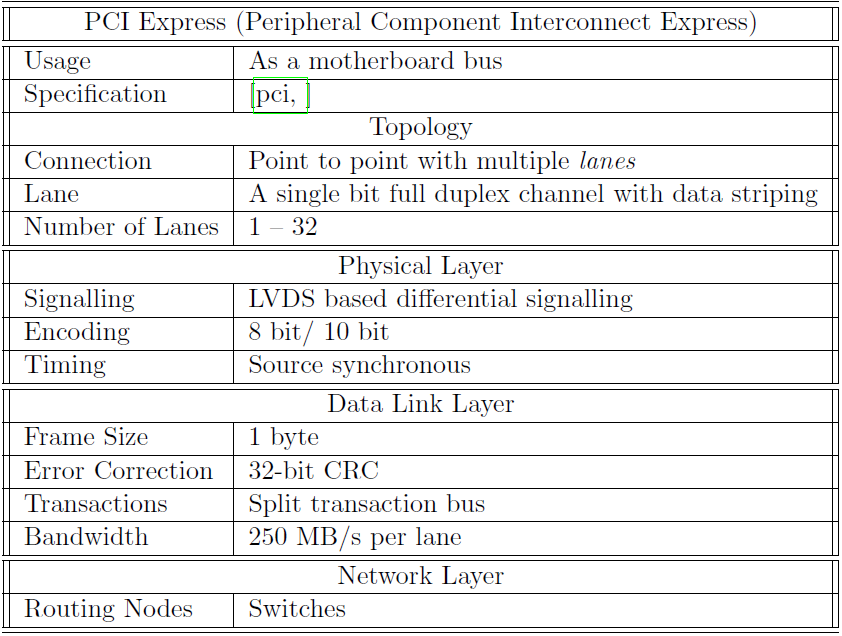

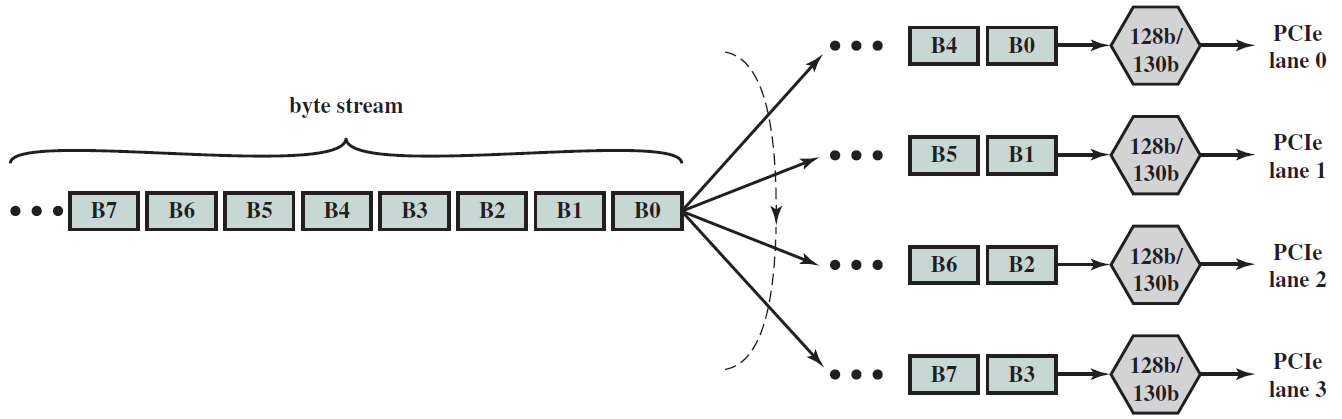

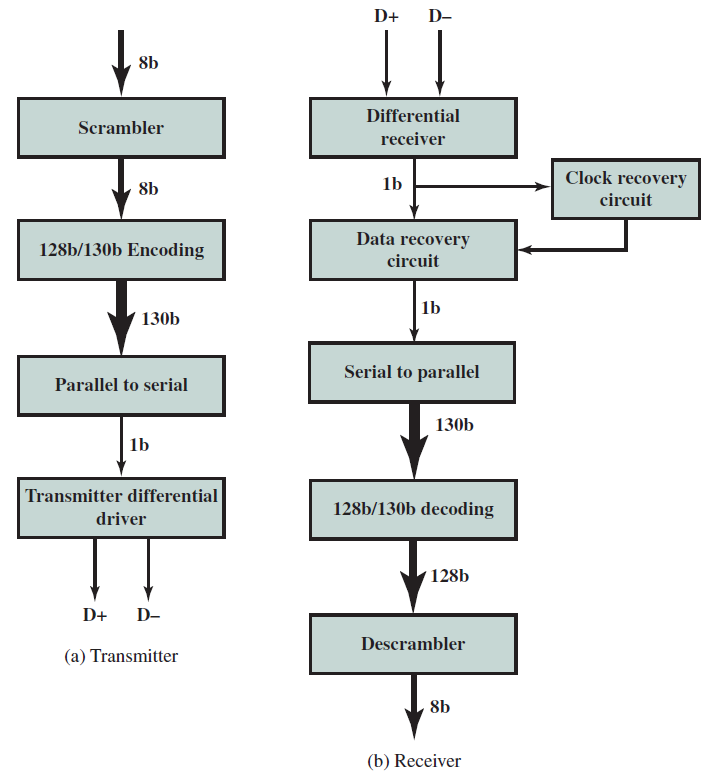

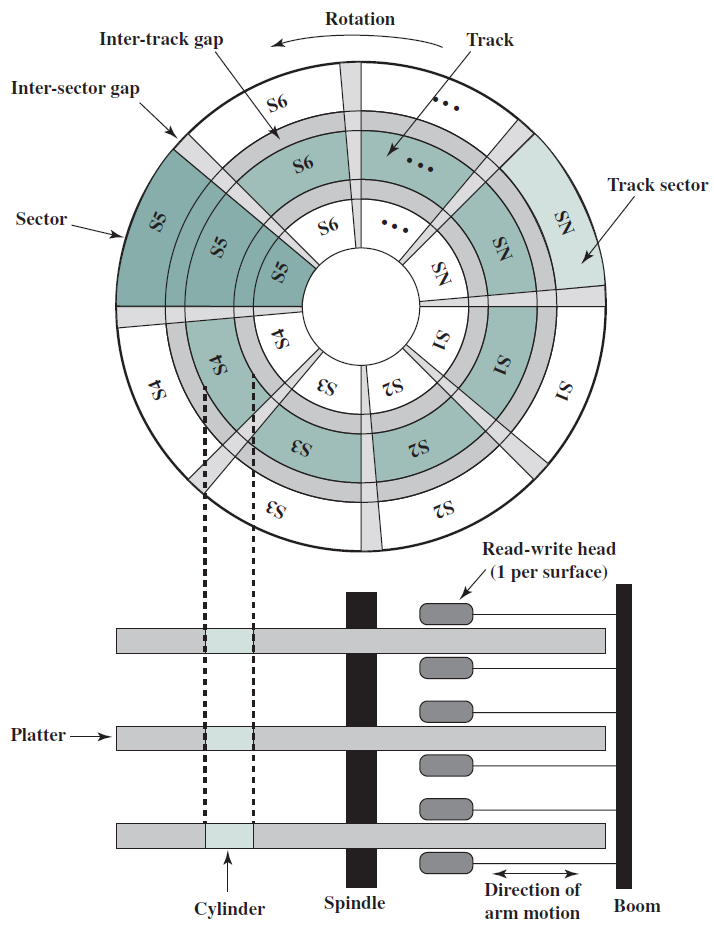

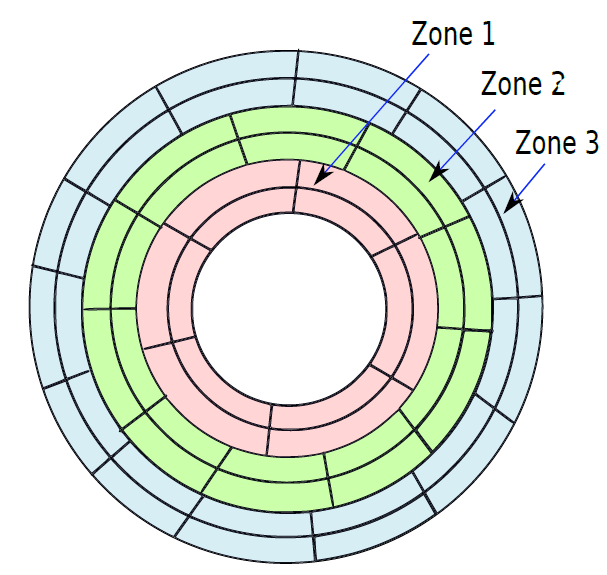

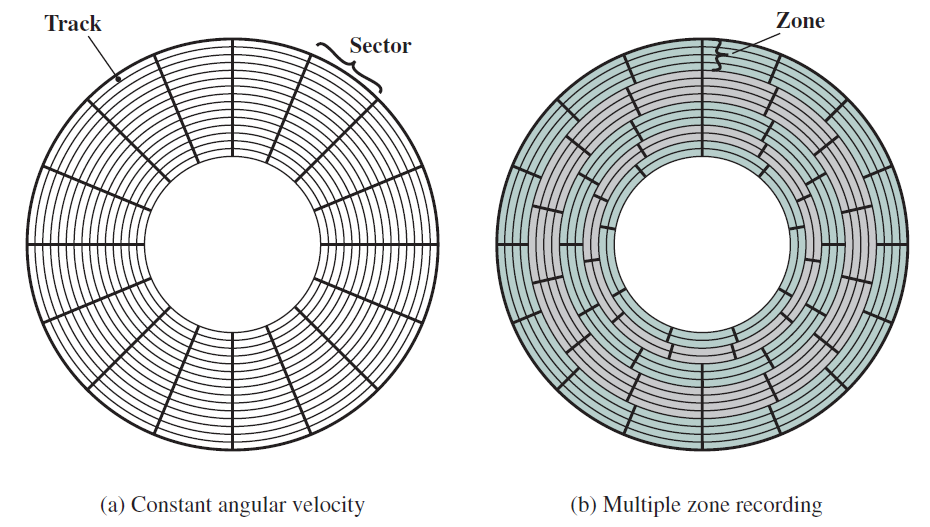

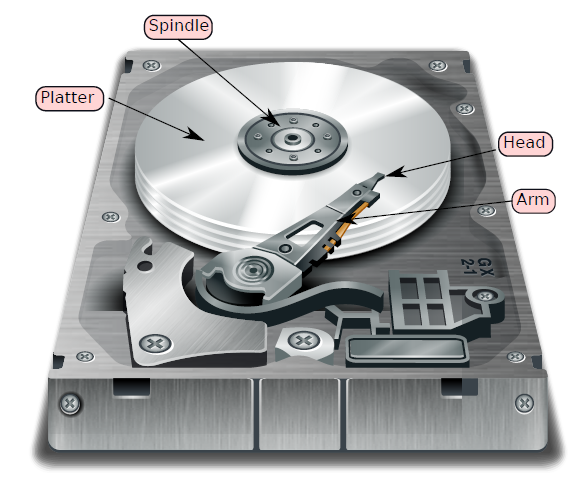

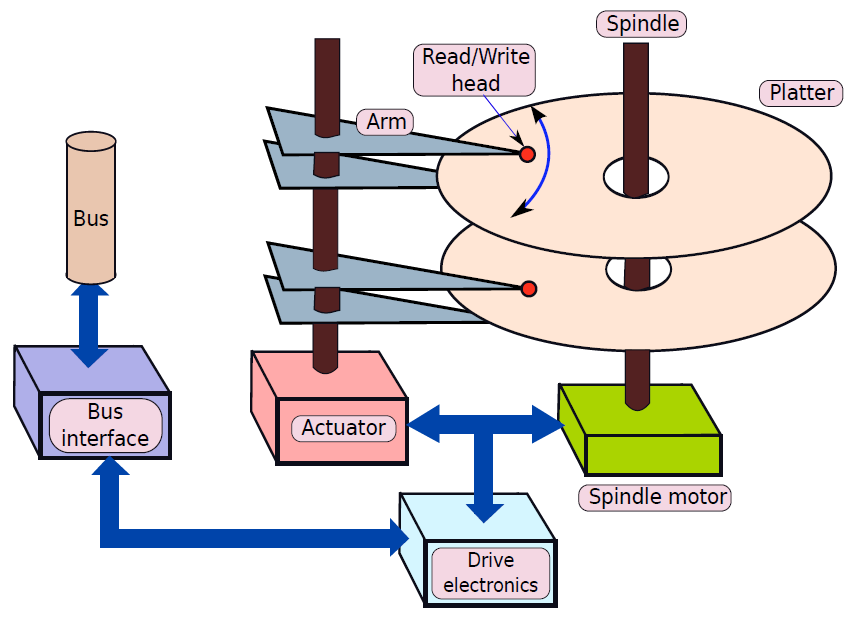

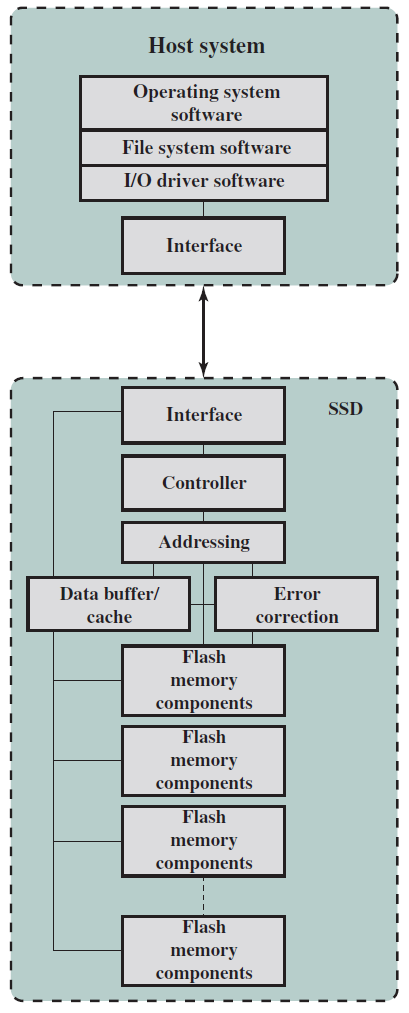

- 19.8 I/O和儲存裝置

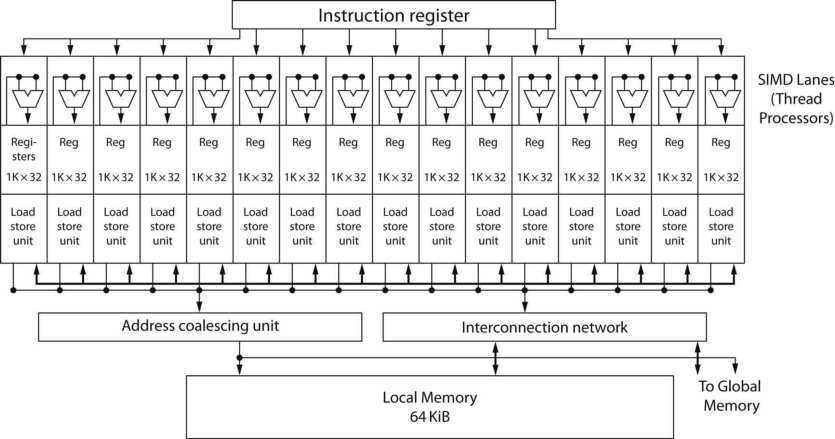

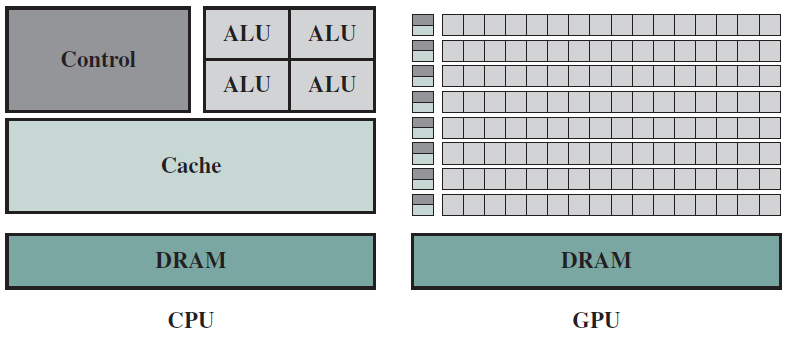

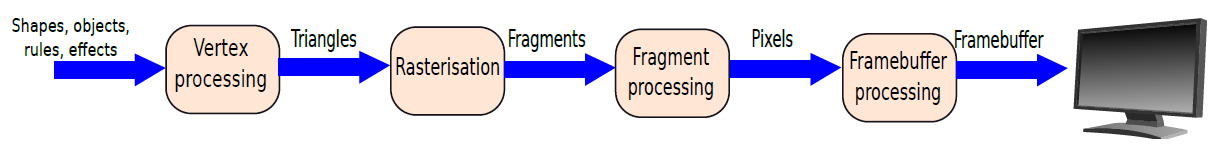

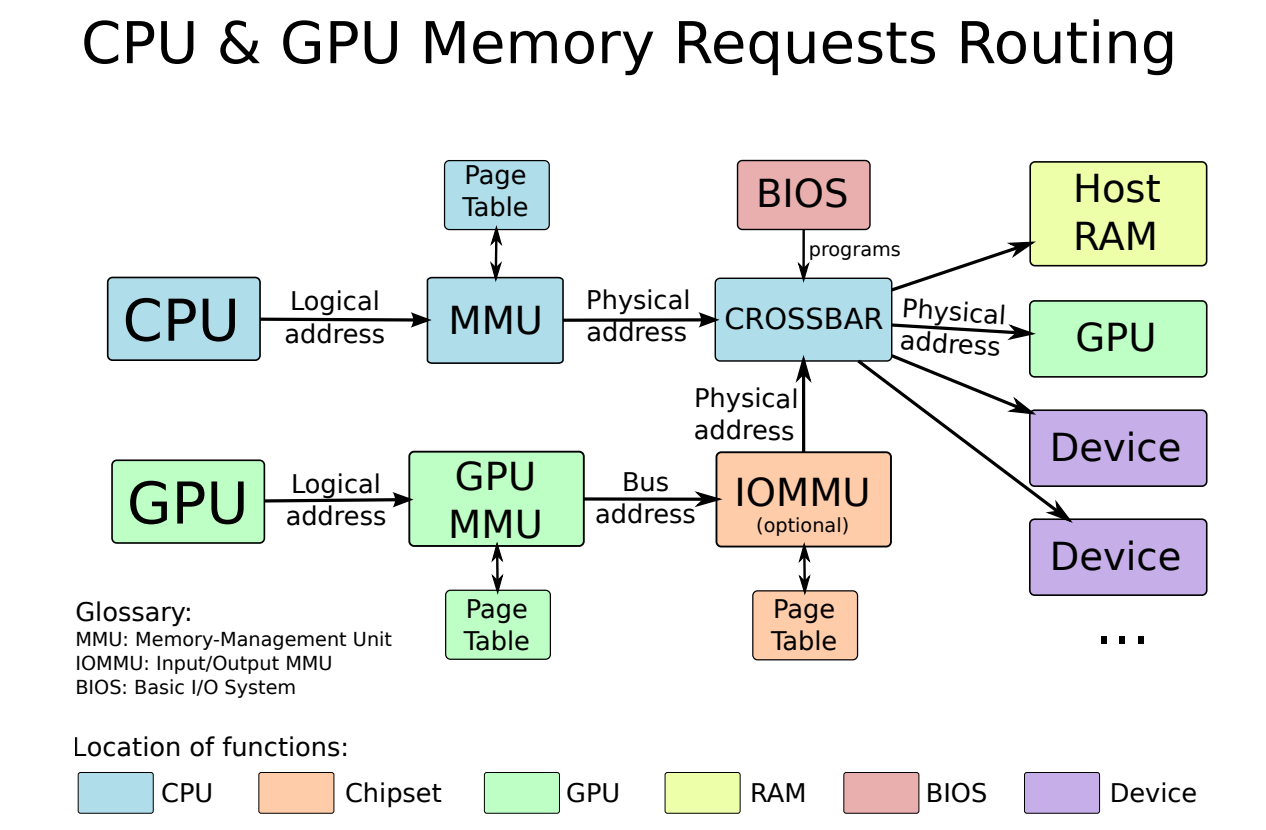

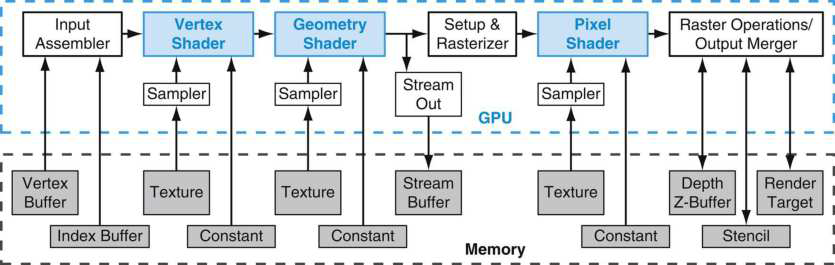

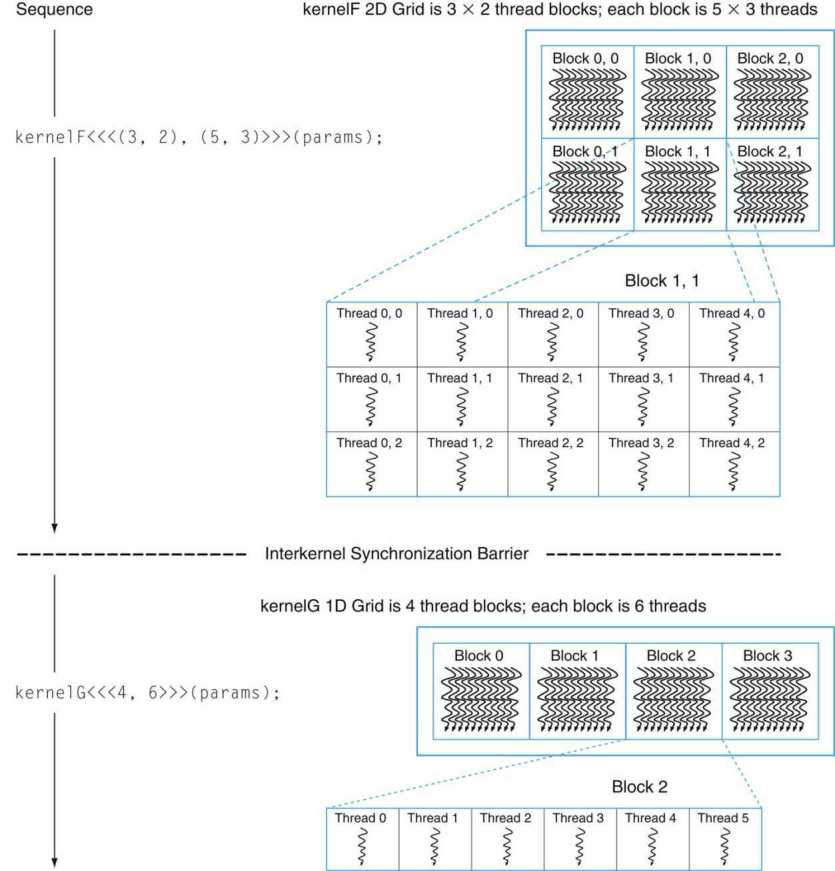

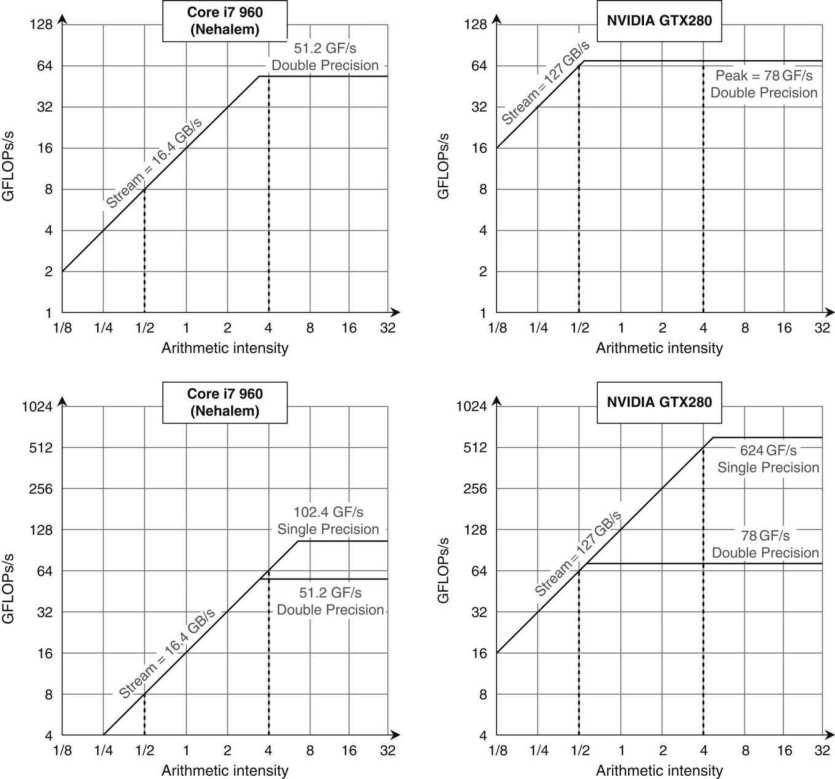

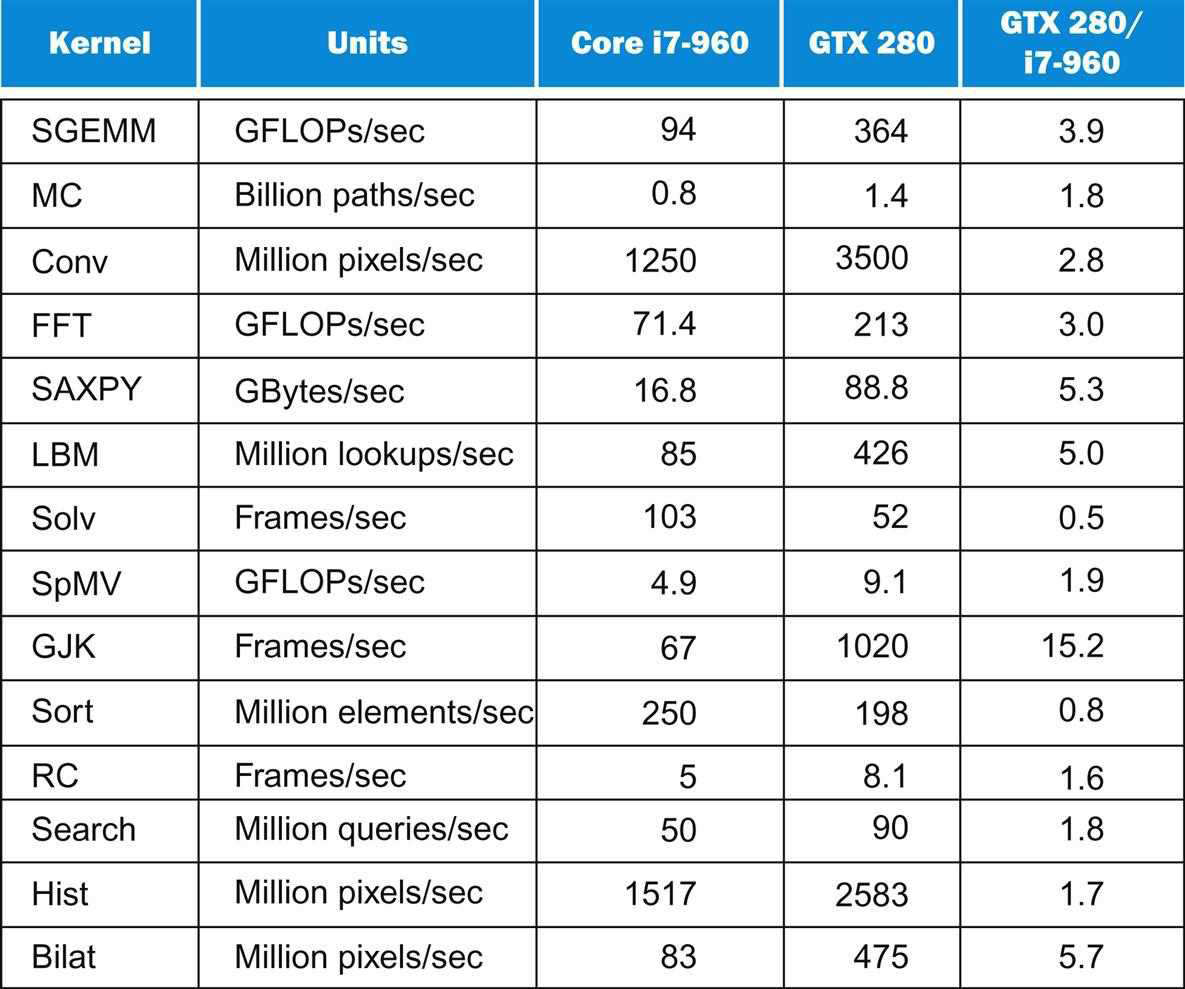

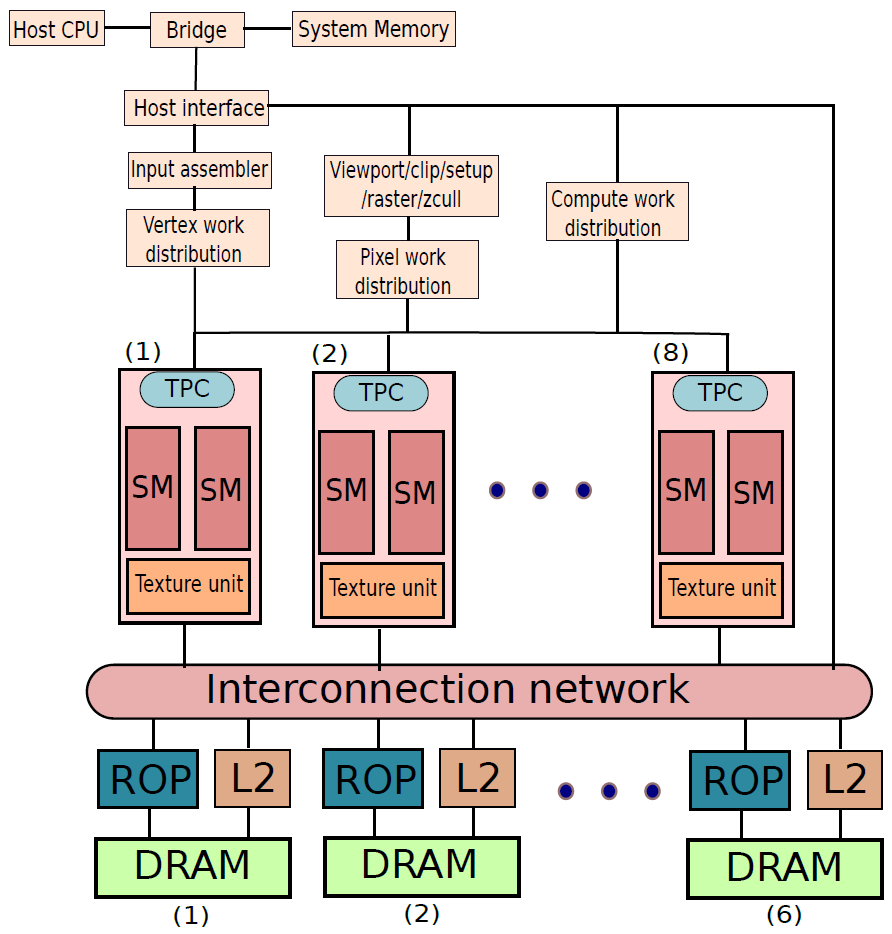

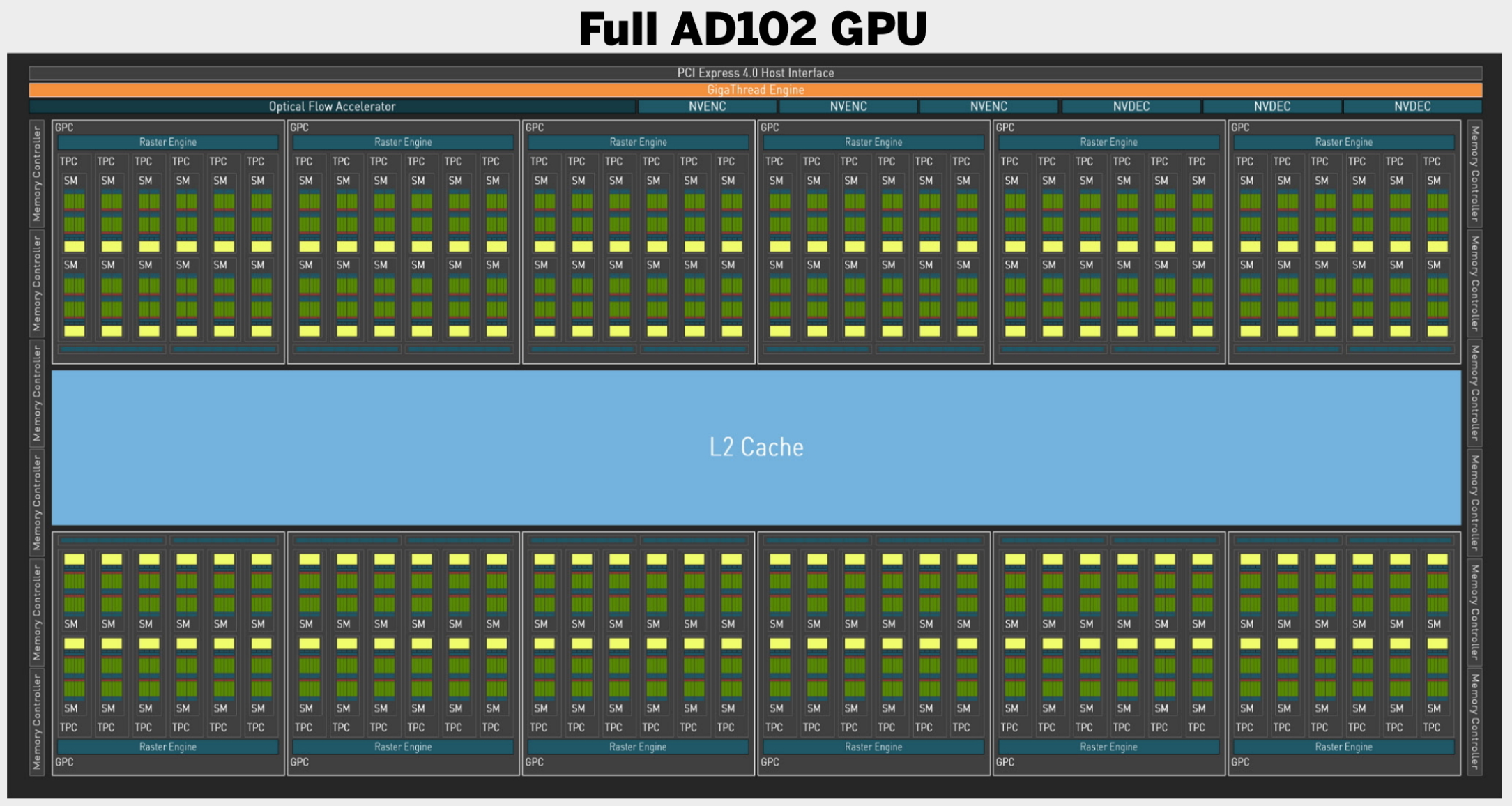

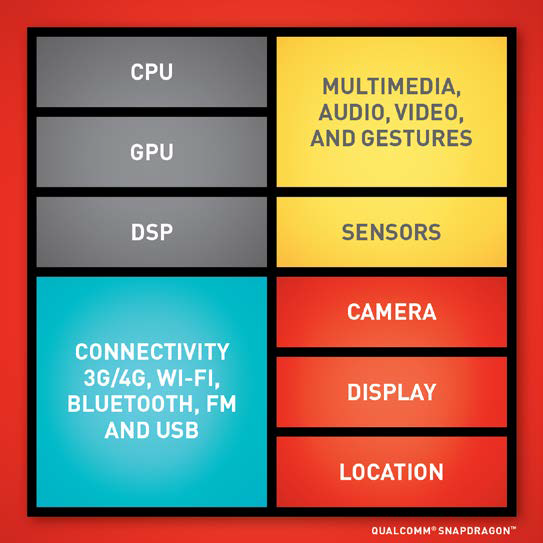

- 19.9 GPU

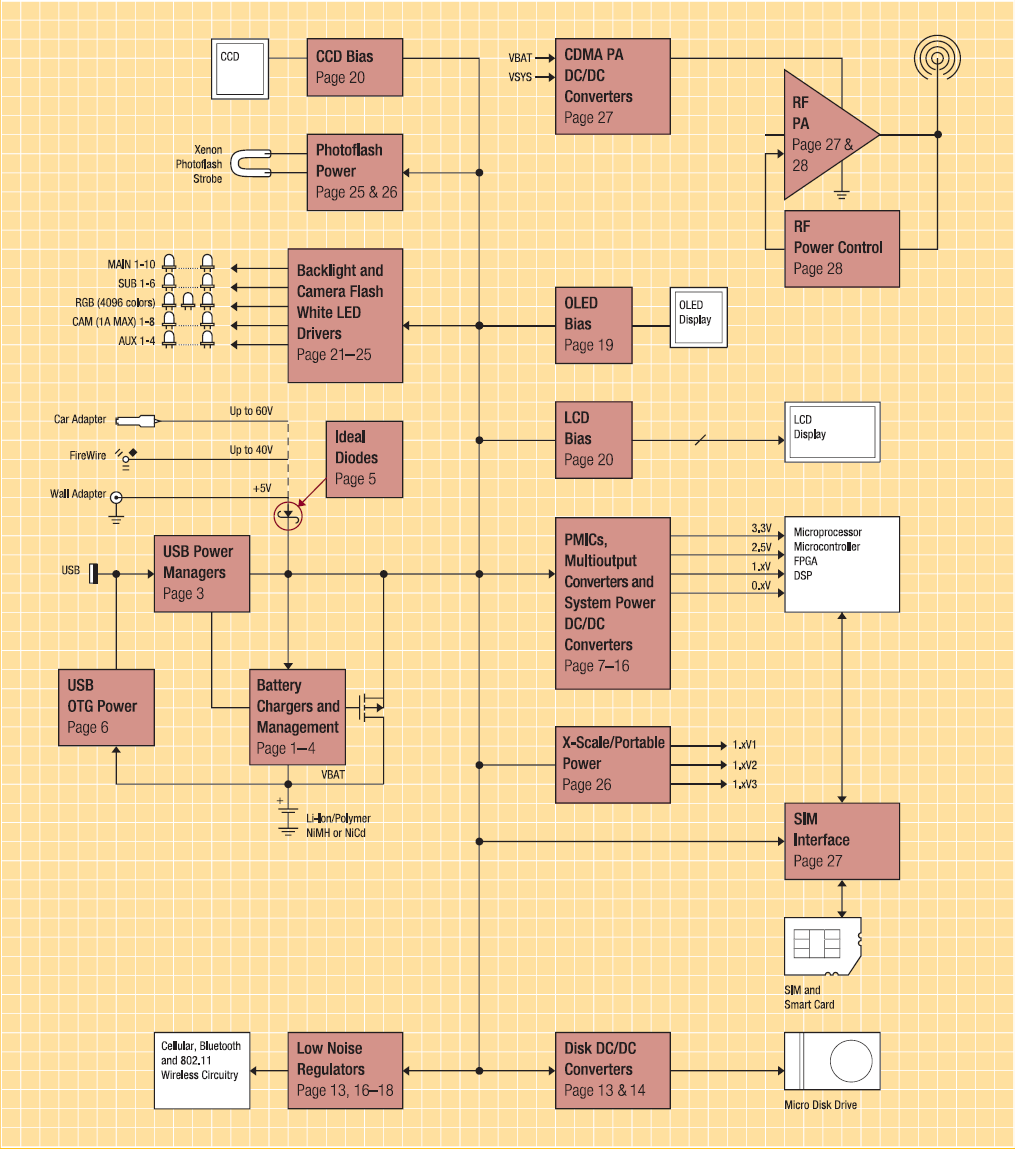

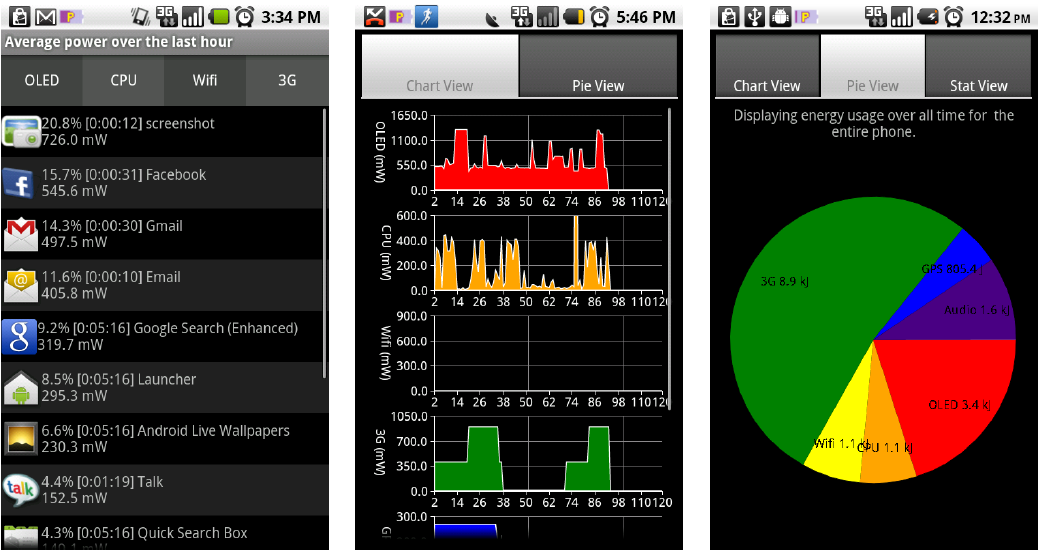

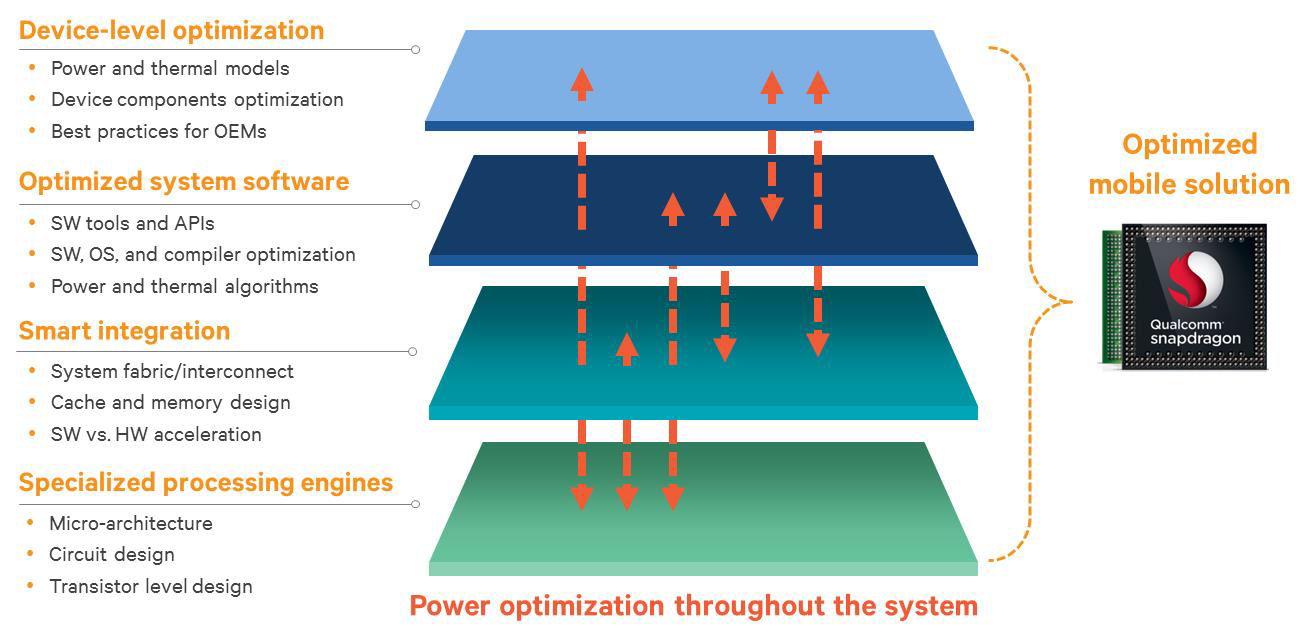

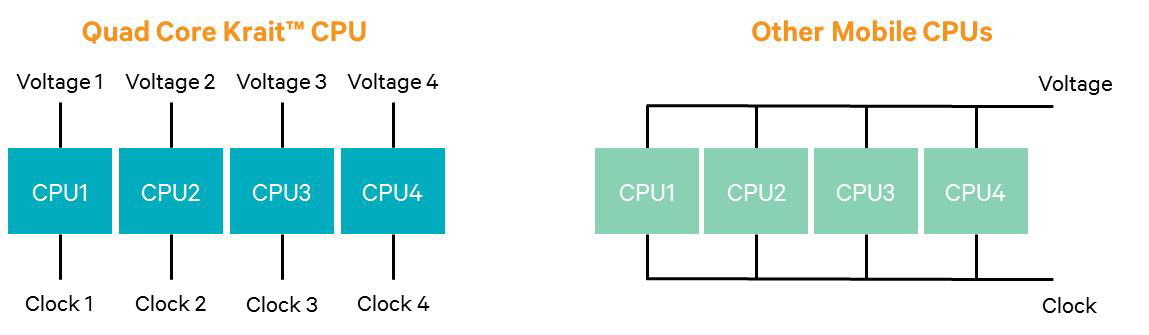

- 19.10 電源

- 19.11 UE硬體

- 19.12 本篇總結

- 特別說明

- 參考文獻

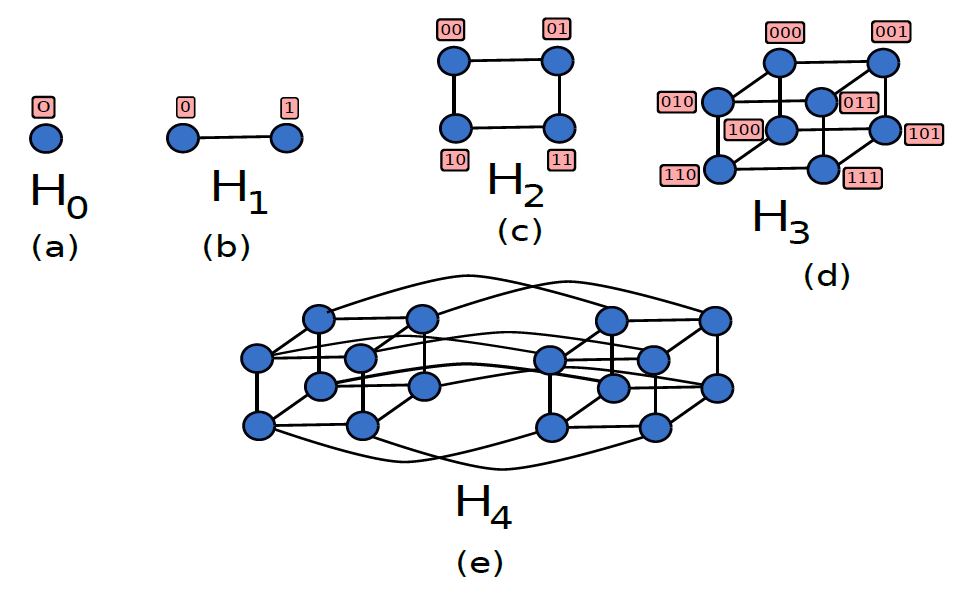

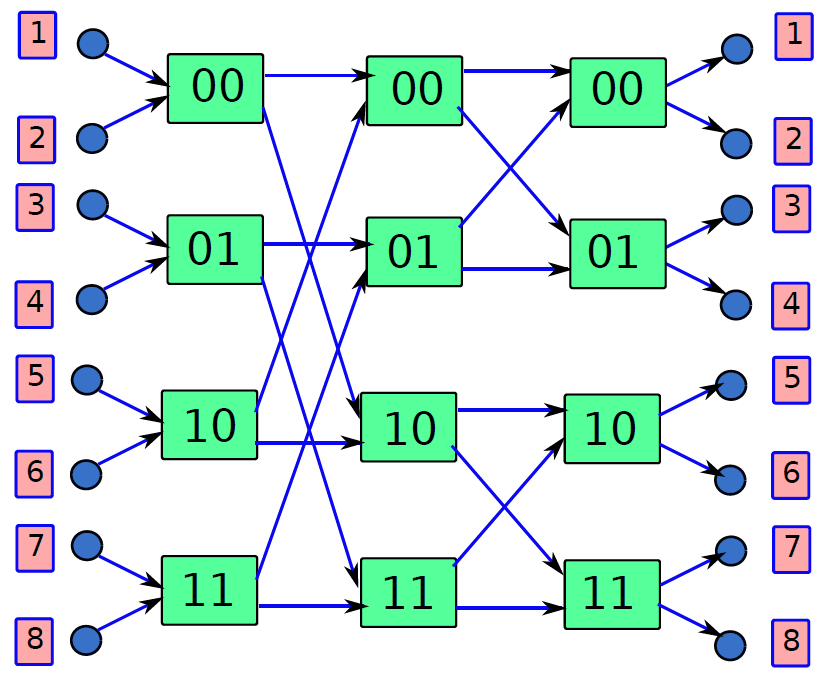

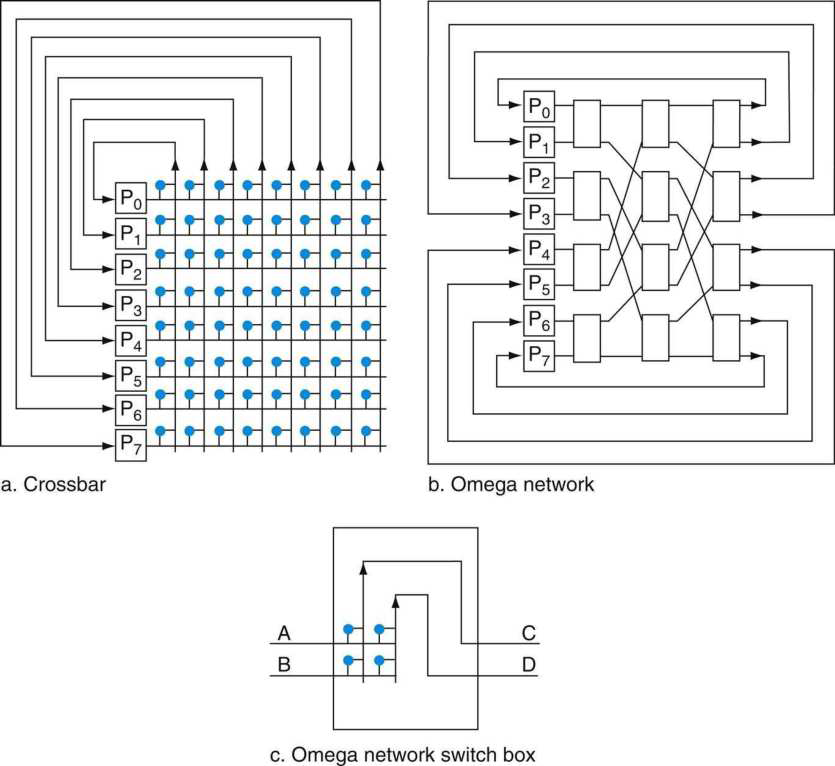

19.1 計算機概述

之前的很多篇文章已經大量涉及了各種各樣的硬體和技術,本篇將更加全面、系統、深入地闡述計算機的硬體組成和體系架構,從而形成自上而下的計算機體知識體系。本篇主要闡述以下內容:

- 計算機基礎。

- 電子電路基礎。

- 計算機硬體。

- 計算機架構和組織。

- 計算機硬體執行機制。

- 計算機硬體的UE封裝和實現。

19.1.1 計算機是什麼

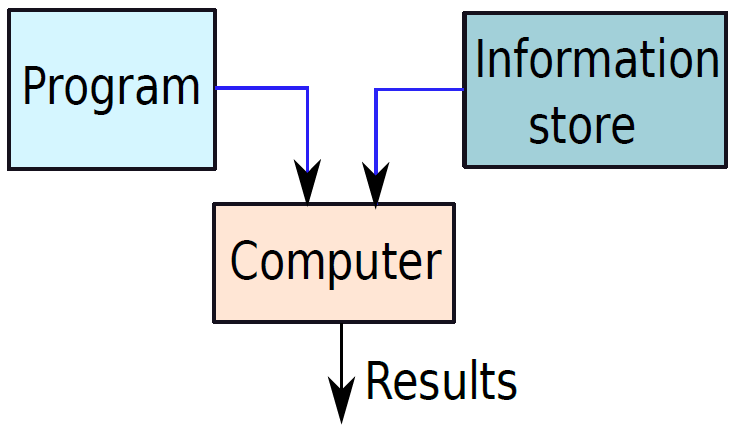

計算機(Computer)是什麼?計算機是一種通用裝置,可以程式設計處理資訊,併產生有意義的結果。它是一種被廣泛使用且使我們的工作變得輕鬆的裝置,是被動型機器,需要我們輸入指令或任務來執行,從而獲得我們需要的結果。

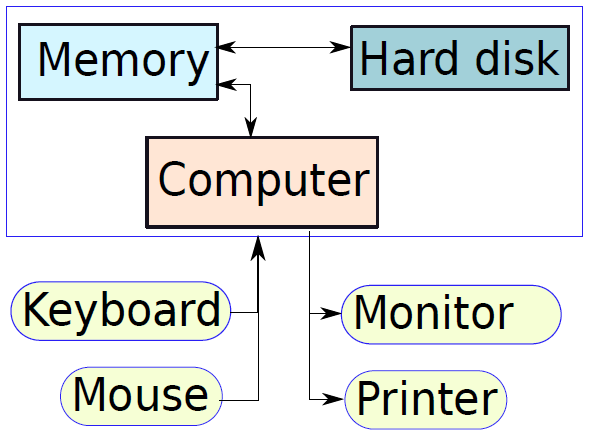

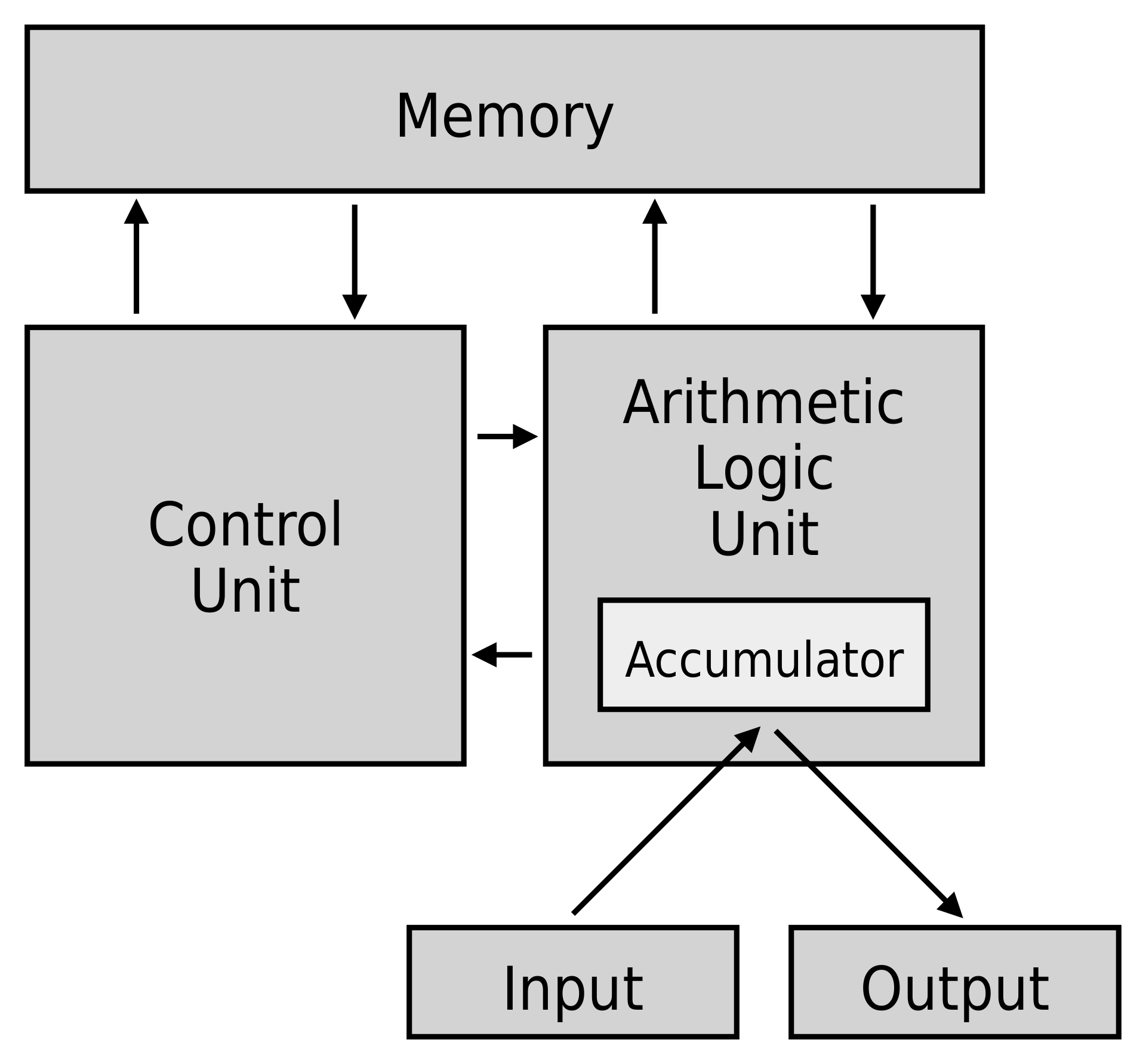

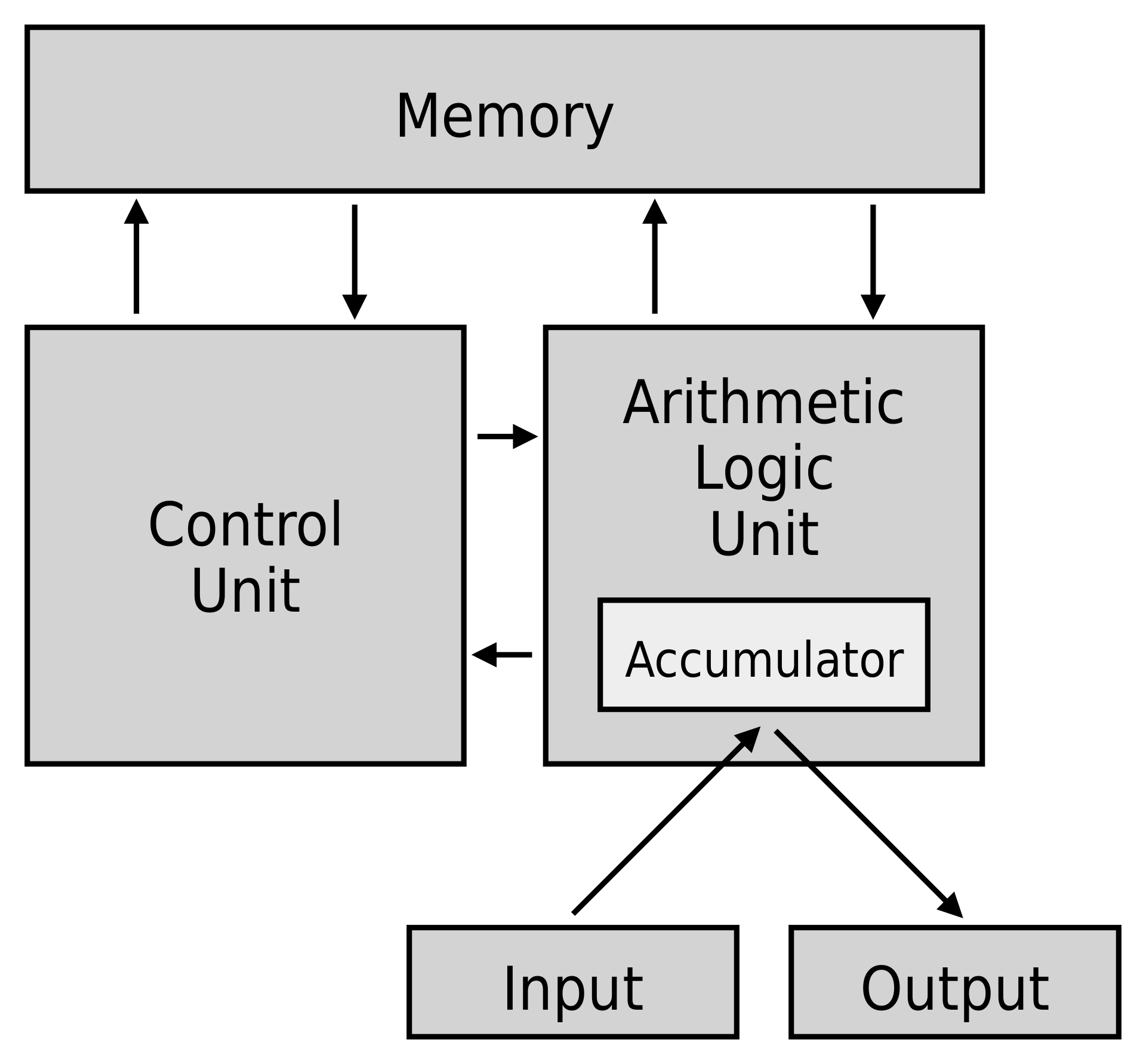

一個基礎的計算機。

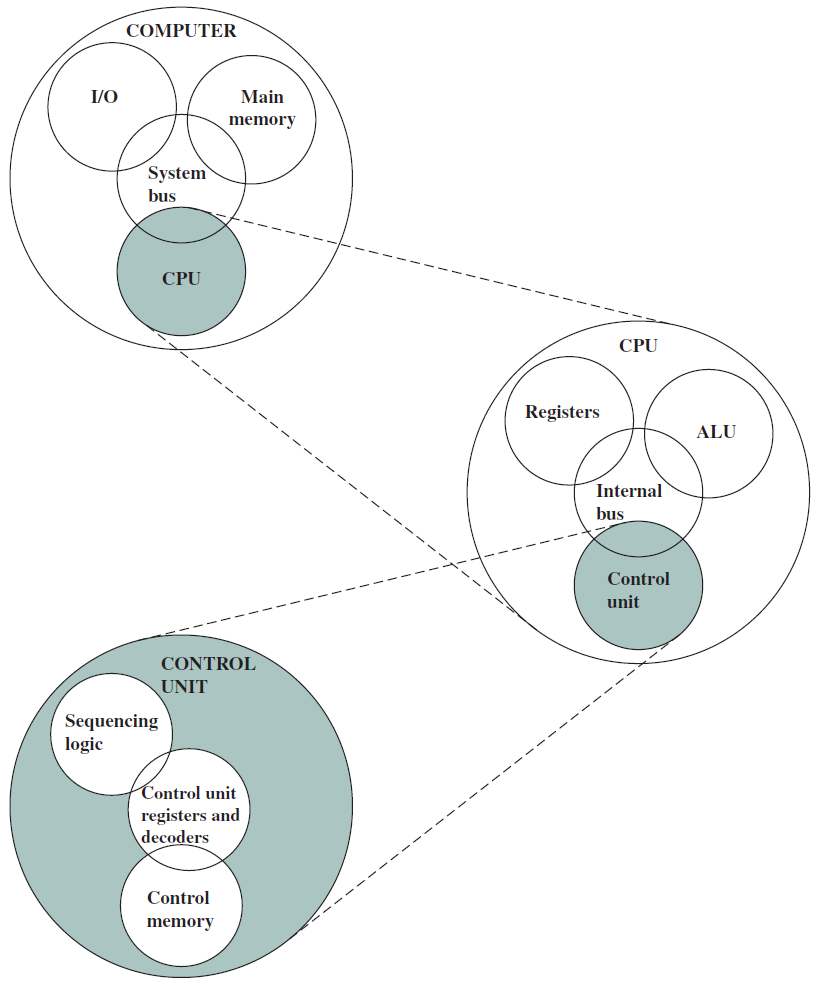

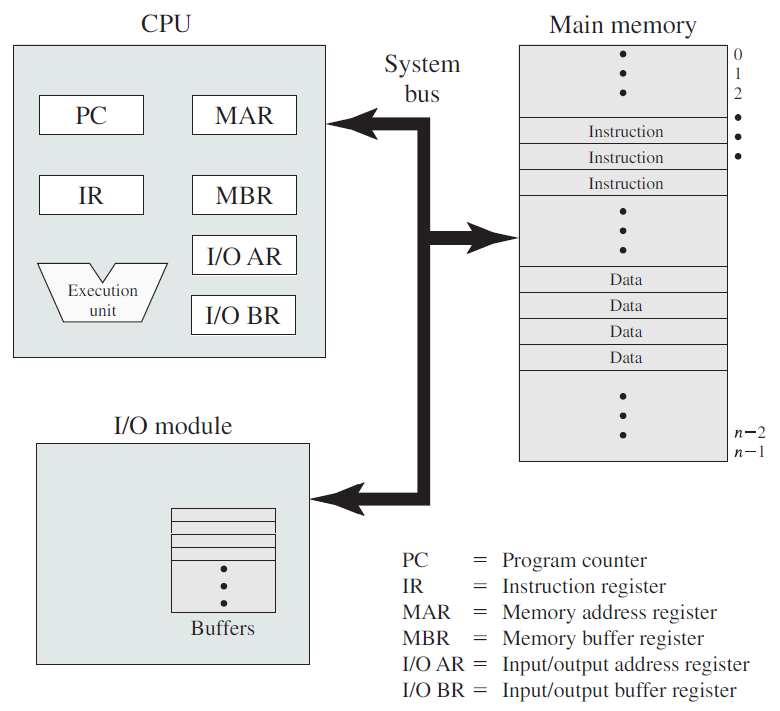

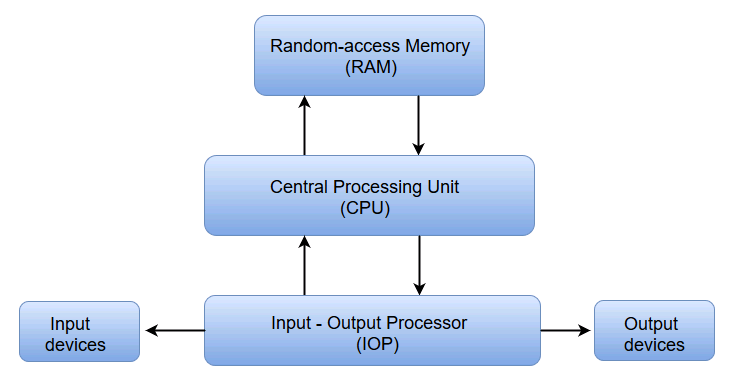

簡單的單處理器計算機如下,提供了傳統單處理器計算機內部結構的分層檢視。有四個主要結構部件:CPU、主記憶體、I/O、系統連結。

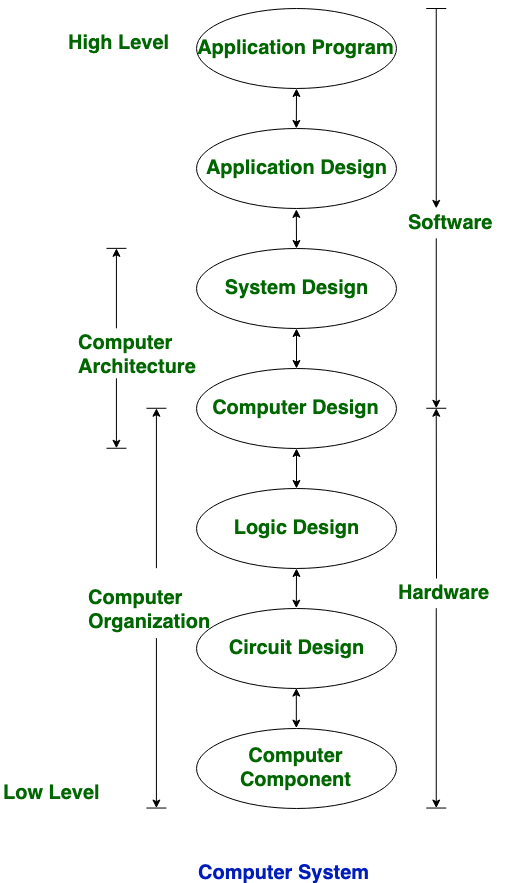

如下圖所示,向用戶提供應用程式時使用的硬體和軟體可以以分層或分層的方式檢視。這些應用程式的使用者,即終端使用者,通常不關心計算機的架構,因此終端使用者根據應用來檢視計算機系統。該應用程式可以用程式語言表示,並由應用程式程式設計師開發,將應用程式開發為一組完全負責控制計算機硬體的處理器指令將是一項極其複雜的任務。為了簡化此任務,提供了一組系統程式。

其中一些程式被稱為實用程式。這些實現了常用的功能,有助於程式建立、檔案管理和I/O裝置控制。程式設計師在開發應用程式時使用這些工具,應用程式在執行時呼叫實用程式來執行某些功能。最重要的系統程式是作業系統,作業系統向程式設計師隱藏了硬體的細節,併為程式設計師提供了使用系統的方便介面。它充當中介,使程式設計師和應用程式更容易存取和使用這些設施和服務。

硬體之中,最重要的部件是晶片,其製造工藝如下圖。從矽錠切片後,將空白晶片經過20至40個步驟,以形成圖案化晶片。然後用晶片測試儀對這些圖案化的晶片進行測試,並繪製出良好零件的地圖。然後將晶片切成小片,在該圖中,一個晶片生產了20個管芯,其中17個管芯通過了測試(X表示模具不良)。在這種情況下,好模具的產量為17/20,即85%。然後將這些好的模具粘結到包裝中,並在將包裝好的零件運送給客戶之前再次進行測試。最終測試中發現一個包裝不良的零件。

19.1.2 計算機結構

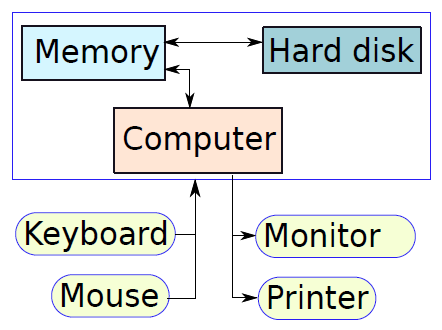

典型的臺式計算機有三個主要物理部件——CPU(中央處理器)、主記憶體儲器和硬碟。CPU通常也被稱為處理器或簡單的機器,是計算機的大腦,是計算機的主要部分,將程式作為輸入並執行。主記憶體儲器用於儲存程式在執行過程中可能需要的資料(資訊儲存),處理器本身的儲存空間有限。當電源關閉時,處理器和主記憶體儲器會丟失所有資料,但硬碟代表永久儲存,程式、資料、照片、視訊和檔案等資料都儲存在硬碟中。

下圖顯示了三個元件的簡化框圖。除了這些主要元件之外,還有一系列與計算機相連的外圍元件,例如鍵盤和滑鼠連線到計算機。它們從使用者處獲取輸入,並將其傳遞給處理器上執行的程式。

類似地,為了顯示程式的輸出,處理器通常將輸出資料傳送到監視器,監視器可以以圖形方式顯示結果,也可以使用印表機列印結果。最後,計算機可以通過網路連線到其他計算機。所有外圍裝置的方框圖如下所示。

19.1.3 計算機執行機制

不管底層技術如何,我們需要理解的一個基本概念是,計算機從根本上來說是一臺愚蠢的機器。與我們的大腦不同,它沒有被賦予抽象的思想、理性和良知。至少在目前,計算機不能自己做出非常複雜的決定,能做的就是執行一個程式。儘管如此,計算機之所以如此強大,是因為它們非常擅長執行程式,每秒可以執行數十億條基本指令。計算機與人腦的比較如下表所示。

| 特性 | 計算機 | 人腦 |

|---|---|---|

| 智力 | 愚蠢 | 智慧 |

| 算力 | 超快 | 慢 |

| 是否疲倦 | 絕不 | 一段時間後 |

| 是否厭倦 | 絕不 | 幾乎總是 |

計算機無法理解人類語言,只能理解二進位制資料,也就是0和1、True和False、On和Off,這些狀態是通過電晶體(transistor)實現的。電晶體是用於儲存2個值(1和0或開和關)的微型裝置,如果電晶體開啟,它的值為 1,如果它關閉,則值為 0。

例如,一個儲存晶片包含數億甚至數十億個電晶體,每個電晶體都可以單獨開啟或關閉。當極少量的電流通過電晶體時,它保持狀態1,當沒有電流時,電晶體的狀態為0。具體範例:

1 : 1

2 : 10

3 : 11

a : 01100001

A : 01000001

U : 01010101

Hello : 01001000 01100101 01101100 01101100 01101111

Hello World! : 01001000 01100101 01101100 01101100 01101111 00100000 01010111 01101111 01110010 01101100 01100100 00100001

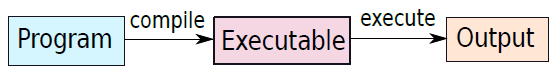

問題在於,以上二進位制程式碼對於人類而言,太難以理解了,此時需要各類計算機軟體做翻譯的橋樑作用。軟體是一組指令,告訴計算機要做什麼、什麼時候做以及如何做。下圖顯示了操作流程。第一步是用高階語言(C或C++)編寫程式,第二步涉及編譯它,編譯器將高階程式作為輸入,並生成包含機器指令的程式,該程式通常稱為可執行檔案或二進位制檔案。注意,編譯器本身是一個由基本機器指令組成的程式。

假設要執行2+2的指令,那麼我們必須給計算機指令:

- 第1步:取2個值。

- 第2步:儲存該2值。

- 第3步:使用 + 運運算元對它們進行相加。

- 第4步:儲存結果。

為 + 運運算元提供了單獨的說明,以便計算機在遇到 + 符號時知道如何進行加法。那麼誰來轉換這段程式碼呢?答案是直譯器(interpreter),它把我們的語言程式碼轉換成計算機可以理解的機器語言。同理,輸入和輸出資料也需要依賴特定的軟體和直譯器。

就像任何語言都有有限的單詞一樣,處理器可以支援的基本指令/基本命令的數量也必須是有限的,這組指令通常稱為指令集(instruction set),基本指令的一些範例是加法、減法、乘法、邏輯或和邏輯非。請注意,每條指令需要處理一組變數和常數,最後將結果儲存在變數中。這些變數不是程式設計師定義的變數,是計算機內的內部位置。

19.1.4 計算機設計準則

計算機設計是元件相互關聯的結構。設計者一次處理特定級別的系統,並且在不同級別存在不同型別的問題。在每一層,設計者都關心結構和功能,結構是相互關聯的用於通訊的各個元件的骨架,功能是系統中涉及的活動。 以下是計算機設計中的問題:

- 無限速度的假設: 不能假設計算機的無限速度,因為假設無限速度是不切實際的,也給設計者的思維帶來了問題。

- 記憶體無限的假設: 就像計算機的速度一樣,記憶體也不能假設為無限的,總是有限的。

- 記憶體和處理器之間的速度不匹配: 有時記憶體和處理器的速度可能不匹配,可能是記憶體速度更快或處理器速度更快。記憶體和處理器之間的不匹配會導致設計中出現問題。

- 處理錯誤和錯誤: 處理缺陷和錯誤是任何計算機設計者的巨大責任,缺陷和錯誤會導致計算機系統出現故障,有時這些錯誤可能更危險。

- 多處理器: 設計具有多個處理器的計算機系統會導致管理和程式設計的巨大任務,是計算機設計中的一大問題。

- 多執行緒: 具有多執行緒的計算機系統總是對設計者構成威脅,具有多個執行緒的計算機應該能夠進行多工和多處理。

- 共用記憶體: 如果一次要執行多個程序,則所有程序共用相同的記憶體空間。應該以特定的方式對其進行管理,以免發生衝突。

- 磁碟存取: 磁碟管理是計算機設計的關鍵,磁碟存取存在幾個問題,系統可能不支援多磁碟存取。

- 更好的效能: 始終是一個問題,設計者總是試圖簡化系統以獲得更好的效能來降低功耗和降低成本。

19.1.5 實用機器架構

下面闡述一下不同型別的實用機器的設計及架構。

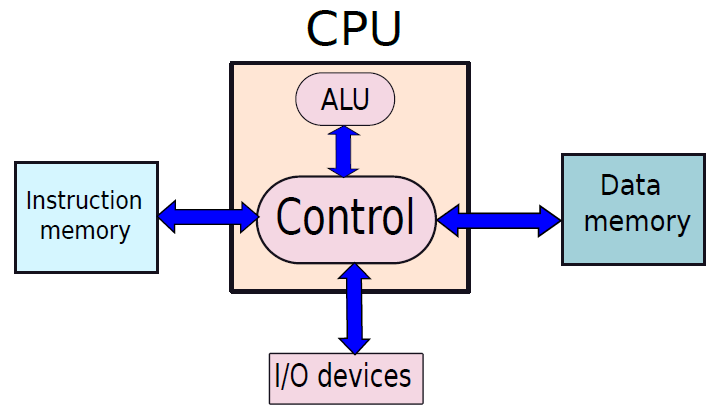

- 哈佛架構

哈佛體系架構下圖所示,有單獨的結構來維護指令表和記憶體。指令表也被稱為指令記憶體,因為可以把它看作是專門為只儲存指令而設計的專用記憶體。記憶體儲存程式所需的資料值,因此被稱為資料記憶體。處理指令的引擎分為兩部分:控制和ALU,控制單元的工作是獲取指令、處理指令並協調指令的執行。ALU代表算術邏輯單元,有專門的電路,可以計算算術表示式或邏輯表示式(and/or/NOT等)。

請注意,每臺計算機都需要從使用者/程式設計器處獲取輸入,並最終將結果傳回程式設計器,可通過多種方法實現,例如我們如今使用的鍵盤和顯示器。早期的計算機使用一組開關,最終結果列印在一張紙上。

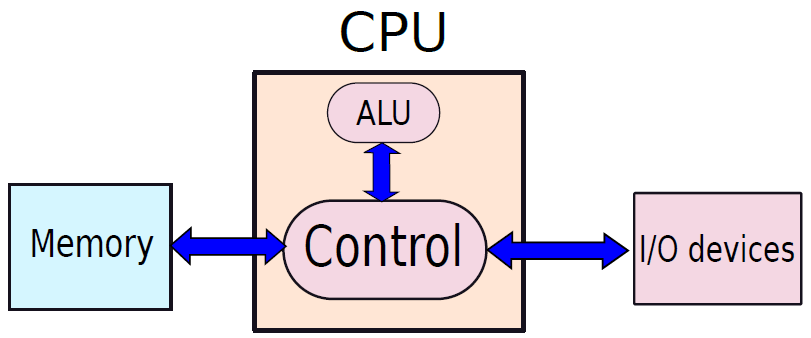

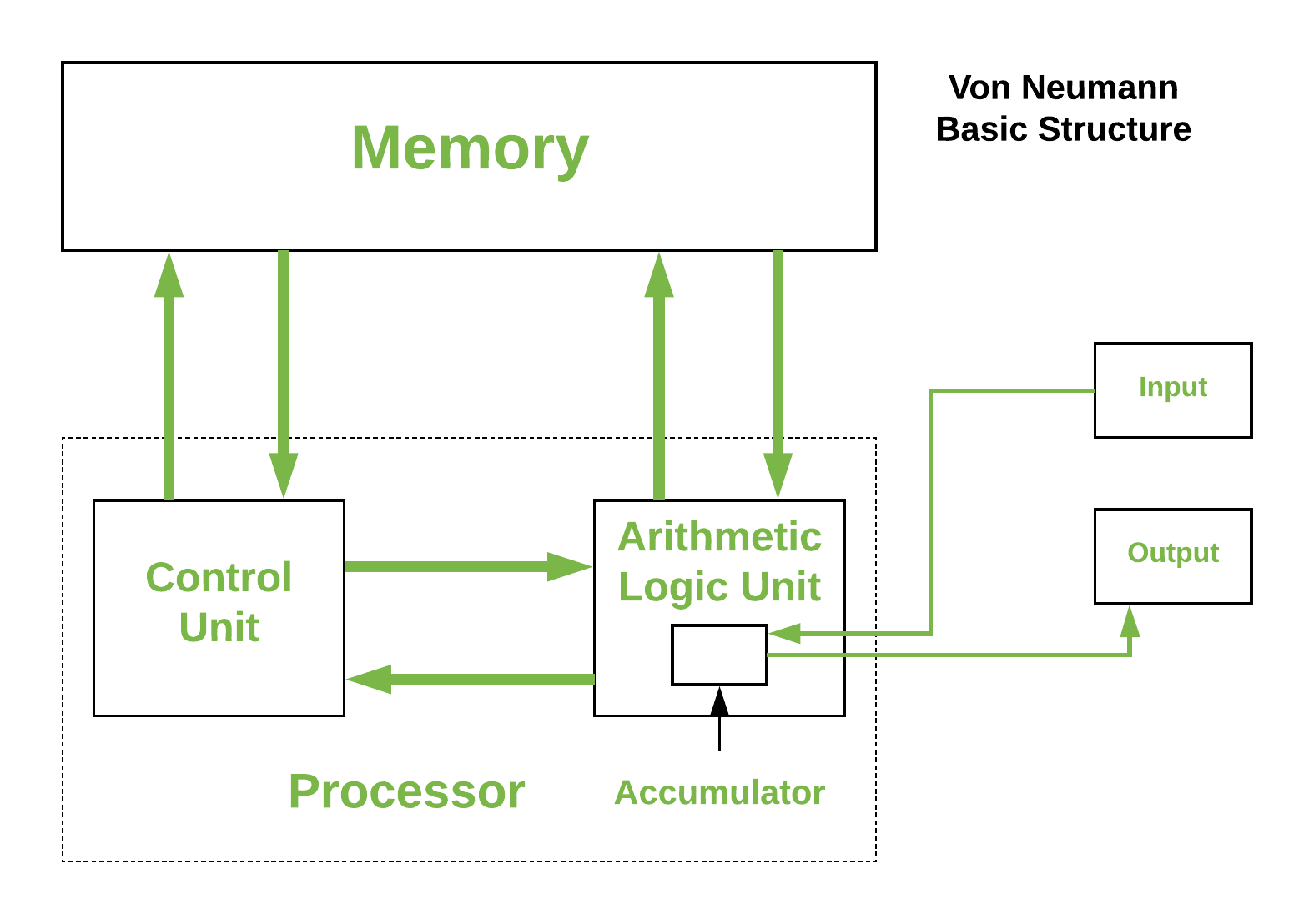

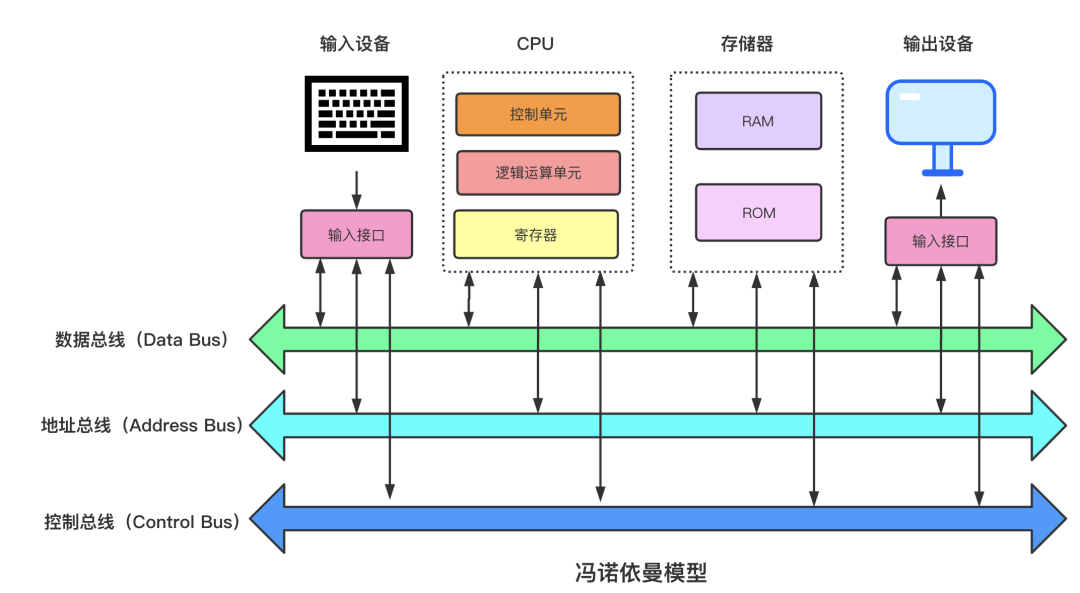

- 馮諾依曼架構

約翰·馮·諾依曼提出了通用圖靈完備計算機的馮·諾伊曼體系結構,實際上,Eckert和Mauchly於1946年基於該架構設計了第一臺通用圖靈完備計算機(有個小限制),稱為ENIAC(電子數位積分器和計算器),該計算機用於計算美國陸軍彈道研究實驗室的火炮環表,後來在1949年被EDVAC計算機取代,該計算機也被美國陸軍的彈道研究實驗室使用。

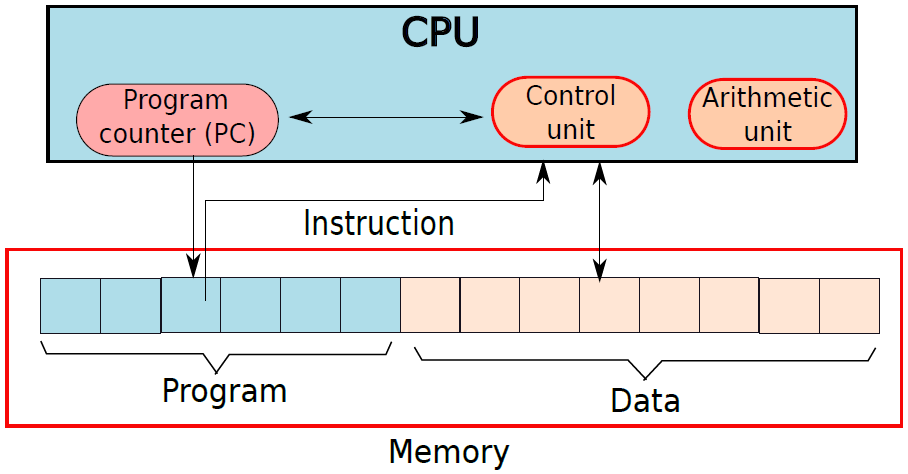

作為ENIAC和EDVAC基礎的基本馮·諾依曼架構如下圖所示。指令表儲存在記憶體中,圖靈機的處理引擎被稱為CPU(中央處理單元),包含程式計數器,其工作是獲取新指令並執行它們。它有專用的功能單元來計算算術函數的結果,在記憶體位置載入和儲存值,以及計算分支指令的結果。最後,與哈佛體系結構一樣,CPU連線到I/O子系統。

這臺機器的創新之處在於指令表儲存在記憶體中,使用通常儲存在記憶體中的同一組符號對每條指令進行編碼。例如,如果記憶體儲存十進位制值,則每條指令都需要編碼為十進位制數位串。馮·諾依曼CPU需要解碼每條指令,這個想法的核心是,指令被視為常規資料(記憶體值)。這個簡單的想法實際上是設計優雅計算系統的一個非常強大的工具,被稱為儲存程式概念。

儲存程式概念(stored program concept):程式儲存在記憶體中,指令被視為常規記憶體值。

儲存程式概念極大地簡化了計算機的設計。由於記憶體資料和指令在概念上是以相同的方式處理的,所以我們可以有一個統一的處理系統和一個以相同方式處理指令和資料的記憶體系統。從CPU的角度來看,程式計數器指向一個通用記憶體位置,其內容將被解釋為編碼指令的內容,很容易儲存、修改和傳輸程式,程式還可以在執行時通過修改自身甚至其他程式來動態更改其行為。這構成了當今複雜編譯器的基礎,這些編譯器將高階C程式轉換為機器指令。此外,許多現代系統(如Java虛擬機器器)動態地修改它們的指令以實現效率。

馮·諾伊曼機器或哈佛機器不像圖靈機器那樣擁有無限的記憶體,嚴格地說,它們並不完全等同於圖靈機,對於所有實用的機器都是如此,它們需要足夠的資源。然而,科學界已經學會接受這種近似。

19.2 計算機硬體基礎

19.2.1 組合語言

組合語言可以廣泛地定義為機器指令的文字表示。在構建處理器之前,我們需要了解不同機器指令的語意,在這方面,對組合語言的嚴格研究將是有益的。組合語言專用於ISA和編譯器框架,因此,組合語言有許多優點。本節將描述不同組合語言變體的基本原理,一些通用概念和術語。隨後,將描述針對基於ARM的處理器的ARM組合語言,描述針對Intel/AMD處理器的x86組合語言。

19.2.1.1 為什麼用組合語言?

先從軟體開發者的視角闡述之。

人類懂得自然語言,如中文、英語和西班牙語。通過一些額外的訓練,人類還可以理解計算機程式語言,如C或Java。然而,如前面所述,計算機是一臺愚蠢的機器,不夠聰明,無法理解人類語言(如英語)或程式語言(如C)中的命令,它只能理解零和一。因此,要給計算機程式設計,必須給它一個0和1的序列。事實上,一些早期的程式設計師曾經通過開啟或關閉一組開關來程式設計計算機,開啟一個開關對應於1,開啟它意味著0。對於今天的大規模數百萬行程式來說,不是一個可行的解決方案,需要另尋更好的方法。

因此,我們需要一個自動轉換器,它可以將用C或Java等高階語言編寫的程式轉換為一系列0和1,稱為機器程式碼(machine code)。機器程式碼包含一組稱為機器指令的指令,每個機器指令都是由零和一組成的序列,並指示處理器執行特定的操作。可以將用高階語言編寫的程式轉換為機器程式碼的程式稱為編譯器(見下圖)。

編譯過程。

請注意,編譯器是一個可執行程式,通常在應該為其生成機器程式碼的機器上執行。可能出現的一個自然問題是——誰編寫了第一個編譯器?

第一,鑑於編譯器的普遍存在,幾乎所有的程式都是用高階語言編寫的,編譯器用來將它們轉換為機器程式碼,但這一規則也有重要的例外。請注意,編譯器的作用有兩方面:首先,它需要正確地將高階語言的程式翻譯成機器指令;其次,它需要生成不佔用大量空間且速度快的高效機器程式碼。因此,多年來編譯器中的演演算法變得越來越複雜,但並不總是能夠滿足這些要求,例如在某些情況下,編譯器可能無法生成足夠快的程式碼,或者無法提供程式設計師期望的某種功能:

- 首先,編譯器中的演演算法受到它們對程式執行的分析量的限制。例如,我們不希望編譯過程極其緩慢,編譯器領域的許多問題在計算上很難解決,因此很耗時。

- 其次,編譯器不知道程式碼中的廣泛模式。例如,某個變數可能只取一組有限的值,在此基礎上,可能進一步優化機器程式碼,編譯器很難理解這一點。聰明的程式設計師有時可以生成比編譯器更優化的機器程式碼,因為他們知道一些廣泛的執行模式,可以勝過編譯器。

- 處理器供應商也可能在ISA中新增新指令。在這種情況下,用於舊版本處理器的編譯器可能無法利用新指令,需要在程式中手動新增它們。流行的編譯器(如gcc,GNU編譯器集合)是相當通用的,它們不使用處理器在生成機器程式碼時提供的所有可能的機器指令。通常,作業系統和裝置驅動程式(與印表機和掃描器等裝置介面的程式)需要大量遺漏的指令,因為它們需要對硬體的低階別存取,因此係統程式設計師有強烈的動機偶爾繞過編譯器。

在所有這些情況下,程式設計師都有必要在程式中手動嵌入一系列機器指令。如上所述,這樣做的兩個主要原因是效率和額外的功能。因此,從系統軟體開發人員的角度來看,有必要了解機器指令,以便他們在工作中更有效率。

現在,我們的目標是讓現代程式設計師遠離0和1的複雜細節。理想情況下,我們不希望程式設計師像50年前那樣通過手動開啟和關閉開關來程式設計,由此開發了一種稱為組合語言的低階語言。組合語言是機器程式碼的一種人類可讀形式,每個組合語言語句通常對應於一條機器指令。此外,它通過不強迫程式設計師記住編碼指令所需的0/1的確切序列,大大減輕了程式設計師的負擔。

- 低階程式語言(low level programming language)使用通常只對應於一條機器指令的簡單語句,這些語言是ISA特有的。

- 組合語言(assembly language)是指一系列特定於每個ISA的低階程式語言,具有由一系列組合語句組成的泛型結構。通常,每個組合語句有兩部分:

- 一個指令程式碼,是基本機器指令的助記符。

- 一個運算元列表。

從實際角度來看,可以編寫獨立的組合程式,並使用稱為組合器的程式將其轉換為可執行程式,也可以在高階語言(如C或C++)中嵌入組合程式碼片段,後者更為常見。

組合器(assembler)是將組合程式轉換為機器程式碼的可執行程式。

編譯器確保能夠將組合程式編譯為機器程式碼。組合語言的好處是多方面的:

- 可讀性。因為組合程式碼中的每一行對應於一條機器指令,所以它和機器程式碼一樣具有表達力。

- 高效性。由於這種一對一的對映,我們不必通過在組合中編寫程式來提高效率。

- 簡化性。它是一種可讀的、優雅的文字表示機器程式碼的形式,大大簡化了使用它編寫程式的過程,也可以在用C等高階語言編寫的軟體中清晰地嵌入組合程式碼片段,它定義了一個高於實際機器程式碼的抽象級別。兩個處理器可能與同一種組合語言相容,但實際上對同一條指令有不同的機器編碼。在這種情況下,組合程式將在這兩個處理器上相容。

再從硬體設計者的視角闡述之。

硬體設計師的職責是設計能夠實現ISA中所有指令的處理器。他們的主要目標是設計一個在面積、功率效率和設計複雜性方面最佳的高效處理器,從他們的角度來看,ISA是軟體和硬體之間的關鍵紐帶。這回答了他們的基本問題——構建什麼?因此,對他們來說,理解不同指令集的精確語意是非常重要的,這樣他們就可以為它們設計處理器。將指令僅僅看作一個0和1的序列是很麻煩的,通過檢視機器指令的文字表示,他們可以獲得很多好處,很清晰地知道是一條怎樣的組合指令。

組合語言專用於指令集和組合器。本節使用流行的GNU組合器的組合語言格式來解釋典型組合語言檔案的語法,請注意,其他系統具有類似的格式,並且概念大致相同。

19.2.1.2 組合語言基礎

機器模型

組合語言不將指令記憶體和資料記憶體視為不同的實體,假設一個抽象的馮·諾依曼機器增加了暫存器。

有關機器模型的圖示,請參見下圖。程式儲存在主記憶體的一部分中,中央處理單元(CPU)逐條指令讀出程式指令,並適當地執行指令,程式計數器(PC)跟蹤CPU正在執行的指令的記憶體地址,大多數指令都希望從暫存器中獲取其輸入運算元。回想一下,每個CPU都有固定數量的暫存器(通常<64),然而大量指令也可以直接從記憶體中獲取運算元。CPU的工作是協調主記憶體和暫存器之間的傳輸,CPU還需要執行所有算術/邏輯計算,並與外部輸入/輸出裝置保持聯絡。

大多數型別的組合語言在大多數語句中都採用這種抽象機器模型。但由於使用組合語言的另一個目的是對硬體進行更細粒度和侵入性的控制,因此有相當多的組合指令可以識別處理器的內部。

這些指令通常通過改變一些關鍵內部演演算法的行為來修改處理器的行為,它們修改內建引數,如電源管理設定,或讀/寫一些內部資料。最後請注意,組合語言不區分機器無關指令和機器相關指令。

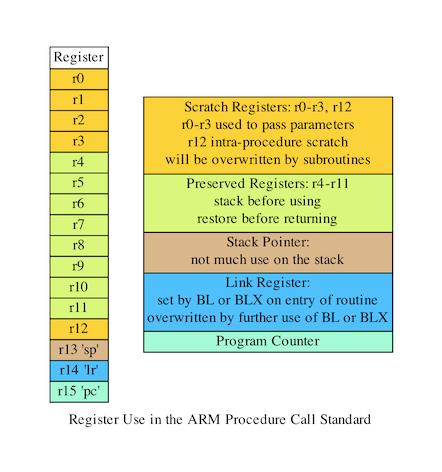

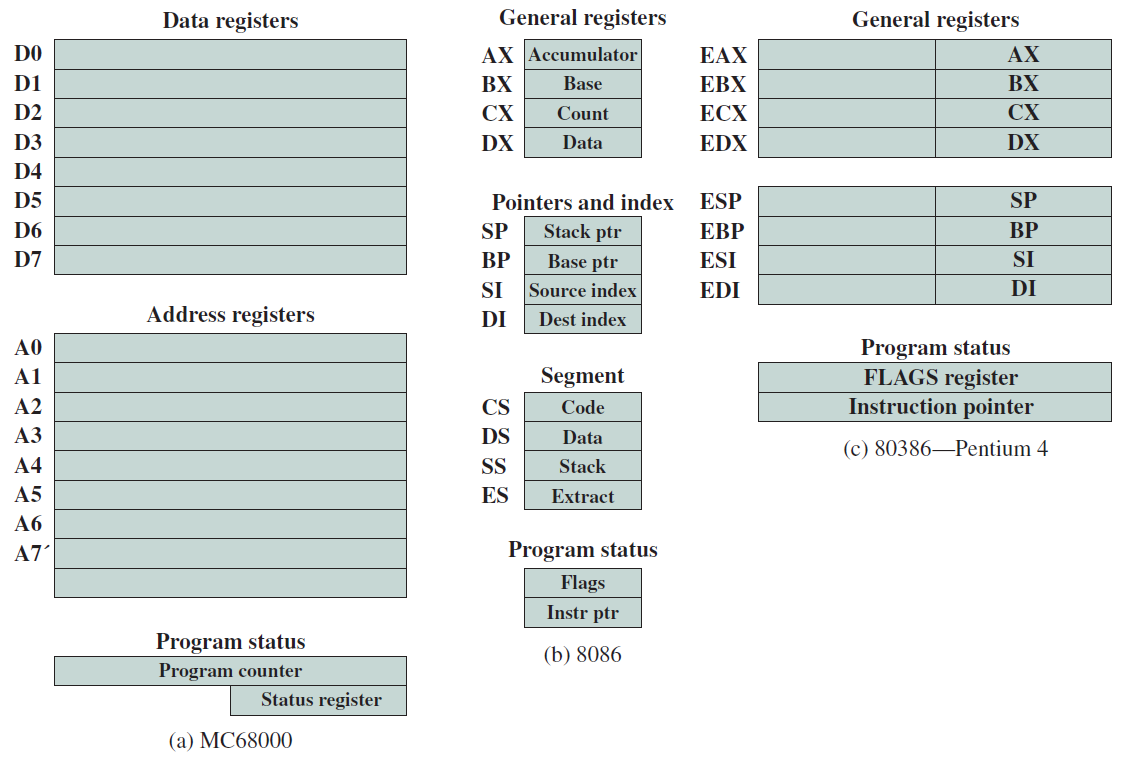

每臺機器都有一組暫存器,這些暫存器對組合程式設計師是可見的。ARM有16個暫存器,x86(32位元)有8個暫存器,而x86_64(64位元)有16個。暫存器有名稱,ARM將它們命名為r0、r1、...、r14、r15,x86將它們命名成eax、ebx、ecx、edx、esi、edi、ebp和esp,可以使用這些名稱存取暫存器。

在大多數ISA中,返回地址暫存器用於函數呼叫。讓我們假設一個程式開始執行一個函數,它需要記住執行函數後需要返回的記憶體地址,此地址稱為返回地址。在跳轉到函數的起始地址之前,我們可以將返回地址的值儲存在這個暫存器中。通過將儲存在返回地址暫存器中的值複製到PC上,可以簡單地實現返回語句。在ARM和MIPS等組合語言中,程式設計師可以看到返回地址暫存器,然而x86不使用返回地址暫存器,使用堆疊。

在ARM處理器中,程式設計師可以看到PC,它是最後一個暫存器(r15)。可以讀取PC的值,也可以設定其值,設定PC的值意味著我們希望分支到程式中的新位置。然而x86的PC是隱式的,程式設計師不可見。

記憶體檢視

記憶體可以看作是一個大的位元組陣列,每個位元組都有一個唯一的地址,基本上就是它在陣列中的位置。第一位元組的地址是0,第二位元組的地址為1,以此類推。我們沒有一種方法來唯一地定址給定的位,地址在32位元機器中是32位元無符號整數,在64位元機器中則是64位元無符號。

在馮·諾依曼機器中,我們假設程式作為位元組序列儲存在記憶體中,程式計數器指向將要執行的下一條指令。

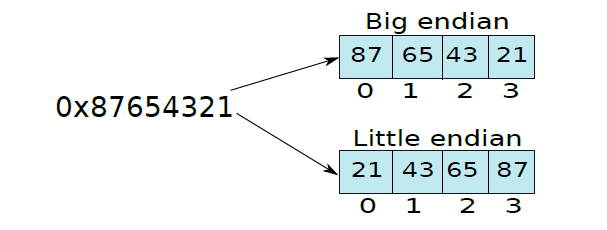

假設記憶體是一個大的位元組陣列,如果我們所有的資料項都只有一個位元組長,那麼就可以了,像C和Java這樣的語言有不同大小的資料型別:char(1位元組)、short(2位元組)、integer(4位元組)和long integer(8位元組)。對於多位元組資料型別,必須在記憶體中為其建立一個表示,在記憶體中表示多位元組資料型別有兩種可能的方式——小端和大端。其次,我們還需要找到表示記憶體中資料陣列或列表的方法。

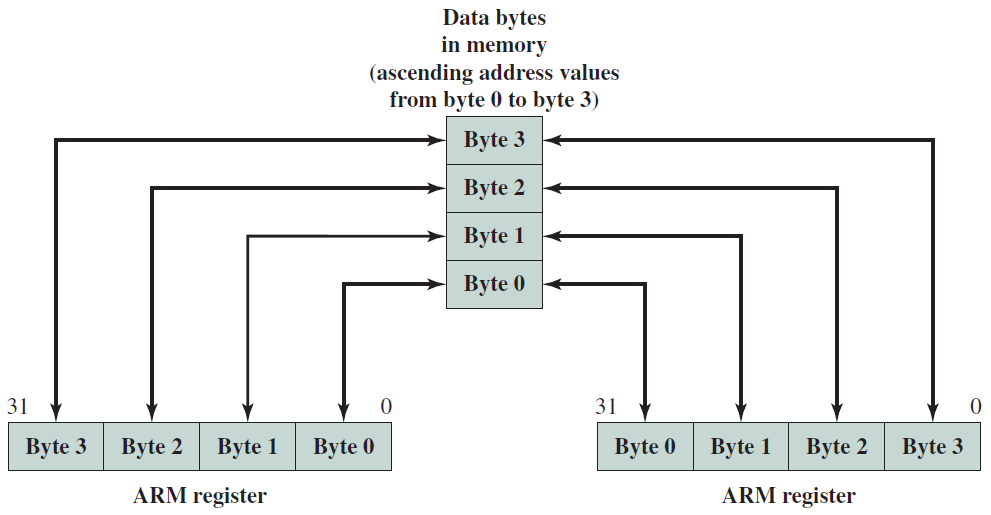

- 小端和大端表示

讓我們考慮在位置0-3儲存整數的問題。讓整數為0x87654321,它可以分為四個位元組:87、65、43和21。一個選項是將最重要的位元組87儲存在最低的記憶體地址0中,下一個位置可以儲存65、43、21,這被稱為大端(big endian)表示,因為我們從最大位元組的位置開始。相比之下,我們可以先將最小的位元組儲存在位置0,然後繼續將最大的位元組儲存在位置3,這種表示方式稱為小端(big endian)。下圖顯示了差異。

大端和小端表示。

因此,沒有理由選擇一種代表而不是另一種代表,例如,x86處理器使用little-endian格式。早期版本的ARM處理器曾經是小端的,然而,現在它們是雙端的,意味著ARM處理器可以根據使用者設定同時作為小端和大端機器工作。傳統上,IBM POWER處理器和Sun SPARC處理器都是大端的。

- 表示陣列

陣列是一組線性有序的物件,其中物件可以是簡單的資料型別(如整數或字元),也可以是複雜的資料型別。

int a[100];

char c[100];

讓我們考慮一個簡單的整數陣列a。如果陣列有100個條目,那麼記憶體中陣列的總大小等於100 4=400位元組。如果陣列的起始記憶體位置為loc,然後將[0]儲存在位置(loc + 0)、(loc + 1)、(loc + 2)、(loc + 3)中。請注意,有大端和小端兩種方法儲存資料。下一個陣列條目a[1]儲存在位置(loc + 4) ... (loc + 7)中,依此類推,我們注意到條目a[i]儲存在(loc + 4 x i) ... (loc + 4 x i + 3)中。

大多數程式語言都定義以下形式的多維陣列:

int a[100][100];

char c[100][100];

它們通常在記憶體中表示為規則的一維陣列,多維陣列中的位置與等效的一維陣列之間存在對映函數,我們可以擴充套件該方案以考慮維度大於2的多維陣列。

我們觀察到,通過以行優先(row major)方式儲存二維陣列,可以將其儲存為一維陣列,意味著資料按行儲存。我們儲存第一行,然後儲存第二行,以此類推。同樣,也可以以列優先(column major)的方式儲存多維陣列,其中儲存第一列,然後再儲存第二列,依此類推。

行優先(row major):陣列按行儲存在記憶體中。

列優先(column major):陣列按列儲存在記憶體中。

19.2.1.3 組合語言語法

組合檔案的確切語法取決於組合程式,不同的組合程式可以使用不同的語法,儘管它們可能在基本指令及其運算元格式上達成一致。本節將解釋GNU系列組合語言的語法,它們是為GNU組合程式設計的,是GNU編譯器集合(gcc)的一部分。與所有GNU軟體一樣,該組合程式和相關編譯器可免費用於大多數平臺,組合程式可在gnu.org上找到。請注意,其他組合程式(如NASM、MASM)都有自己的格式,但總體結構在概念上與本節描述的沒有太大區別。

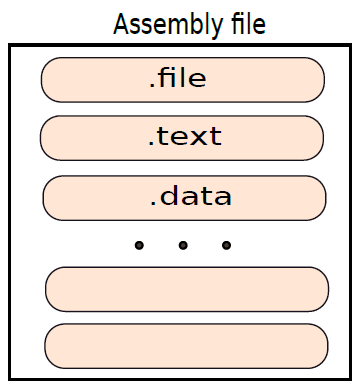

組合檔案結構

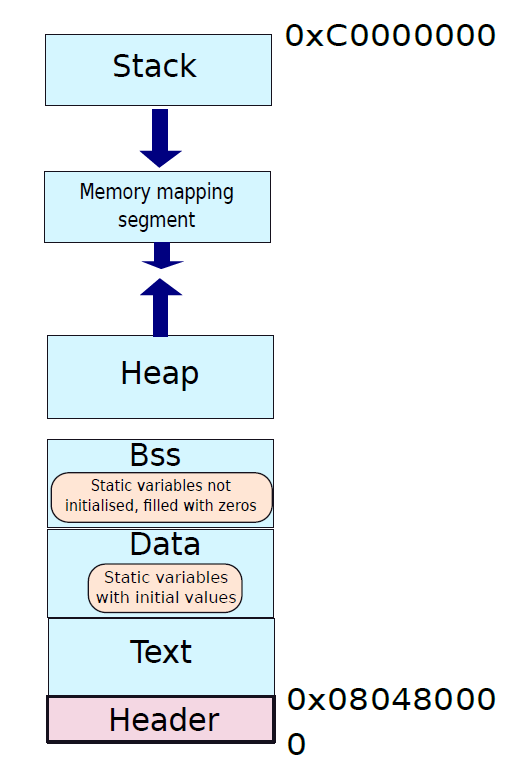

程式集檔案是一個常規文字檔案,字尾是.s。如果安裝了GNU編譯器gcc,則可以通過發出以下命令快速生成C程式的組合檔案,當然也可以使用線上GCC。

gcc -S test.c

生成的程式集檔案將命名為test.s。GNU程式集的結構非常簡單,如下圖所示。不同部分的範例包括文字(實際程式)、資料(具有初始化值的資料)和bss(初始化為0的通用資料)。每個段(section)以節標題開頭,這是以「.」開頭的節的名稱符號,例如,文字部分以「.text」行開頭。接著是組合語言語句列表,每條語句通常以換行符結尾,同樣,資料部分包含資料值列表。

組合檔案以包含格式為「.file <檔名>」的行的檔案段開頭。當我們使用gcc編譯器從C程式生成程式集檔案時,.file部分中的檔名通常與我們的原始C程式(test.C)相同。文欄位是必填的,其餘段是可選的,可能有一個或多個資料段,也可以使用.section指令定義新的節。本節我們主要關注文字部分,因為對學習指令集的本質感興趣。

組合語言檔案結構。

組合基本語句

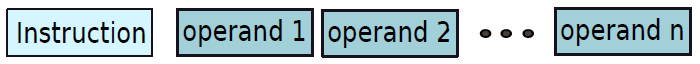

一條基本的組合語言語句指定了一條組合指令,有兩部分:指令及其運算元列表,如下圖所示。該指令是實際機器指令的文字識別符號,運算元列表包含每個運算元的值或位置。運算元的值是一個數值常數,也被稱為立即值(immediate value),運算元位置可以是暫存器位置或記憶體位置。

組合語言語句。

在計算機架構中,指令中指定的常數值也稱為立即數(immediate)。

假設有以下語句:

add r3, r1, r2

在這個ARM組合語句中,add指令指定了我們希望將兩個數位相加並將結果儲存在某個預先指定的位置的事實。在這種情況下,加法指令的格式如下:<指令><目標暫存器><運算元暫存器1><運算元暫存器2>。指令的名稱為add,目標暫存器為r3,運算元暫存器為r1和r2。指令的詳細步驟如下:

1.讀取暫存器r1的值。讓我們將該值稱為v1。

2.讀取暫存器r2的值。讓我們將該值稱為v2。

3.計算v3=v1+v2。

4.將v3儲存在暫存器r3中。

現在讓我們再舉一個以類似方式工作的兩條指令的範例:

sub r3, r1, r2

mul r3, r1, 3

sub指令減去儲存在暫存器中的兩個數,mul指令將儲存在暫存器r1中的一個數乘以數值常數3,這兩條指令都將結果儲存在暫存器r3中,它們的操作模式與加法指令類似。此外,算術指令(如add、sub和mul)也稱為資料處理指令。還有其他幾類指令,例如從記憶體載入或儲存值的資料傳輸指令,以及實現分支的控制指令。

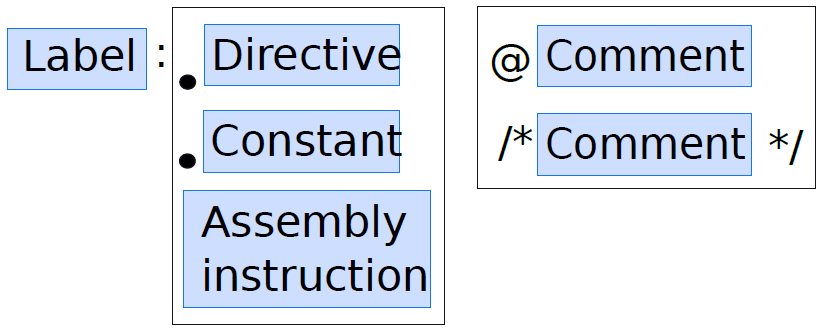

通用語句結構

組合語句的一般結構如下圖所示,它由三個欄位組成:標籤(指令的識別符號)、鍵(組合指令或組合程式指令)和註釋。這三個欄位都是可選的,但是,任何組合語句都需要至少具有其中一個。

組合語句的通用結構。

語句可以選擇以標籤開頭,標籤是語句的文字識別符號,換句話說,標籤在組合中唯一地標識組合語句。請注意,我們不允許在同一組合檔案中重複標籤,標籤在執行分支指令時非常有用。

下面的範例程式碼中顯示了一個標籤的範例,這裡標籤的名稱是「label1」,後面是冒號。在標籤之後,我們編寫了一條組合指令,並給它一個運算元列表。標籤可以由有效的字母數位字元[a-z] [A-Z] [0-9] 以及符號「.」、「_」和「$」。通常,我們不能以數位作為標籤的開頭。在指定標籤之後,我們可以將該行保持為空,也可以指定鍵(組合語句的一部分)。如果鍵以「.」開頭,那麼它是一個組合程式指令,對所有計算機都有效,它指示組合程式執行某個操作,此操作可以包括啟動新節或宣告常數。該指令還可以採用參數列,如果鍵以字母開頭,則它是一條常規的組合指令。

label1: add r1, r2, r3

在標籤、組合指令和運算元列表之後,可以選擇插入註釋。GNU組合程式支援兩種型別的註釋,我們可以在插入類似C或Java風格的註釋。在ARM組合中,通過在註釋前面加上「@」字元,也可以有一個小的單行註釋。

label1: add r1, r2, r3 @ Add the values in r2 and r3

label2: add r3, r4, r5 @ Add the values in r4 and r5

add r5, r6, r7 /* Add the values in r6 and r7 */

組合語句可能只包含標籤,而不包含鍵。在這種情況下,標籤本質上指向一個空語句,不是很有用。因此,組合程式假定在這種情況下,標籤指向最近的包含鍵的後續組合語句。

19.2.1.4 指令型別

按功能分類

按功能,可分為四種主要型別,說明如下:

- 資料處理指令:資料處理指令通常是算術指令,如加法、減法和乘法,或按位元或、互斥或計算的邏輯指令,比較指令也屬於這個型別。

- 資料傳輸指令:這些指令在兩個位置之間傳輸值,位置可以是暫存器或記憶體地址。

- 分支指令:分支指令幫助處理器的控制單元根據運算元的值跳轉到程式的不同部分,在實現for迴圈和if-then-else語句時很有用。

- 異常生成指令:這些專用指令有助於將控制權從使用者級程式轉移到作業系統。

我們將介紹資料處理、資料傳輸和控制指令。

按運算元分類

GNU組合程式中的所有組合語言語句都具有相同的結構,它們以指令的名稱開頭,後面是運算元列表。我們可以根據指令所需的運算元對其進行分類,如果一條指令需要n個運算元,那麼通常稱它是n地址格式,例如,不需要任何運算元的指令是0地址格式指令,如果它需要3個運算元,則它是3地址格式指令。

如果一條指令需要n個運算元(包括源和目標),那麼我們稱其為n地址格式指令。

在ARM中,大多數資料處理指令採用3地址格式,資料傳輸指令採用2地址格式。然而,在x86中,大多數指令都是2地址格式。我們想到的第一個問題是,3地址格式指令與2地址格式指令的邏輯是什麼?這裡一定有一些權衡。

讓我們闡述一些一般的經驗法則。如果一條指令有更多的運算元,那麼它將需要更多的位來表示該指令,因此需要更多的資源來儲存和處理指令。然而,這一論點有另一面,擁有更多的運算元也會使指令更加通用和靈活,將使編譯器編寫者和組合程式設計師的生活變得更加輕鬆,因為使用更多運算元的指令可以做更多的事情。反向邏輯適用於佔用較少運算元的指令,佔用更少的儲存空間,也不那麼靈活。

讓我們考慮一個例子。假設我們試圖將兩個數位3和5相加,得到結果8。用於新增的ARM指令如下所示:

add r3, r1, r2

此指令將暫存器r1(3)和r2(5)的內容相加,並將其儲存在r3(8)中。然而,x86指令如下所示:

add edx, eax

此處假設edx包含3,eax包含5,執行加法,結果8儲存回edx。因此,在這種情況下,x86指令採用2地址格式,因為目標暫存器與第一源暫存器相同。

19.2.1.5 運算元型別

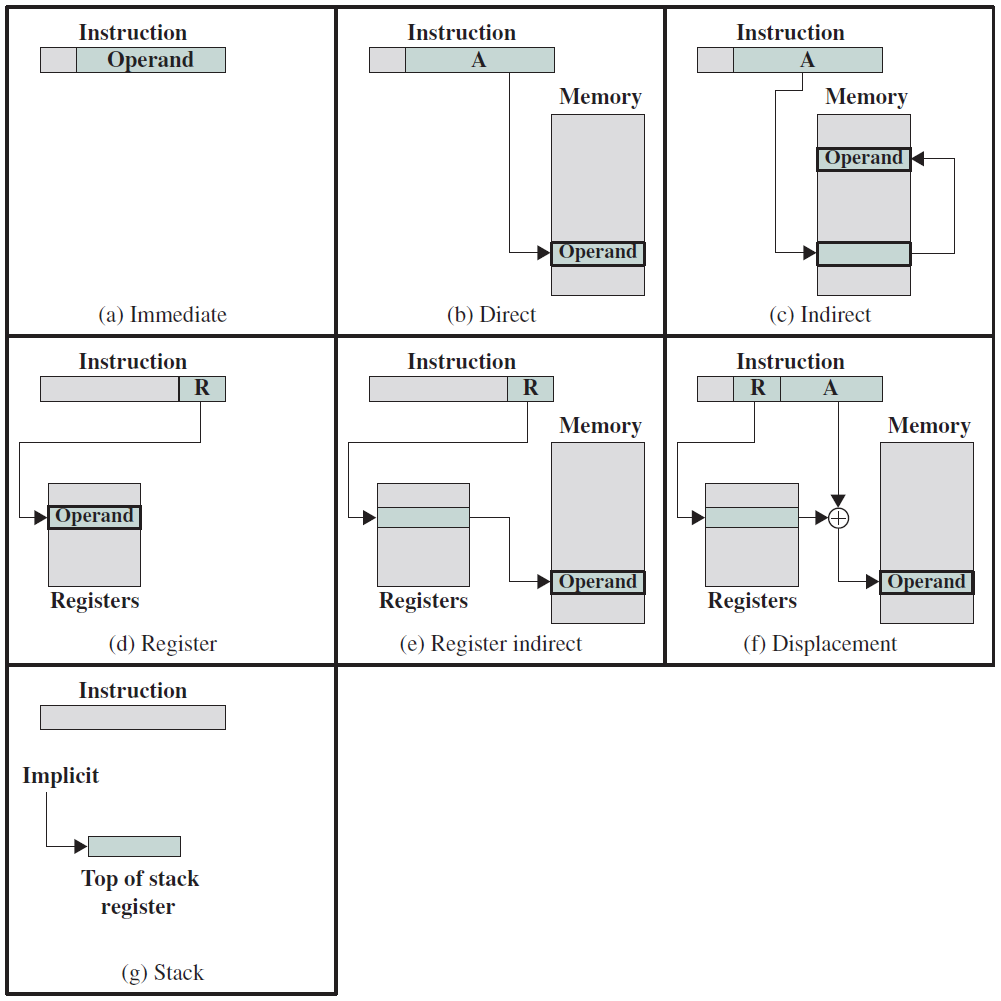

現在讓我們看看不同型別的運算元,在組合語句中指定和存取運算元的方法稱為定址模式。

在組合語句中指定和存取運算元的方法稱為定址模式(addressing mode)。

指定運算元的最簡單方法是將其值嵌入指令中,大多數組合語言允許使用者將整數常數的值指定為運算元,這種定址模式被稱為立即定址模式(immediate addressing mode),此方法對於初始化暫存器或記憶體位置或執行算術運算非常有用。

一旦必需的常數集被載入到暫存器和記憶體位置,程式就需要通過對暫存器和記憶體進行操作來繼續,這個空間有幾種定址模式。在介紹它們之前,讓我們以暫存器轉移符號(register transfer notation)的形式介紹一些額外的術語。

暫存器轉移符號

這個符號允許我們指定指令和運算元的語意,讓我們看看錶示指令基本動作的各種方法:

此表示式有兩個暫存器運算元r1和r2,r1是目標暫存器,r2是源暫存器,我們正在將暫存器r2的內容轉移到暫存器r1。我們可以用一個常數指定一個加法運算,如下所示:

我們還可以使用此符號指定暫存器上的操作,將r2和r3的內容相加,並將結果儲存在r1中:

也可以使用此符號表示記憶體存取:

上述語句中,記憶體地址等於暫存器r2的內容加4,然後從該記憶體地址的內容開始提取整數,並將其儲存在暫存器r1中。

運算元的通用定址模式

讓我們將運算元的值表示為V。在隨後的討論中,我們使用了\(V\leftarrow r1\)等表示式,並不意味著我們有一個新的稱為V的儲存位置,意味著運算元的數值由RHS指定(右側)。讓我們通過範例簡要地看一下一些最常用的定址模式:

- 立即:\(V\leftarrow imm\)。使用常數imm作為運算元的值。

- 暫存器:\(V\leftarrow r1\)。在此定址模式下,處理器使用暫存器中包含的值作為運算元。

- 暫存器間接:\(V\leftarrow [r1]\)。暫存器儲存包含該值的記憶體位置的地址。

- 基準偏移量:\(V\leftarrow [r1 + offset]\)。offset是一個常數,處理器從r1獲取基本記憶體地址,將常數offset新增到該地址,然後存取新的記憶體位置以獲取運算元的值。offset也稱為位移。

- 基址變址:\(V\leftarrow [r1 + r2]\)。r1是基址暫存器,r2是索引暫存器,記憶體地址等於(r1+r2)。

- 基址變址偏移:\(V\leftarrow [r1 + r2 + offset]\)。包含該值的記憶體地址為(r1+r2+offset),其中offset為常數。

- 記憶體直接:\(V\leftarrow addr\)。該值從地址addr開始包含在記憶體中,addr是一個常數。在這種情況下,記憶體地址直接嵌入指令中。

- 記憶體間接:\(V\leftarrow [[r1]]\)。該值存在於記憶體位置中,其地址包含在記憶體位置M中,M的地址包含在暫存器r1中。

- PC相關:\(V\leftarrow [PC + offset]\)。offset量是一個常數,記憶體地址計算為PC+offset,其中PC表示PC中包含的值。此定址模式對分支指令很有用,注意此處的PC是指程式計數器。

讓我們通過考慮基偏移定址模式來引入一個稱為有效記憶體地址(effective memory address)的新術語。記憶體地址等於基址暫存器的內容加上偏移量,計算出的記憶體地址稱為有效記憶體地址。在記憶體運算元的情況下,我們可以類似地為其他定址模式定義有效地址。

多種定址模式。

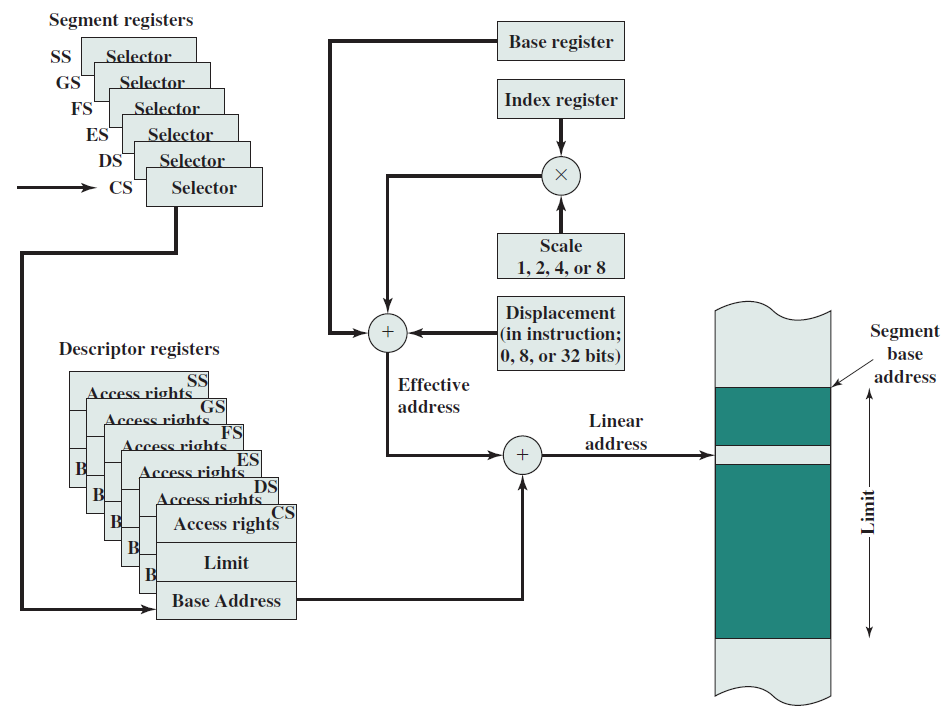

x86定址模式計算。

19.2.1.6 常見指令說明

本小節將以ARM為基準,闡述常見的RISC指令用法。

資料傳輸指令

資料傳輸指令包含以下幾類:

- LDR和STR

可載入暫存器和儲存暫存器,包含32位元字、8位元無符號位元組、半字、無符號位元組、雙字等。

LDR和STR都有四種可能的形式:零偏移量、預索引偏移、程式相關、後索引偏移。四種形式的語法順序相同,分別為:

op{cond}{B}{T} Rd, [Rn]

op{cond}{B} Rd, [Rn, FlexOffset]{!}

op{cond}{B} Rd, label

op{cond}{B}{T} Rd, [Rn], FlexOffset

以上是針對32位元字或8位元無符號位元組,如果需要雙字則B改成D:

op{cond}D Rd, [Rn]

op{cond}D Rd, [Rn, Offset]{!}

op{cond}D Rd, label

op{cond}D Rd, [Rn], Offset

半字、有符號位元組語法如下:

op{cond} type Rd, [Rn]

op{cond} type Rd, [Rn, Offset]{!}

op{cond} type Rd, label

op{cond} type Rd, [Rn], Offset

範例:

; 範例1

SUB R1, PC, #4 ; R1 = address of following STR instruction

STR PC, [R0] ; Store address of STR instruction + offset,

LDR R0, [R0] ; then reload it

SUB R0, R0, R1 ; Calculate the offset as the difference

; 範例2

LDRD r6,[r11]

LDRMID r4,[r7],r2

STRD r4,[r9,#24]

STRD r0,[r9,-r2]!

LDREQD r8,abc4

; 範例3

LDREQSH r11,[r6] ; (conditionally) loads r11 with a 16-bit halfword from the address in r6. Sign extends to 32 bits.

LDRH r1,[r0,#22] ; load r1 with a 16 bit halfword from 22 bytes above the address in r0. Zero extend to 32 bits.

STRH r4,[r0,r1]! ; store the least significant halfword from r4 to two bytes at an address equal to contents(r0) plus contents(r1). Write address back into r0.

LDRSB r6,constf ; load a byte located at label constf. Sign extend.

- LDM和STM

LDM、STM載入和儲存多個暫存器,暫存器r0到r15的任何組合都可以被傳送。語法如下:

op{cond}mode Rn{!}, reglist{^}

範例:

LDMIA r8,{r0,r2,r9}

STMDB r1!,{r3-r6,r11,r12}

STMFD r13!,{r0,r4-r7,LR} ; Push registers including the stack pointer

LDMFD r13!,{r0,r4-r7,PC} ; Pop the same registers and return from subroutine

- PLD

PLD快取預載入。語法:

PLD [Rn{, FlexOffset}]

範例:

PLD [r2]

PLD [r15,#280]

PLD [r9,#-2481]

PLD [r0,#av*4] ; av * 4 must evaluate, at assembly time, to an integer in the range -4095 to +4095

PLD [r0,r2]

PLD [r5,r8,LSL 2]

- SWP

在暫存器和記憶體之間交換資料,使用SWP實現號誌。語法:

SWP{cond}{B} Rd, Rm, [Rn]

通用資料處理指令

此類指令又包含以下幾種:

- 靈活第二運算元

大多數ARM通用資料處理指令都有一個靈活的第二運算元,在每條指令的語法描述中顯示為Operand2。語法有兩種形式:

#immed_8r

Rm{, shift}

範例:

ADD r3,r7,#1020 ; immed_8r. 1020 is 0xFF rotated right by 30 bits.

AND r0,r5,r2 ; r2 contains the data for Operand2.

SUB r11,r12,r3,ASR #5 ; Operand2 is the contents of r3 divided by 32.

MOVS r4,r4, LSR #32 ; Updates the C flag to r4 bit 31. Clears r4 to 0.

- ADD、SUB、RSB、ADC、SBC和RSC

此類指令的語法如下:

op{cond}{S} Rd, Rn, Operand2

範例:

ADD r2,r1,r3

SUBS r8,r6,#240 ; sets the flags on the result

RSB r4,r4,#1280 ; subtracts contents of r4 from 1280

ADCHI r11,r0,r3 ; only executed if C flag set and Z flag clear

RSCLES r0,r5,r0,LSL r4 ; conditional, flags set

- AND、ORR、EOR和BIC

邏輯操作,語法如下:

op{cond}{S} Rd, Rn, Operand2

範例:

AND r9,r2,#0xFF00

ORREQ r2,r0,r5

EORS r0,r0,r3,ROR r6

BICNES r8,r10,r0,RRX

- MOV、MVN、CMP、CMN、TST、TEQ、CLZ

移動、對比、測試、計數前導零指令,語法如下:

MOV{cond}{S} Rd, Operand2

MVN{cond}{S} Rd, Operand2

CMP{cond} Rn, Operand2

CMN{cond} Rn, Operand2

TST{cond} Rn, Operand2

TEQ{cond} Rn, Operand2

CLZ{cond} Rd, Rm

範例:

MOV r5,r2

MVNNE r11,#0xF000000B

MOVS r0,r0,ASR r3

CMP r2,r9

CMN r0,#6400

CMPGT r13,r7,LSL #2

TST r0,#0x3F8

TEQEQ r10,r9

TSTNE r1,r5,ASR r1

CLZ r4,r9

CLZNE r2,r3

算術指令

算術指令包含大量的乘法指令,乘法的指令較多較複雜。常見算術指令如下表所示:

| 指令 | 語法 | 說明 |

|---|---|---|

| MUL、MLA | MUL{cond}{S} Rd, Rm, Rs MLA{cond}{S} Rd, Rm, Rs, Rn |

乘法和乘法累加(32位元乘32位元,取底部32位元結果) |

| UMULL、UMLAL、SMULL、SMLAL | Op{cond}{S} RdLo, RdHi, Rm, Rs | 無符號和有符號長乘法和乘法累加(32位元乘32位元,64位元累加或結果)。 |

| SMULxy、SMLAxy、SMULWy、SMLAWy、SMLALxy | SMLA SMULW SMLAW |

有符號乘法(16、32位元乘16、32位元,結果是32位元或64位元,部分指令有累積)。 |

| MIA、MIAPH、MIAxy | MIA{cond} Acc, Rm, Rs MIA |

XScale協處理器0指令。 |

範例:

MUL r10,r2,r5

MLA r10,r2,r1,r5

MULS r0,r2,r2

MULLT r2,r3,r2

MLAVCS r8,r6,r3,r8

UMULL r0,r4,r5,r6

UMLALS r4,r5,r3,r8

SMLALLES r8,r9,r7,r6

SMULLNE r0,r1,r9,r0 ; Rs can be the same as other registers

SMLAWB r2,r4,r7,r1

SMLAWTVS r0,r0,r9,r2

MIA acc0,r5,r0

MIALE acc0,r1,r9

MIAPH acc0,r0,r7

MIAPHNE acc0,r11,r10

MIABB acc0,r8,r9

MIABT acc0,r8,r8

MIATB acc0,r5,r3

MIATT acc0,r0,r6

MIABTGT acc0,r2,r5

分支指令

分支語句的描述如下表:

| 指令 | 語法 | 說明 |

|---|---|---|

| B、BL | B/BL {cond} label | 分支和帶連結的分支 |

| BX | BX{cond} Rm | 分支和交換指令集 |

| BLX | BLX{cond} Rm BLX label |

使用Link分支,並可選地交換指令集。本說明有兩種可選形式: 1、連結到程式相對地址的無條件分支 2、與暫存器中儲存的絕對地址連結的條件分支。 |

範例:

B loopA

BLE ng+8

BL subC

BLLT rtX

BX r7

BXVS r0

BLX r2

BLXNE r0

BLX thumbsub

條件執行

幾乎所有ARM指令都可以包含可選條件程式碼。這在語法描述中顯示為{cond}。只有當CPSR中的條件程式碼標誌滿足指定條件時,才執行帶有條件程式碼的指令。可以使用的條件程式碼如下表所示(部分)。

| 字尾 | 標記 | 含義 |

|---|---|---|

| EQ | Z設定 | = |

| NE | Z清除 | != |

| CS、HS | C設定 | >=(無符號) |

| CC、LO | C清除 | =(無符號) |

| MI | N設定 | 負數 |

| PL | N清除 | 非負數 |

| VS | V設定 | 溢位 |

| VC | V清除 | 無溢位 |

| HI | C設定且Z清除 | >(無符號) |

| LS | C清除或Z設定 | <=(無符號) |

| GE | N和V一樣 | >=(有符號) |

| LT | N和V不一樣 | <(有符號) |

| GT | Z清除且N和V一樣 | >(有符號) |

| LE | Z設定或N和V不一樣 | <=(有符號) |

| AL | 任意 | 總是(通常省略) |

幾乎所有ARM資料處理指令都可以根據結果選擇性地更新條件程式碼標誌。要使指令更新標誌,請包含S字尾,如指令的語法描述所示。

有些指令(CMP、CMN、TST和TEQ)不需要S字尾,它們的唯一功能是更新標誌,總是更新標誌。

標誌將保留到更新,未執行的條件指令對標誌沒有影響,一些指令更新標誌的子集,其他標誌不受這些指令的影響。詳細資訊在說明說明中指定。可以根據另一條指令中設定的標誌,有條件地執行指令,或者:

- 緊接在更新標誌的指令之後。

- 在沒有更新標誌的任何數量的介入指令之後。

範例:

ADD r0, r1, r2 ; r0 = r1 + r2, don't update flags

ADDS r0, r1, r2 ; r0 = r1 + r2, and update flags

ADDCSS r0, r1, r2 ; If C flag set then r0 = r1 + r2, and update flags

CMP r0, r1 ; update flags based on r0-r1.

其它指令

ARM還有協調處理器、偽指令、雜項指令等其它指令,本文限於篇幅就不接受了。更多詳情參見:

19.2.2 二進位制位

計算機不像人類那樣理解單詞或句子,只理解0和1的序列,儲存、檢索和處理數十億個0和1非常容易。其次,使用矽電晶體(silicon transistor)實現計算機的現有技術與處理0和1的概念非常相容。基本矽電晶體是一種開關,可以根據輸入將輸出設定為邏輯0或1,矽電晶體是我們今天擁有的所有電子計算機的基礎,從手機的處理器到超級計算機的處理器。十九世紀末製造的一些早期計算機處理十進位制數位,本質上大多是機械的。首先讓我們明確定義一些簡單的術語:

位(bit):可以有兩個值的變數:0或1。

位元組(byte):8個位的序列。

19.2.2.1 邏輯操作

二進位制變數(0或1)最早由喬治·布林(George Boole)於1854年描述,他使用這些變數及其相關運算來描述數學意義上的邏輯,他設計了一個完整的代數,由簡單的二元變數、一組新的運運算元和基本運算組成。為了紀念喬治·布林,二進位制變數也稱為布林變數(Boolean variable),布林變數的代數系統稱為布林代數(Boolean algebra)。邏輯位元運算如下:

- NOT

邏輯二補數(logical complement)稱為NOT運運算元,任何布林運運算元都可以通過真值表來表示,真值表列出了所有可能的輸入組合的運運算元輸出,NOT運運算元的真值表如下表所示。

| 原始值 | NOT操作後 |

|---|---|

| 0 | 1 |

| 1 | 0 |

- OR

OR運運算元表示任一運算元等於1的事實。例如,如果A=1或B=1,則A或B等於1。OR運運算元的真值表如下所示。

| A | B | A OR B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

- AND

AND運運算元的操作是所有運算元為1,則結果才為1,其它則為0。例如,當A和B都為1時,A和B等於1。AND運運算元的真值表如下所示。

| A | B | A AND B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

- NAND、NOR

另外的兩個簡單的運運算元,即NAND和NOR非常有用。NAND是AND的邏輯二補數,NOR是OR的邏輯補。它們的真值表如下所示。

| A | B | A NAND B | A NOR B |

|---|---|---|---|

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

NAND和NOR是非常重要的運運算元,因為它們被稱為通用運運算元,我們可以只使用它們來構造任何其他運運算元。

- XOR

XOR是互斥或運運算元,當A和B相等時,值為0,否則為1。真值表如下所示。

| A | B | A XOR B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

19.2.2.2 布林代數

讓我們來看看NOT運運算元的一些規則:

- 定義:\(\overline{0}=1, \text { 且 } \overline{1}=0\),即NOT運運算元的定義。

- 雙重否定:\(\overline{\overline{A}}=A\),非A的非等於A本身。

OR和AND運運算元:

- 恆等式:A+0=A,A.1=A,亦即如果計算布林變數A與0的OR或與1的AND,結果等於A。

- 相消性:A+1=1,A.0=0,亦即如果計算A OR 1,那麼結果總是等於1。類似地,A AND 0總是等於0,因為第二個運算元的值決定了最終結果。

- 冪等性:A+A=A,A.A=A,亦即計算A與自身的OR或AND的結果為A。

- 互補性:A+\(\overline{A}\)=1,A.\(\overline{A}\)=0,亦即A=1或\(\overline{A}\)=1。在任何一種情況下,A+\(\overline{A}\)都有一個項,它是1,因此結果是1。同樣,A.\(\overline{A}\)中的一個項是0,因此結果為0。

- 交換性:A.B=B.A,A+B=B+A,亦即布林變數的順序無關緊要。

- 關聯性:A+(B+C) = (A+B)+C,以及A.(B.C)=(A.B).C。

- 分配性:A.(B+C) = A.B+A.C,A+B.C=(A+B).(A+C),亦即可以使用這個定律來開啟括號並簡化表示式。

我們可以使用這些規則以各種方式操作包含布林變數的表示式,下面看看布林代數中的一組基本定理。

- 摩根定律(De Morgan's Laws)

有兩個摩根定律可以通過構造LHS和RHS的真值表來驗證。

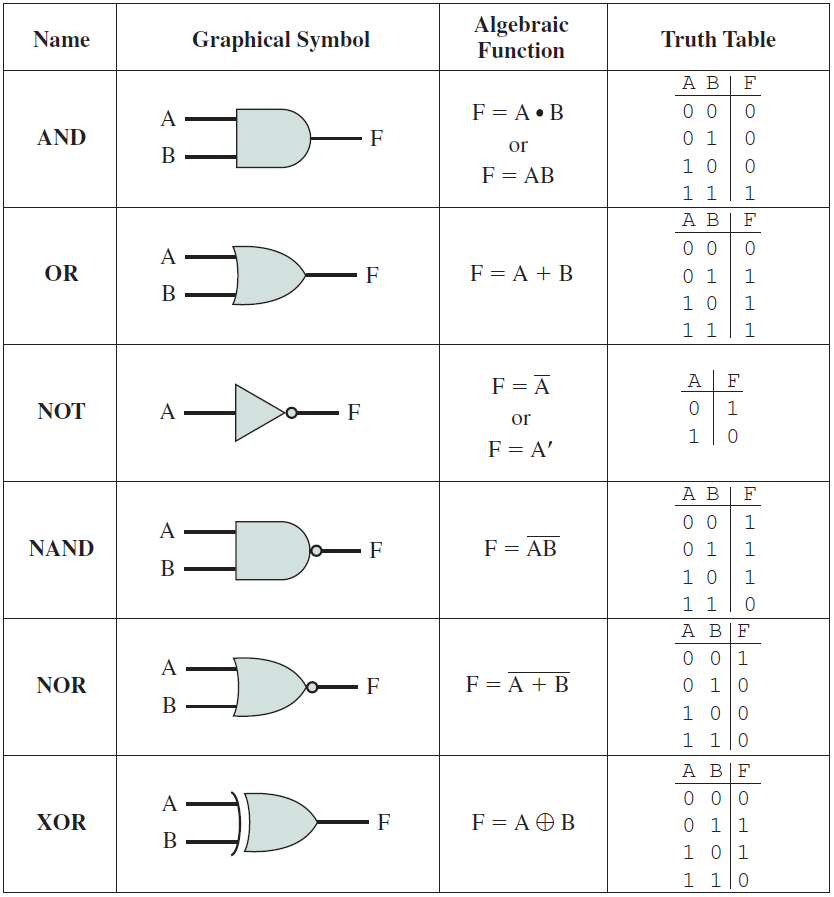

- 邏輯閘(Logic Gate)

現在讓我們嘗試實現電路來實現複雜的布林公式,「邏輯閘」定義為實現布林函數的器件,可以由矽、真空管或任何其他材料製成。

邏輯閘是實現布林函數的裝置。

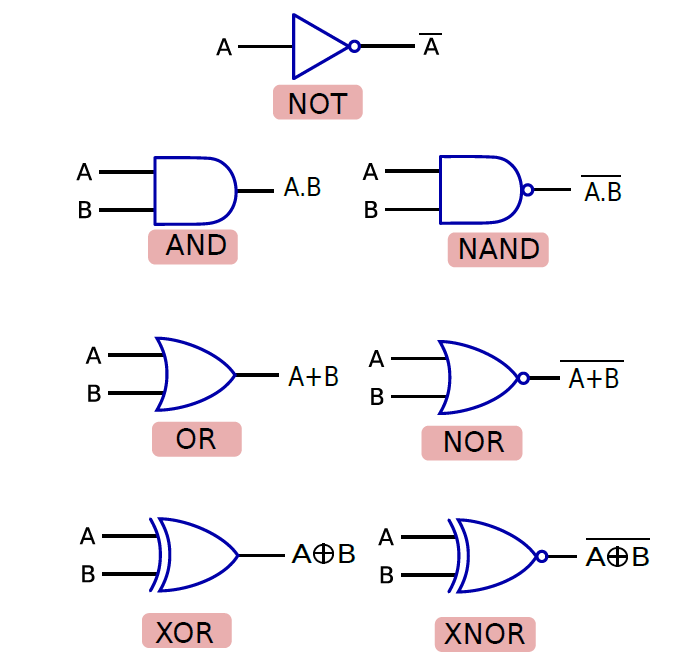

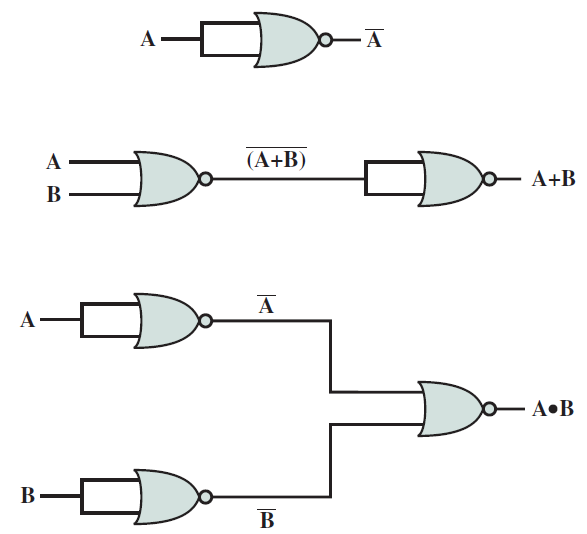

給定一組邏輯閘,我們可以設計一個電路來實現任何布林函數,不同邏輯閘的符號如下圖所示。

邏輯閘列表。

19.2.3 電晶體

矽是週期表中的第14種元素,有四個價電子,雖然與碳和鍺屬於同一組,但其化學反應性不如後兩者。

90%以上的地殼由矽基礦物組成,二氧化矽是沙子和石英的主要成分,它供應充足,而且製造起來相當便宜。矽具有一些有趣的特性,使其成為設計電路和處理器的理想襯底。讓我們考慮一下矽的分子結構,它有一個緻密的結構,每個矽原子都與其他四個矽原子相連,緊密相連的一組矽原子結合在一起形成一個強晶格,其他材料(尤其是金剛石)具有類似的晶體結構。因此,矽原子比大多數金屬更緊密。

由於缺乏自由電子,矽沒有很好的導電效能,介於良導體和絕緣體之間,因此被稱為半導體(semiconductor)。通過可控的方式新增一些雜質,可以稍微改變其性質,這個過程被稱為摻雜(doping)。

19.2.3.1 摻雜

通常,向矽中新增兩種雜質以改變其特性:n型和p型。n型雜質通常由週期表中的V族元素組成,磷是最常見的n型摻雜劑,偶爾也會使用砷。新增具有價電子的V族摻雜劑的效果是,額外的電子從晶格中分離出來,並可用於傳導電流。這種摻雜過程有效地提高了矽的導電性。

同樣,可以向矽中新增III族元素,如硼或鎵,以產生p型摻雜矽,會產生相反的效果,會在晶格中建立一個空隙,此空隙也稱為孔(hole),孔表示沒有電子。像電子一樣,孔可以自由移動,也有助於傳導電流。電子帶負電荷,孔在概念上與正電荷相關。

現在我們已經制作了兩種半導體材料:n型和p型,下面看看如果連線它們形成p-n結會發生什麼。

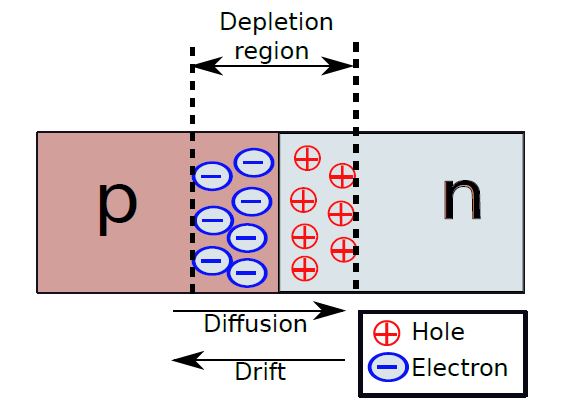

19.2.3.2 P-N結

讓我們考慮一個p-n結,如下圖所示。p型區有過量的孔,n型區有過剩的電子。在結處,一些孔交叉並移動到n區,因為它們被電子吸引。類似地,一些電子越過並聚集在p區一側。孔和電子的這種遷移稱為擴散,見證這種遷移的交界處周圍的區域被稱為耗盡區。然而,由於電子和孔的遷移,在耗盡區中產生了與遷移方向相反的電場,這個電場感應出一種稱為漂移電流的電流。在穩態下,漂移電流和擴散電流相互平衡,因此實際上沒有電流流過結。

如果將p側連線到正端子,將n側連線到負端子,則這種設定稱為正向偏置。在這種情況下,孔從結的p側流向n側,電子則反向流動。因此,該結傳導電流。

如果我們將p側連線到負端子,將n側連線到正端子,則這種設定稱為反向偏置。在這種情況下,孔和電子被拉離結。因此,沒有電流流過結,並且在這種情況下p-n結不導電。所描述的簡單p-n結被稱為二極體(diode),它只在一個方向傳導電流,即當它處於正向偏置時。

二極體(diode)是一種典型地由單個p-n結制成的電子器件,其僅在一個方向上傳導電流。

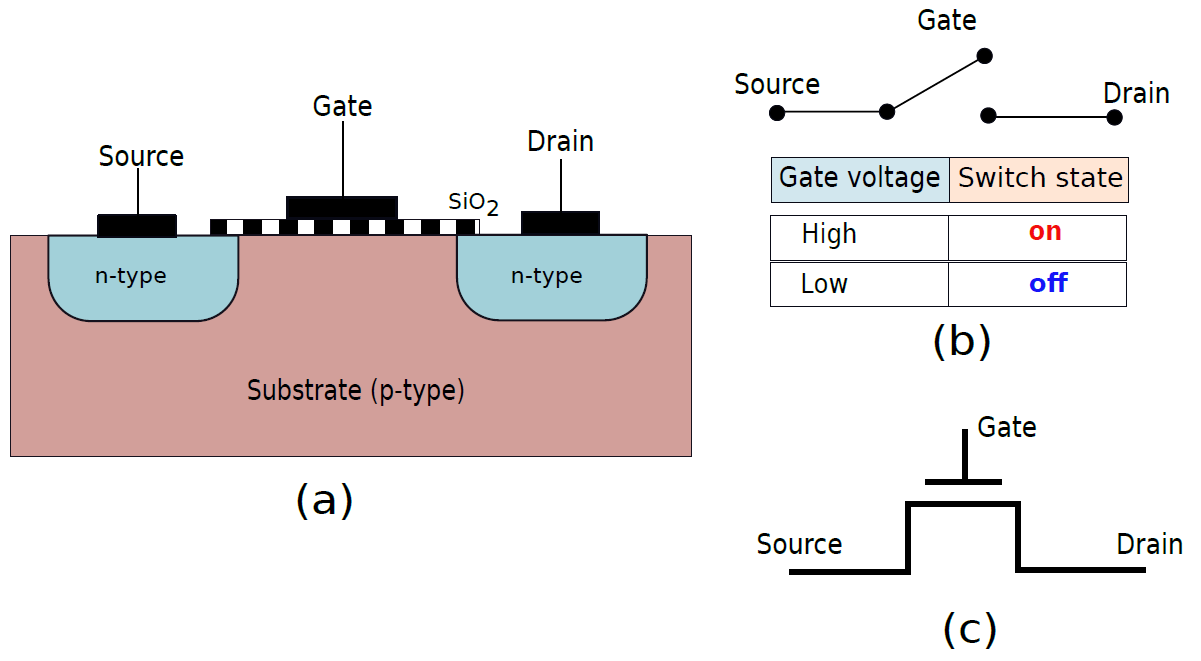

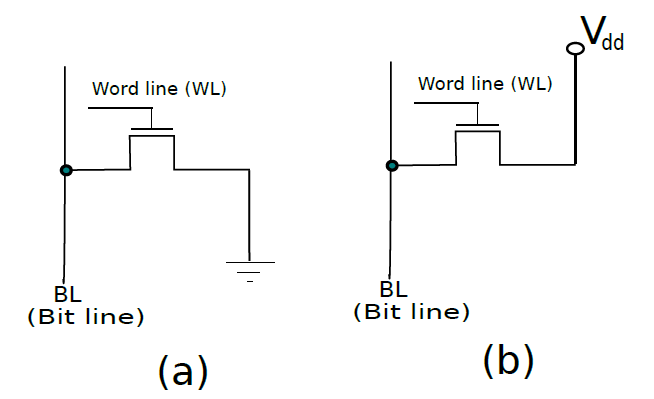

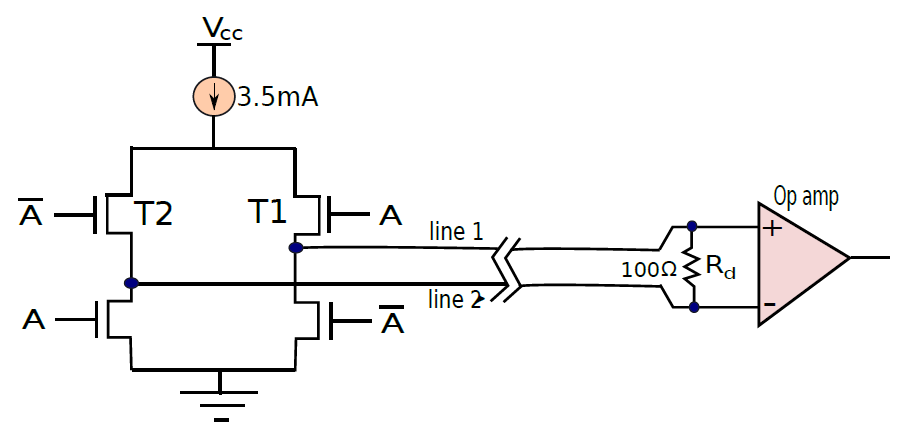

19.2.3.3 NMOS電晶體

現在,讓我們將兩個p-n結相互連線,如下圖(a)所示,這種結構被稱為NMOS(負金氧半導體)電晶體。在這張圖中,有一個p型摻雜矽的中心襯底。兩側有兩個小區域含有n型摻雜矽,這些區域分別被稱為漏極和源極。注意,由於結構是完全對稱的,這兩個區域中的任何一個都可以被指定為源極或漏極,源極和漏極中間的區域稱為通道。在溝道的頂部有一個通常由二氧化矽(SiO2)製成的薄絕緣層,它由金屬或多晶矽基導電層覆蓋,就是所謂的門(gate)。

因此,典型的NMOS電晶體有三個端子:源極、漏極和柵極,它們中的每一個都可以連線到電壓源。我們現在有兩個柵極電壓選項——邏輯1(\(V_{dd}\)伏)或邏輯0(0伏)。如果柵極處的電壓為邏輯1(Vdd伏),則溝道中的電子被吸引到柵極。事實上,如果柵極處的電壓大於某個閾值電壓(在當前技術中通常為0.15V),則由於電子的積累,在漏極和源極之間形成低電阻導電路徑。因此,電流可以在漏極和源極之間流動。如果溝道的有效電阻是R溝道,那麼我們有\(V_{drain}=IR_{channel}+V_{source}\)。如果流經電晶體的電流量低,則由於低溝道電阻(R溝道),\(V_{drain}\)大致等於\(V_{source}\)。因此,我們可以將NMOS電晶體視為開關(見上圖b)。當柵極電壓為1時,它被開啟。

現在,如果我們將柵極電壓設定為0,那麼由電子組成的導電路徑就無法在溝道中形成。因此,電晶體將不能傳導電流,將處於o狀態。在這種情況下,開關關閉。

NMOS電晶體的電路符號如上圖(c)所示。

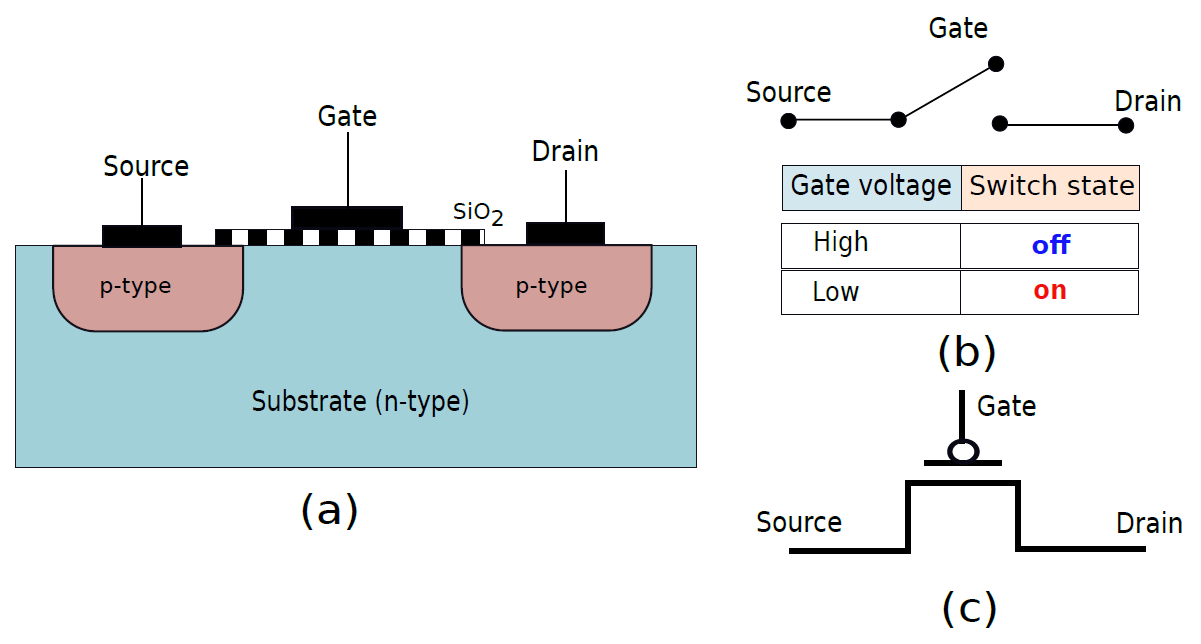

19.2.3.4 PMOS電晶體

像NMOS電晶體一樣,我們可以有一個PMOS電晶體,如下圖(a)所示,源極和漏極是由p型矽構成的區域,電晶體操作的邏輯與NMOS電晶體的邏輯完全相反。在這種情況下,如果柵極處於邏輯0,則空穴被吸引到溝道並形成導電路徑。然而,如果柵極處於邏輯1,則孔被溝道排斥,不形成導電路徑。

PMOS電晶體也可以被視為開關(圖b),當柵極電壓為0時,它開啟,當柵極處的電壓為邏輯1時,它關閉。PMOS電晶體的電路符號如圖(c)所示。

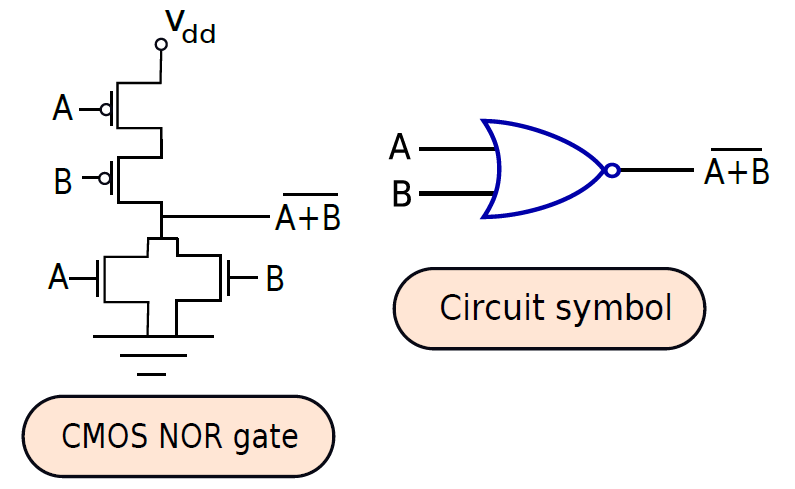

19.2.3.5 NAND和NOR門

下圖顯示瞭如何在CMOS技術中構建NAND門。兩個輸入端A和B連線到每個NMOS-PMOS對的柵極,如果A和B都等於1,則PMOS電晶體將關斷,NMOS電晶體將導通,將輸出設定為邏輯0。但是,如果其中一個輸入等於0,則其中一個NMOS電晶體將關閉,其中一個PMOS電晶體將開啟。因此,輸出將設定為邏輯1。

請注意,我們使用AND運算的運運算元「.」,這種符號在表示布林公式時被廣泛使用。同樣,對於OR運算,使用「+」符號。

下圖顯示瞭如何構建NOR門。在這種情況下,兩個輸入端A和B也連線到每個NMOS-PMOS對的柵極。然而,與NAND門相比,拓撲結構有所不同。如果其中一個輸入為邏輯1,則其中一個NMOS電晶體將導通,其中一個PMOS電晶體將截止,輸出將設定為0。如果兩個輸入都等於0,則兩個NMOS晶體將截止,兩個PMOS晶體將導通,輸出將等於邏輯1。

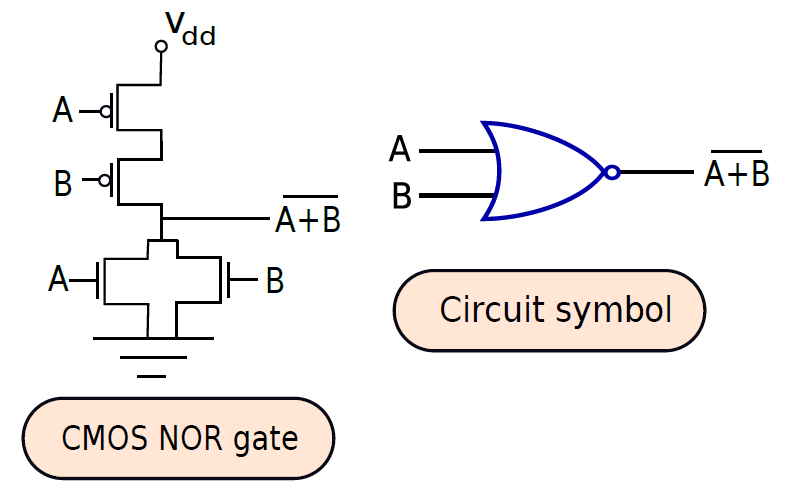

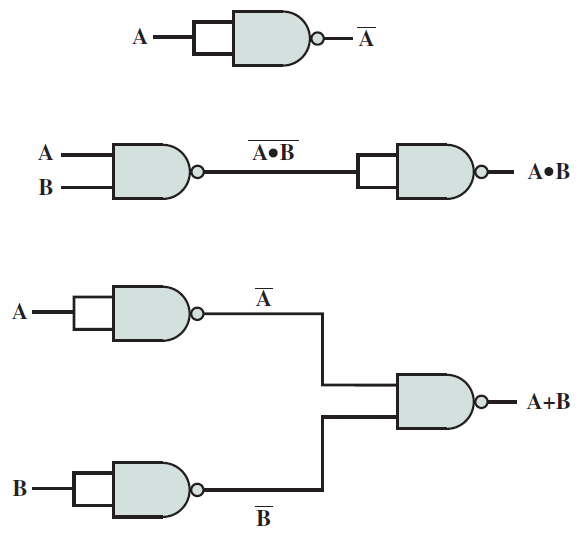

NAND門的一些用途如下:

NOR門的一些用途如下:

19.2.4 組合邏輯電路

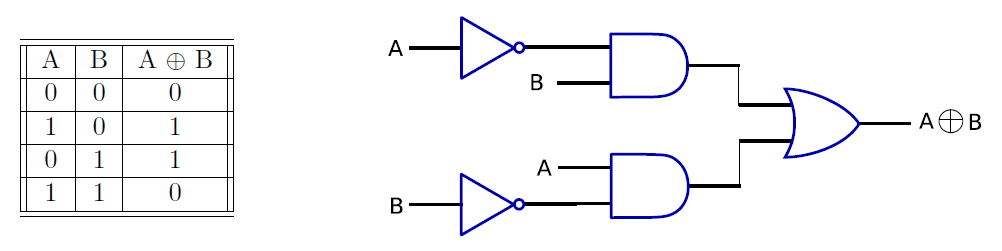

19.2.4.1 XOR門

讓我們實現互斥或(XOR)的邏輯函數,使用運運算元進行XOR運算,如果兩個輸入不相等,則互斥或操作返回1,否則返回0。已知\(A \oplus B=A \cdot \overline{B}+\overline{A} \cdot B\),則真值表和實現互斥或門的電路如下所示。

基本邏輯閘如下所示:

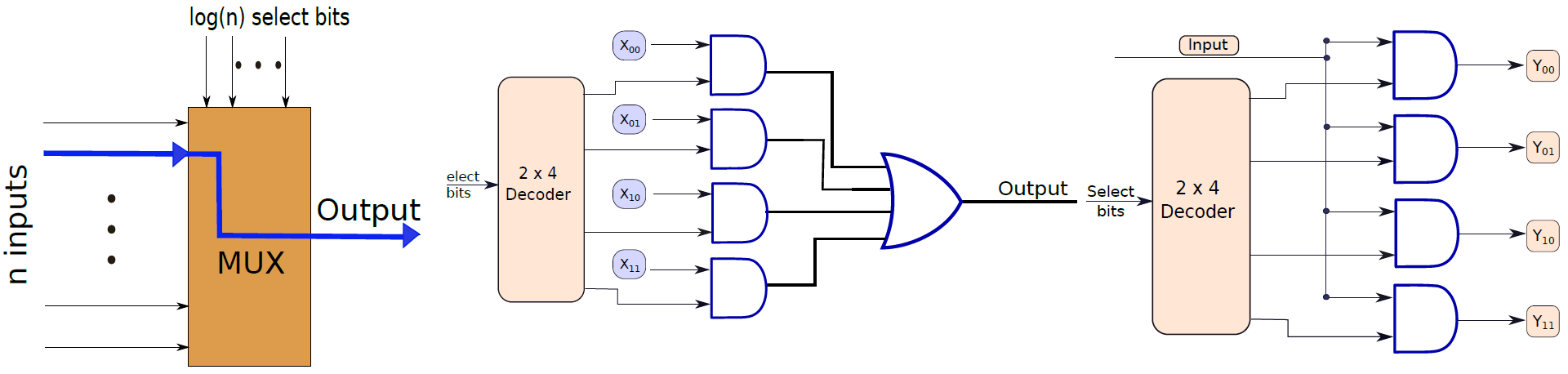

19.2.4.2 多路複用器和訊號分離器

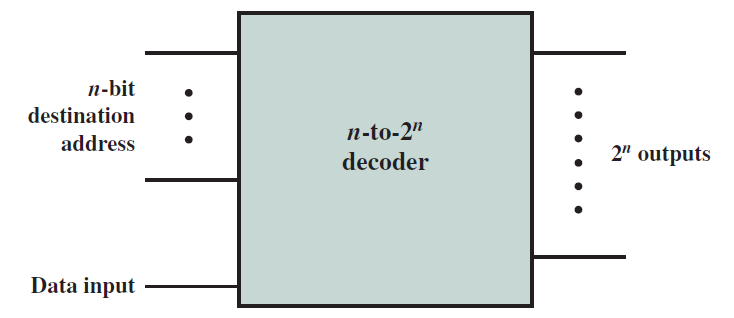

多路複用器(Multiplexer)的框圖如下圖左所示,採用n個輸入位和log(n)個選擇位,並根據選擇位的值,選擇一個輸入作為輸出(參見圖中帶箭頭的線)。多路複用器在處理器設計中大量使用,我們需要從一組輸入中選擇一個輸出。多路複用器也稱為多路複用器。

訊號分離器將log(n)位二進位制數作為輸入,1位輸入,並將輸入傳輸到n條輸出線中的一條,參見下圖右。多路分解器用於儲存單元的設計,其中輸入必須精確地反映在一條輸出線中。

左:單個多路複用器結構圖。中:4輸入的多路複用器。右:訊號分離器。

多路複用器輸入至程式計數器。

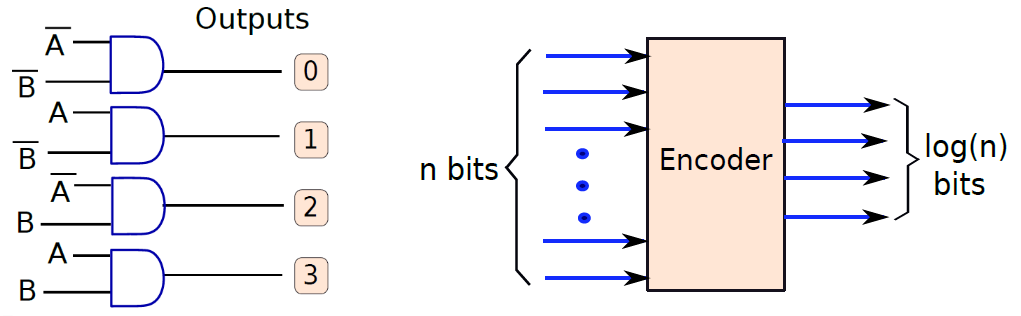

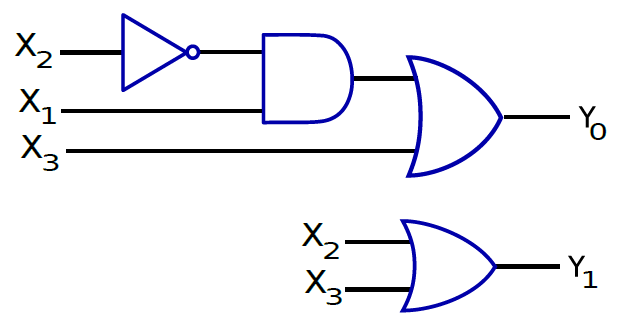

19.2.4.3 編碼器和解碼器

解碼器將log(n)位二進位制數作為輸入,並具有n個輸出。根據輸入,它將其中一個輸出設定為1。

解碼器的設計如下圖左所示,具有兩個輸入和四個輸出的2x4解碼器的設計。假設輸入是A和B。我們生成所有可能的組合:\(\overline{A B}, \overline{A} B, A \overline{B}, AB\)。這些布林組合是通過計算A和B的邏輯「非」,然後將這些值路由到一組「與」門來生成的。

現在讓我們考慮一個與解碼器邏輯相反的電路,其框圖如下圖右所示。該電路有n個輸入和log(n)個輸出,n個輸入中的一個假定為1,其餘假定為0,輸出位提供等於1的輸入二進位制編碼。例如,在8輸入、3輸出編碼器中,如果第f行等於1,則輸出等於100(計數從0開始)。

左:2x4解碼器的設計。右:n位編碼器框圖。

現在我們假設我們不存在只有一個輸入行可以等於1的限制,假設有多個輸入可以等於1。在這種情況下,我們需要報告具有最高索引(優先順序)的輸入行的二進位制編碼。例如,如果是第3行和第5行,那麼我們需要報告第5行的二進位制編碼,和上圖右一樣。此外,4-2位編碼器的電路圖如下圖所示。

用解碼器實現解複用器:

時鐘SR鎖存器(下圖左)和D鎖存器(下圖右):

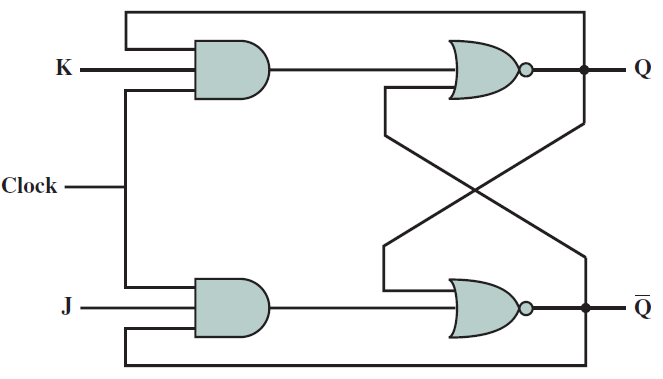

J–K鎖存器:

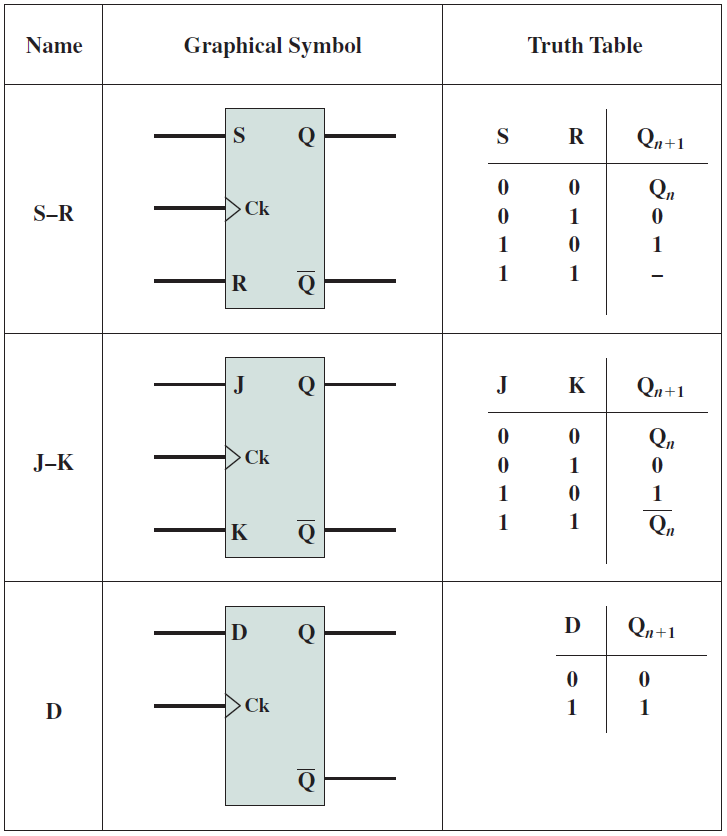

基本鎖存器的比較:

19.2.5 時序邏輯電路

前面已經研究了在位元上計算不同函數的組合邏輯電路,本小節將討論如何儲存位以供以後使用,這些結構被稱為順序邏輯元件(sequential logic element),因為輸出取決於過去的輸入,這些輸入在事件序列中較早出現。邏輯閘的基本思想是修改輸入值以獲得所需的輸出,在組合邏輯電路中,如果輸入被設定為0,那麼輸出也被重置。為了確保電路儲存一個值並在處理器通電時保持該值,需要設計一種具有某種「內建記憶體」的不同型別的電路。讓我們從制定一組要求開始:

1、電路應能自我維持,並在外部輸入復位後保持其值。不應依賴外部訊號來維持其儲存的元件。

2、應該有一種方法來讀取儲存的值而不破壞它。

3、應該有一種方法將儲存值設定為0或1。

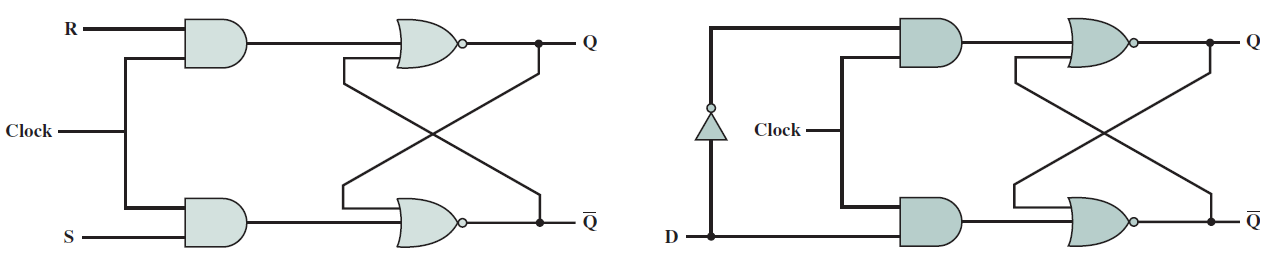

確保電路保持其值的最佳方法是建立反饋路徑,並將輸出連線回輸入,先看看最簡單的邏輯電路:SR鎖存器(SR latch)。

19.2.5.1 SR鎖存器

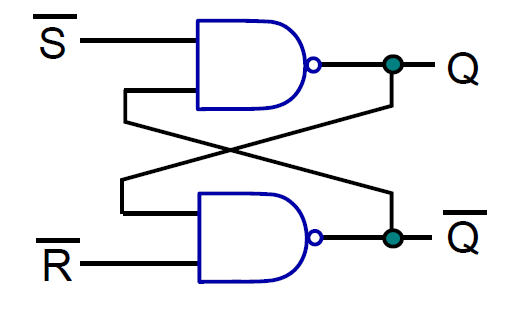

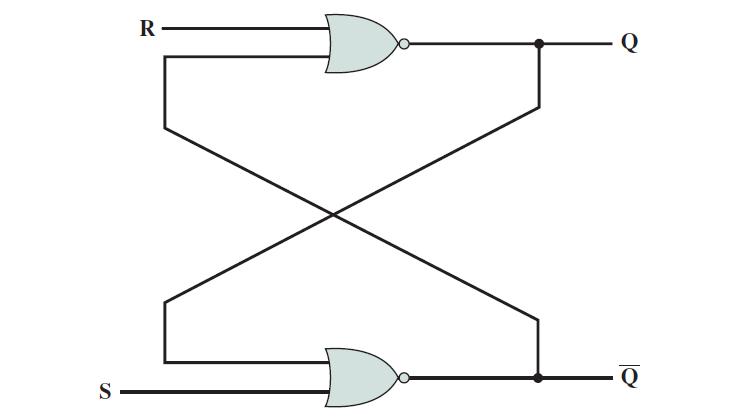

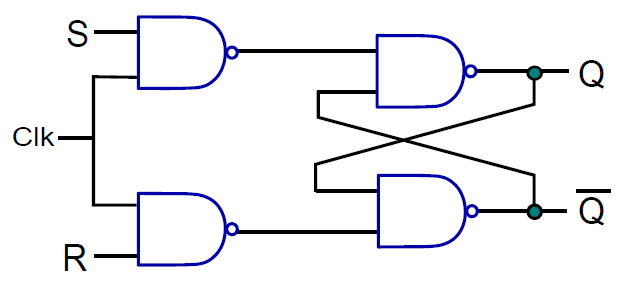

下圖顯示了SR鎖存器。有兩個輸入S(設定)和R(重置),有兩個輸出Q及其二補數Q,包含了兩個交叉耦合NAND門的電路。請注意,如果與非門的一個輸入為0,則輸出保證為1。然而,如果其中一個輸入是1,另一個輸入則為a,則輸出為a。

用NOR門實現的SR鎖存器:

19.2.5.2 時鐘和訊號

一個典型的處理器包含數百萬或可能數十億個邏輯閘和數千個鎖存器,不同的電路需要不同的時間,例如多路複用器可能需要1ns,解碼器可能需要0.5ns。電路完成計算後,就可以轉發輸出了。如果沒有全域性時間的概念,很難在不同的單元之間同步通訊,尤其是那些具有可變延遲的單元,導致難以設計、操作和驗證處理器。由此需要時間概念,例如可以說加法器需要兩個時間單位,在兩個單元結束時,預期資料將在鎖存器X中找到,其他單元可以在兩個時間單元后從鎖存器中獲取值並繼續計算。

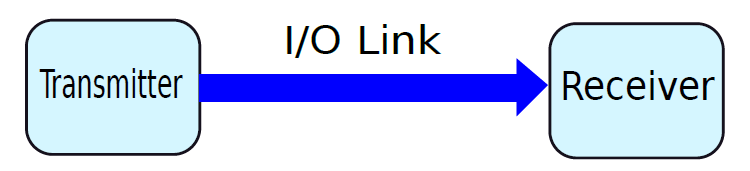

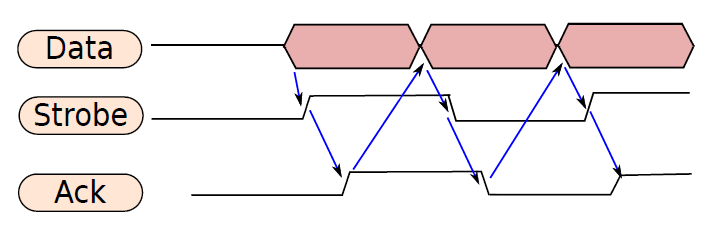

考慮一個需要向印表機傳送一些資料的處理器的例子。為了傳輸資料,處理器通過一組銅線傳送一系列位元,印表機讀取這些位元,然後列印資料。問題是,處理器什麼時候傳送資料?計算完成後,需要傳送資料。我們可以問的下一個問題是,處理器如何知道計算何時結束?它需要知道不同單元的確切延遲,一旦計算的總持續時間過去,可以將輸出資料寫入鎖存器,並設定用於通訊的銅線的電壓。因此,處理器確實需要時間概念。其次,設計者需要告訴處理器不同子單元所需的時間。與處理2.34ns和1.92ns等數位相比,處理1、2和3等整數要簡單得多。這裡的1、2、3表示時間單位,時間單位可以是任何數位,例如0.9333ns。

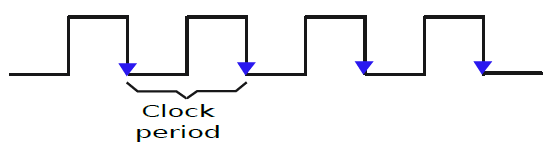

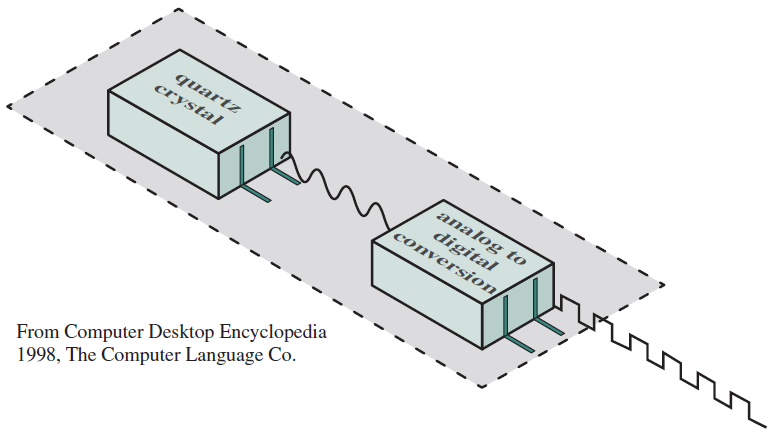

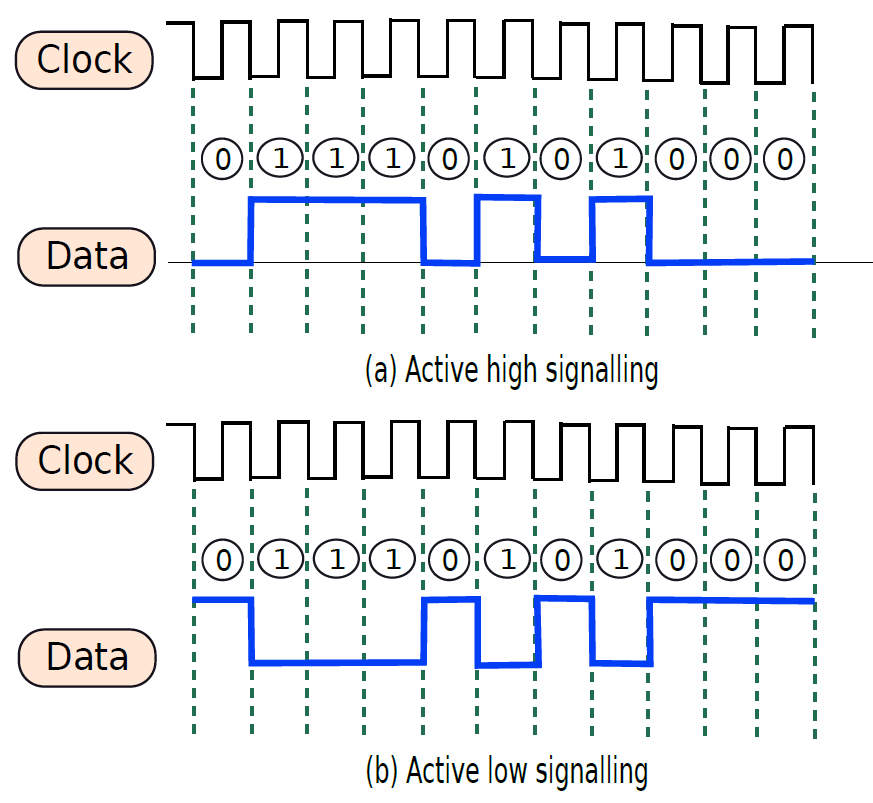

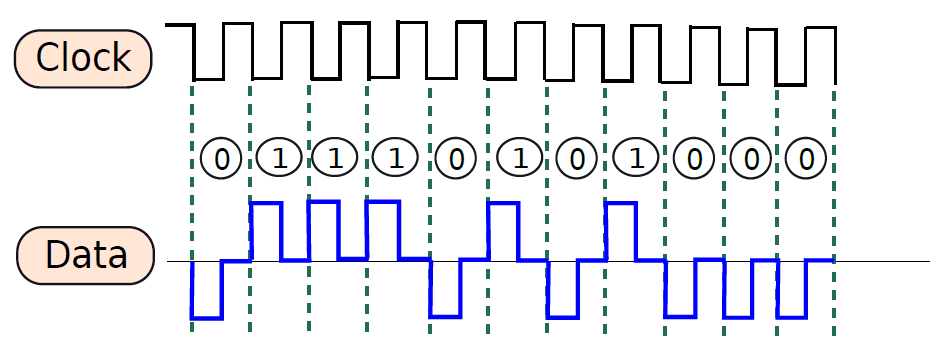

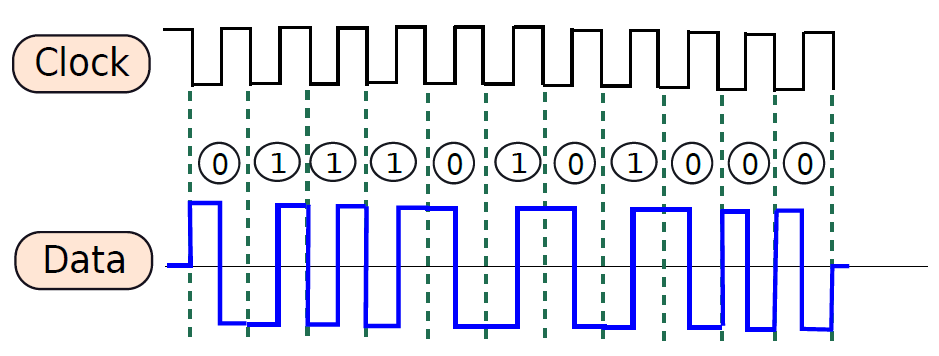

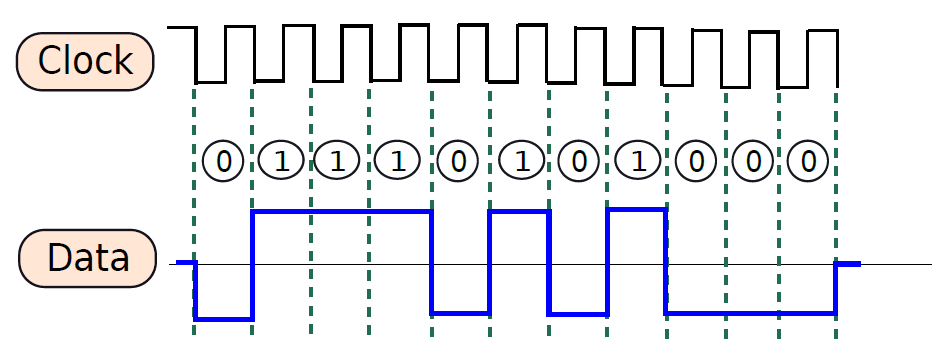

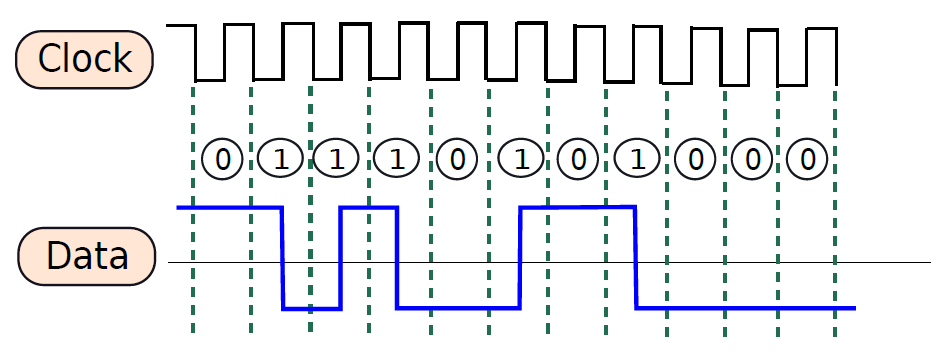

時鐘訊號(clock signal):傳送到大型電路或處理器的每個部分的週期性方波。

時鐘週期(clock cycle):時鐘訊號的週期。

時脈頻率(clock frequency):時鐘週期的倒數。

因此,大多數數位電路與時鐘訊號同步,該時鐘訊號在完全相同的時間向處理器的每個部分傳送週期性脈衝。時鐘訊號為方波,如下圖所示,大多數時間,時鐘訊號是由主機板上的專用單元從外部生成的。讓我們考慮時鐘訊號從1轉變到0(向下/負邊緣)的點作為時鐘週期的開始,從時鐘的一個向下沿到下一個向下邊緣測量時鐘週期,時鐘週期的持續時間也稱為時鐘週期,時鐘週期的倒數被稱為時脈頻率。

一個時鐘訊號。

電腦、筆記型電腦、平板電腦或行動電話通常會在其規格中列出頻率。例如,規範可能會說處理器執行在3GHz,這個數位是指時脈頻率。

典型的計算模型是:電路中執行所有基本動作所需的時間是按照時鐘週期來測量的,如果生產者單元佔用n個時鐘週期,那麼在n個時鐘迴圈結束時,它將其值寫入鎖存器。其他使用者單元知道此延遲,並且在第(n+1)個時鐘週期開始時,它們從鎖存器讀取值。由於所有單元都與時鐘明確同步,並且處理器知道每個單元的延遲,因此很容易對計算進行排序、與I/O裝置通訊、避免競爭條件、偵錯和驗證電路。我們想向印表機傳送資料的簡單範例可以通過使用時鐘輕鬆解決。

19.2.5.3 時鐘SR鎖存器

下圖顯示了SR鎖存器,其增加了兩個與非門,時鐘作為輸入之一,另外兩個輸入分別是S位和R位。如果時鐘為0,則交叉耦合NAND門的兩個輸入都為1,將保持先前的值。如果時鐘為1,則交叉耦合NAND門的輸入分別為S和R,這些輸入與基本SR鎖存器相同。請注意,時鐘鎖存器通常稱為觸發器(flip-flop)。

時鐘SR鎖存器圖例。

觸發器(flip-flop)是一個時鐘鎖存器,可以儲存一位(0或1)。

通過使用時鐘,我們部分解決了輸入和輸出同步的問題。在這種情況下,當時鍾為0時,輸出不受輸入的影響。當時鍾為1時,輸出受輸入影響。這種鎖存器也稱為電平敏感鎖存器(level sensitive latch)。

電平敏感鎖存器(level sensitive latch)取決於時鐘訊號的值:0或1。通常,它只能在時鐘為1時讀取新值。

在電平敏感鎖存器中,電路有半個時鐘週期來計算正確的輸出(當時鍾為0時)。當時鍾為1時,輸出可見。最好有一個完整的時鐘週期來計算輸出,這需要一個邊緣敏感鎖存器(edge sensitive latch),邊緣敏感鎖存器僅在時鐘的向下邊緣反映輸出端的輸入。

邊緣敏感鎖存器(edge sensitive latch)僅在固定的時鐘邊緣(例如向下邊緣,從1到0的轉換)反映輸出端的輸入。

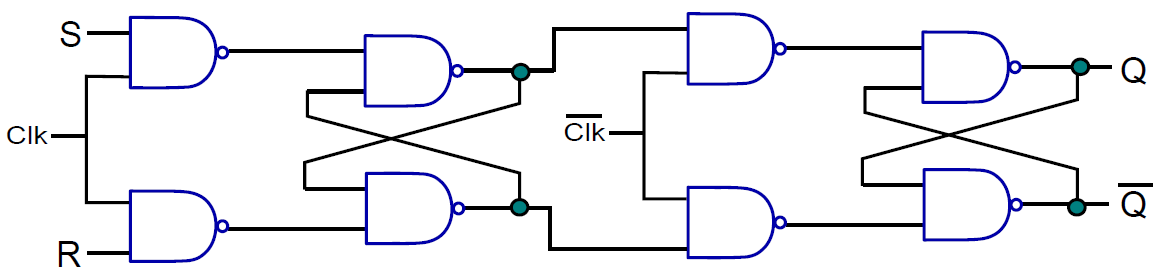

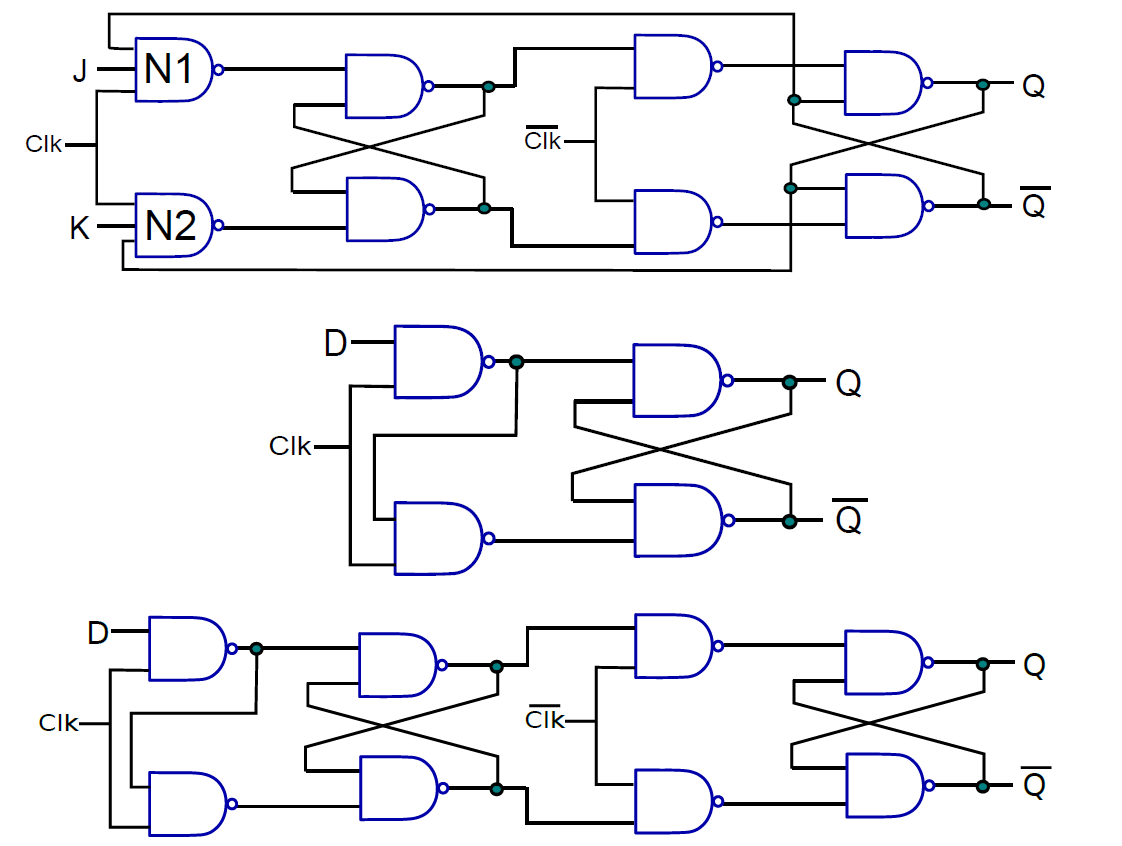

19.2.5.4 邊緣敏感SR觸發器

下圖顯示了邊緣敏感SR觸發器的結構圖,連線了兩個邊緣敏感SR觸發器,唯一的區別是第二個觸發器使用了時鐘訊號組合。第一個觸發器為主(master),而第二個為從(slave)。這種觸發器也被稱為主-從SR觸發器。這就是這個電路的工作原理。

除了主從SR觸發器,還有其它各種型別的觸發器,如JK觸發器、D觸發器、主從D觸發器等。

從上到下:JK觸發器、D觸發器、主從D觸發器。

19.2.5.5 暫存器

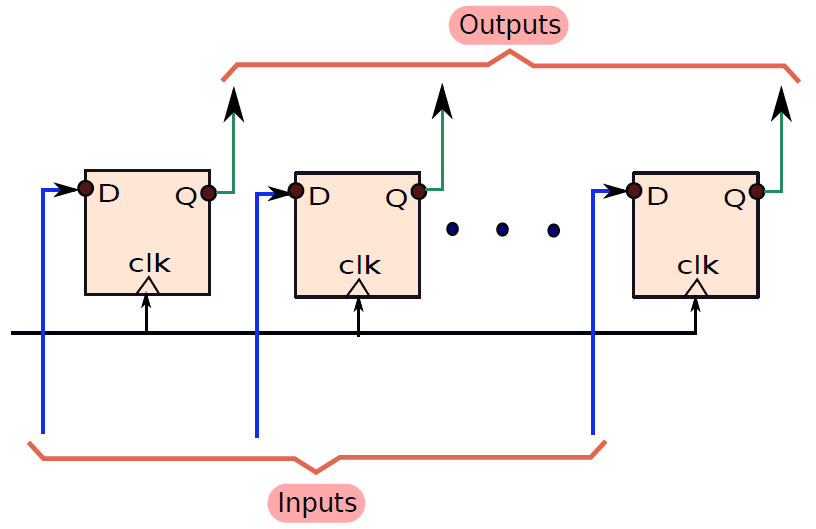

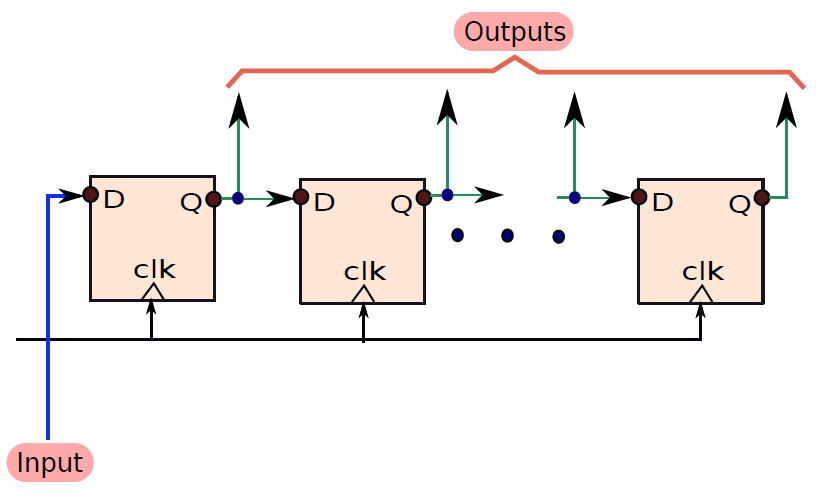

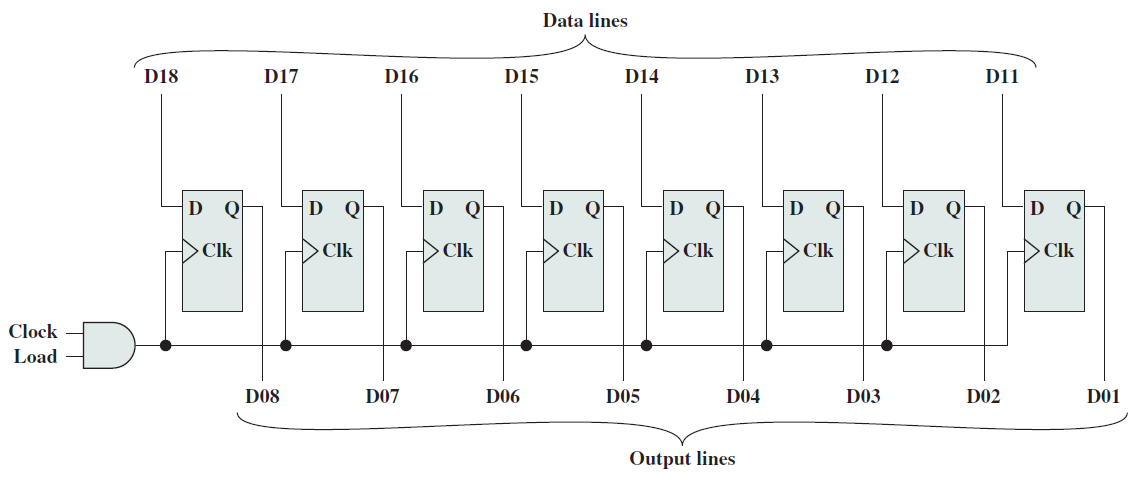

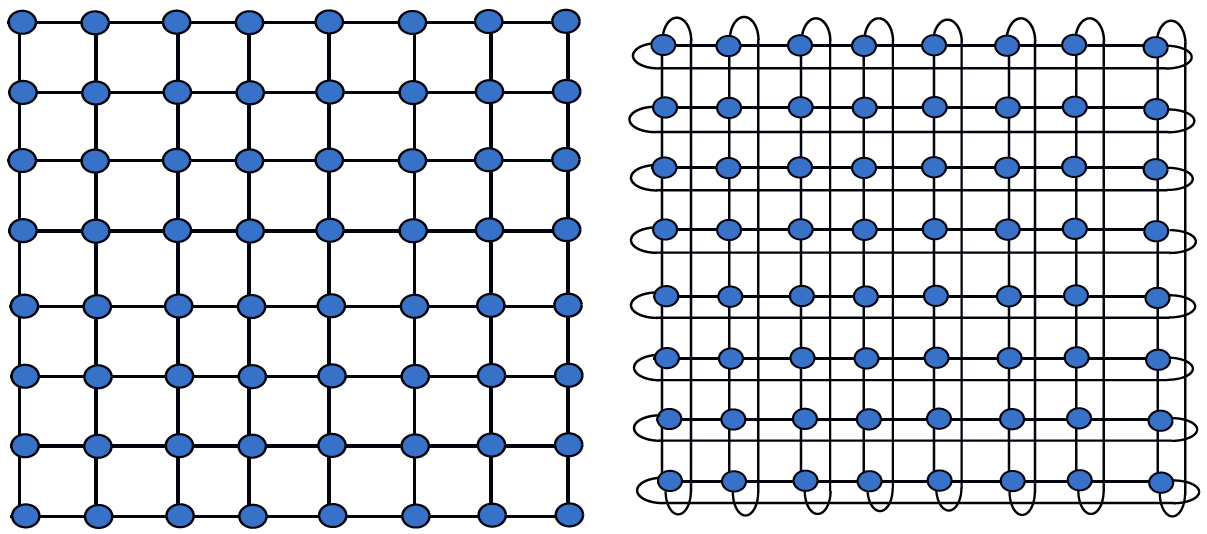

我們可以通過使用一組n個主從D觸發器來儲存n位資料,每個D觸發器連線到輸入線,其輸出端連線到輸出線,這種n位結構被稱為n位暫存器。我們可以並行載入n位,也可以在每個負時鐘邊沿並行讀取n位。因此,這種結構被稱為並行輸入——並行輸出暫存器。其結構如下圖所示。

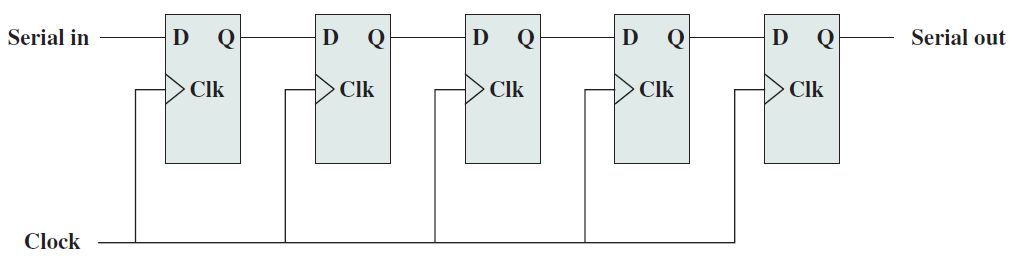

現在讓我們考慮一個序列輸入-並行輸出暫存器,如下圖所示,有一個輸入被饋送到最左邊的D觸發器, 每個週期,輸入都會移動到右側的相鄰觸發器。因此,要載入n位將需要n個週期。 第一位將在第一個週期被載入到最左邊的觸發器中,它需要n個週期才能到達最後一個觸發器。 到那時,其餘的n - 1觸發器將載入其餘的n - 1位,然後我們可以並行讀取所有 n 位(類似於並行並行輸出暫存器)。 該暫存器也稱為移位暫存器,用於實現高速I/O匯流排中使用的電路。

8位元並行暫存器的結構圖如下:

5位移位暫存器:

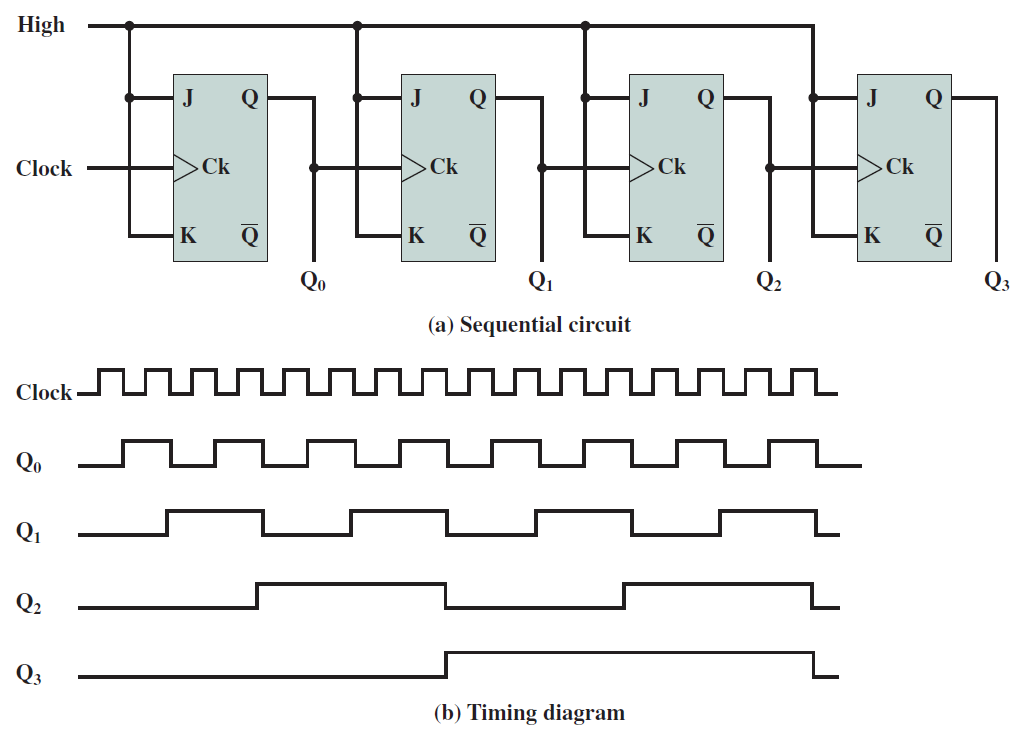

行波計數器:

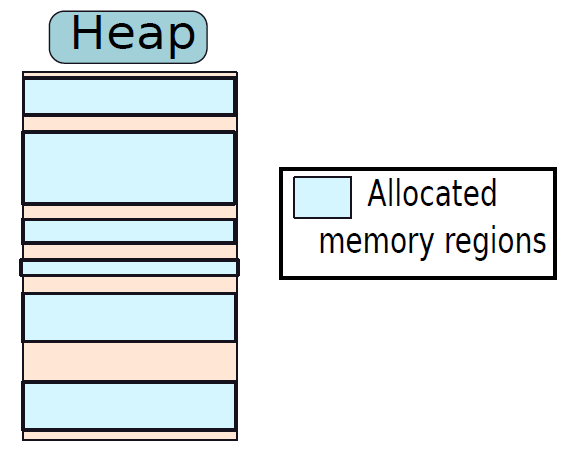

19.2.6 記憶體

19.2.6.1 靜態記憶體(SRAM)

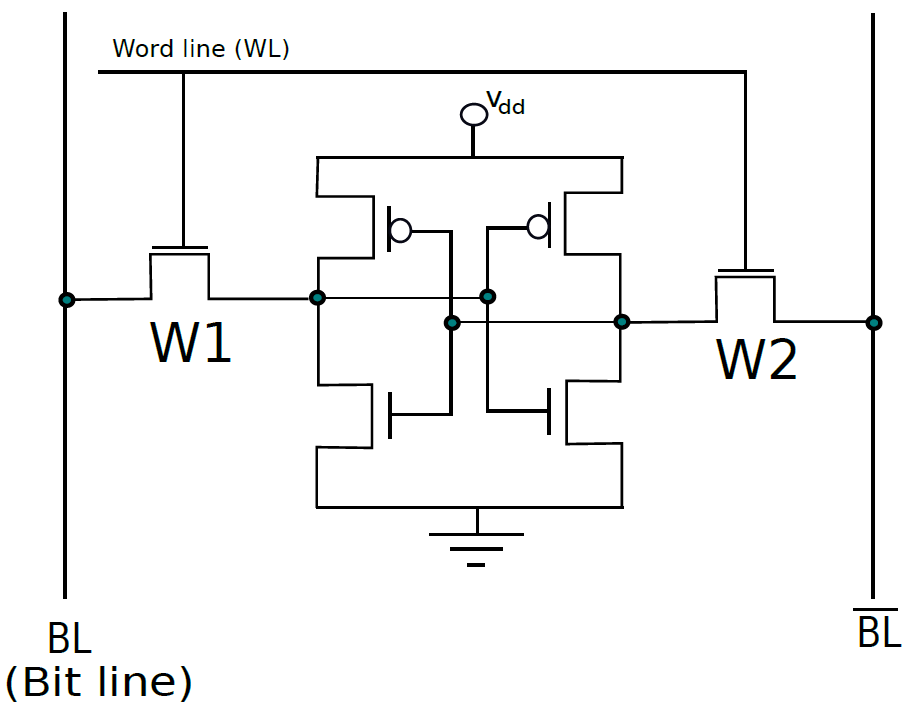

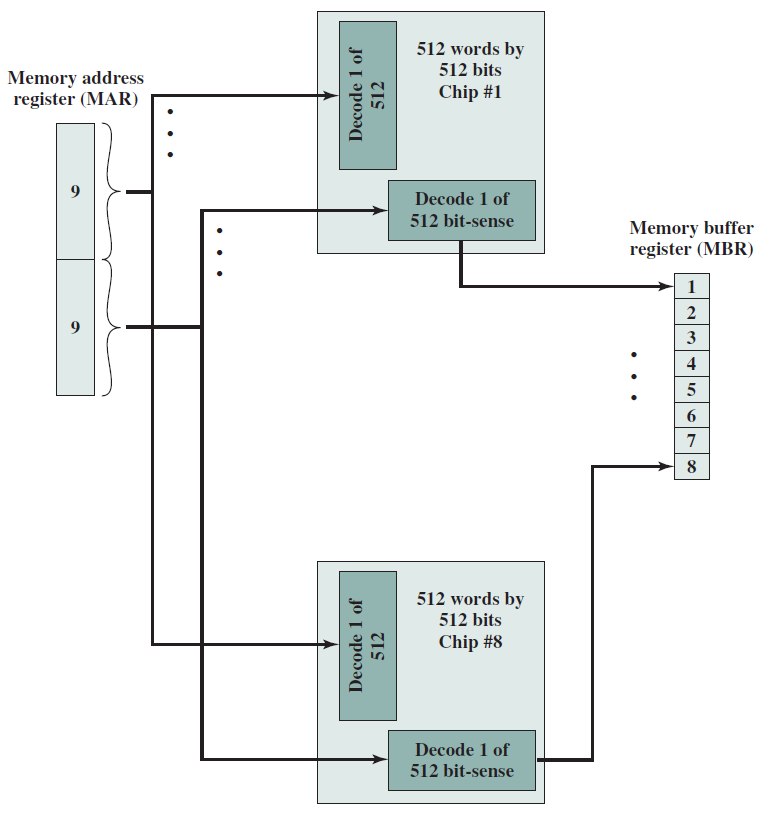

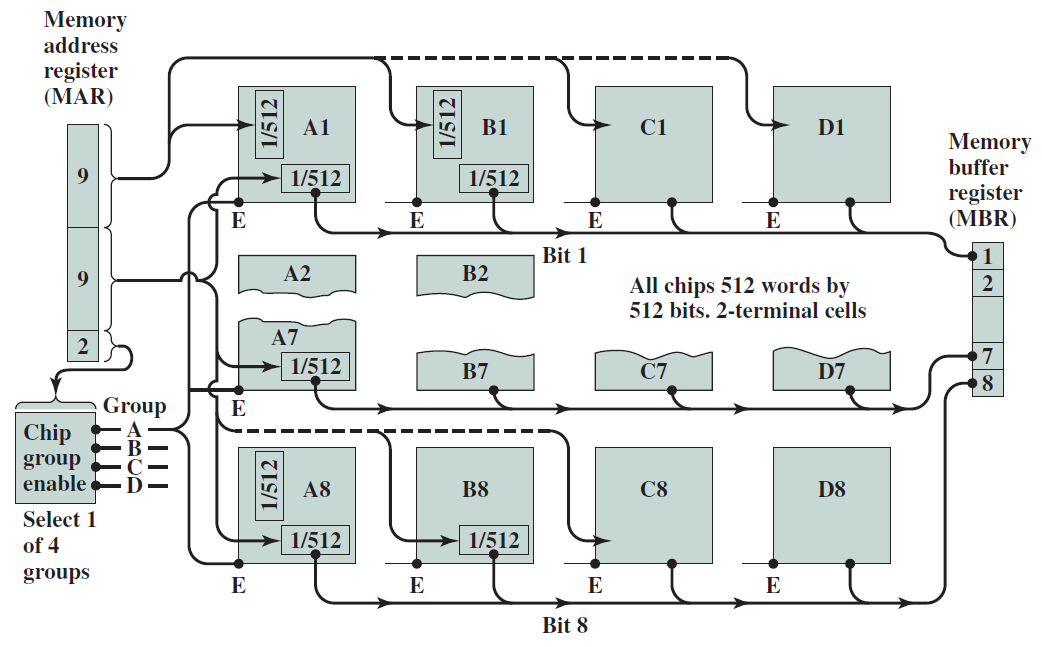

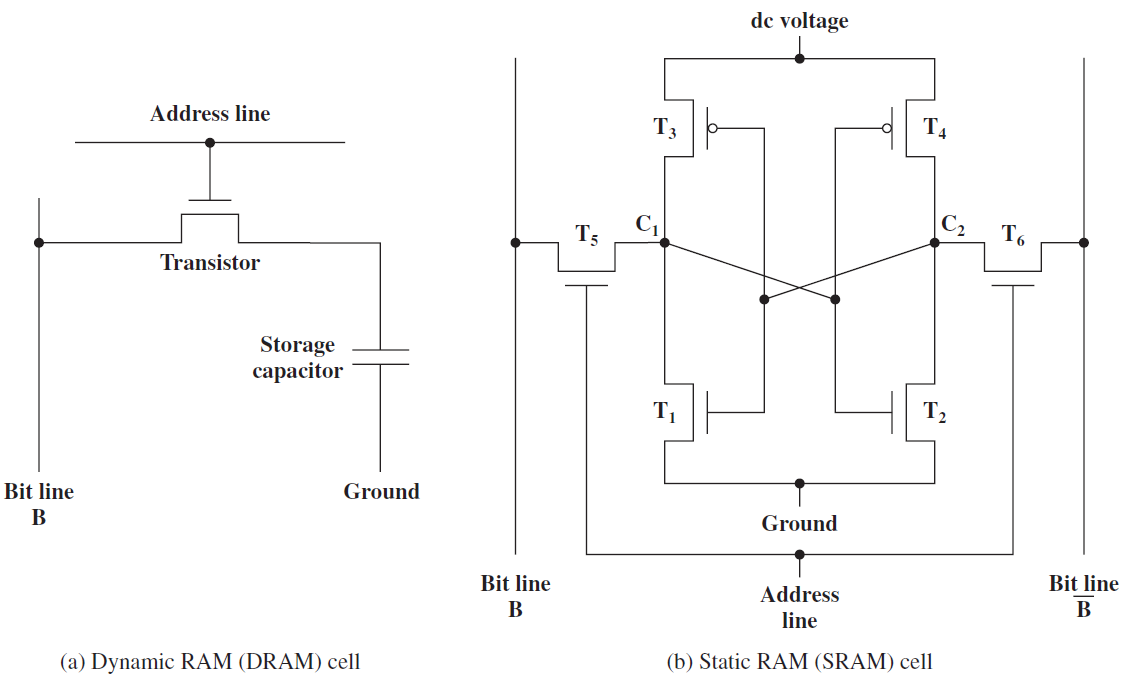

SRAM是指靜態隨機存取記憶體,基本SRAM單元包含兩個交叉耦合的反相器,如下圖所示。相比之下,基本SR觸發器或D觸發器包含交叉耦合的NAND門。設計如下所示。

SRAM單元的核心包含4個電晶體(每個反相器中有2個),這種交叉耦合佈置足以節省單個位元(0或1)。然而,我們需要一些額外的電路來讀取和寫入值。此時,在鎖存器中使用交叉耦合反相器到底是不是一個壞主意,它們畢竟需要更少的電晶體。我們將看到,實現用於讀取和寫入SRAM單元的電路的開銷是非常重要的,開銷不足以證明以SRAM單元為核心製作鎖存器的合理性。

交叉耦合的反相器連線到每一側(W1、W2)上的電晶體,W1和W2的柵極連線到被稱為字線的相同訊號,兩個反相器W1和W2中的四個電晶體構成SRAM單元,它總共有六個電晶體。現在,如果字線上的電壓低,則W1和W2關斷,不可能讀取或寫入SRAM單元。然而,如果字線上的訊號為高,則W1和W2導通,可以存取SRAM單元。

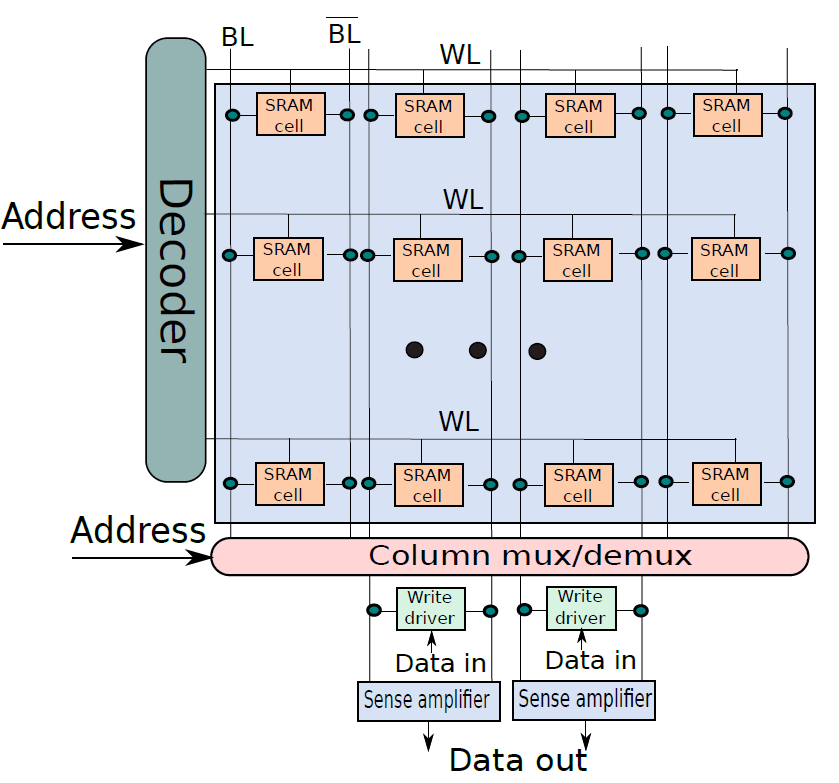

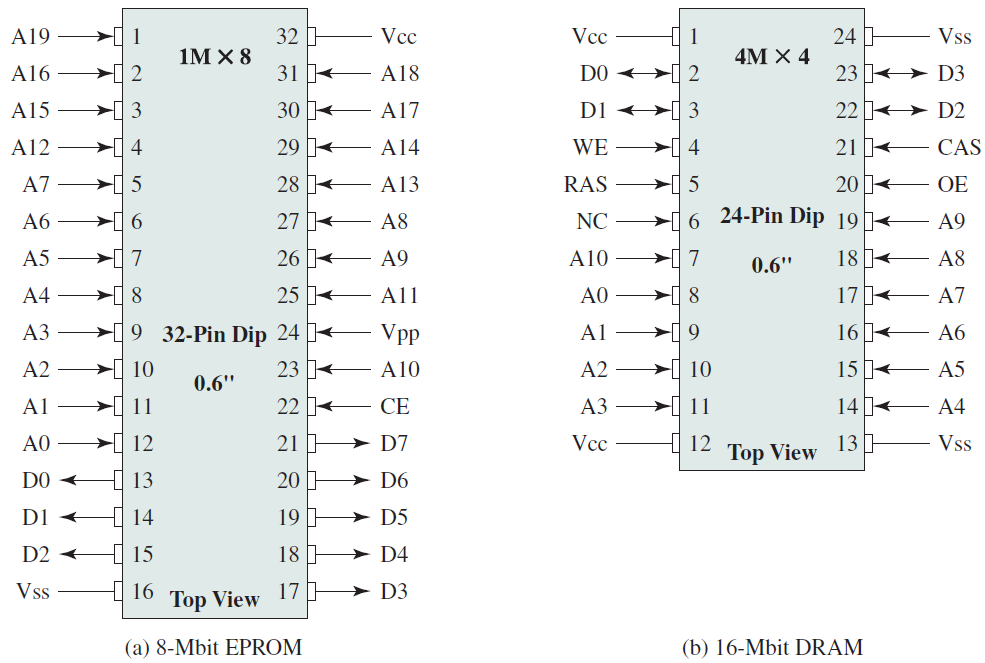

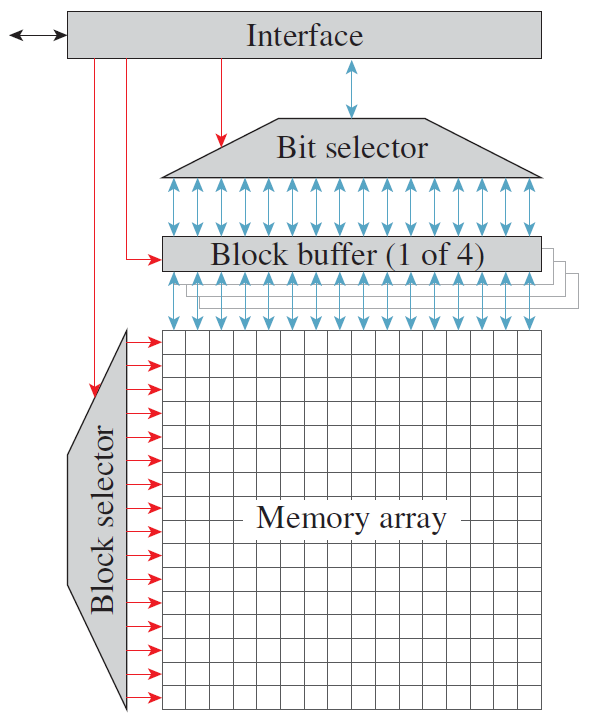

下圖顯示了一個典型的SRAM陣列,SRAM單元被佈置為二維矩陣。一行中的所有SRAM單元共用字線,一列中的所有SRAM單元共用一對位線。要啟用某個SRAM單元,必須開啟其相關的字線,由解碼器完成,獲取地址位的子集,並開啟適當的字線。一行SRAM單元可能包含100多個SRAM單元,通常,我們會對32個SRAM單元(在32位元機器上)的值感興趣。在這種情況下,列複用器/解複用器選擇屬於感興趣的SRAM單元的位線,使用地址中的位的子集作為列選擇位。這種設計方法也稱為2.5D記憶體組織。

SRAM單元陣列。

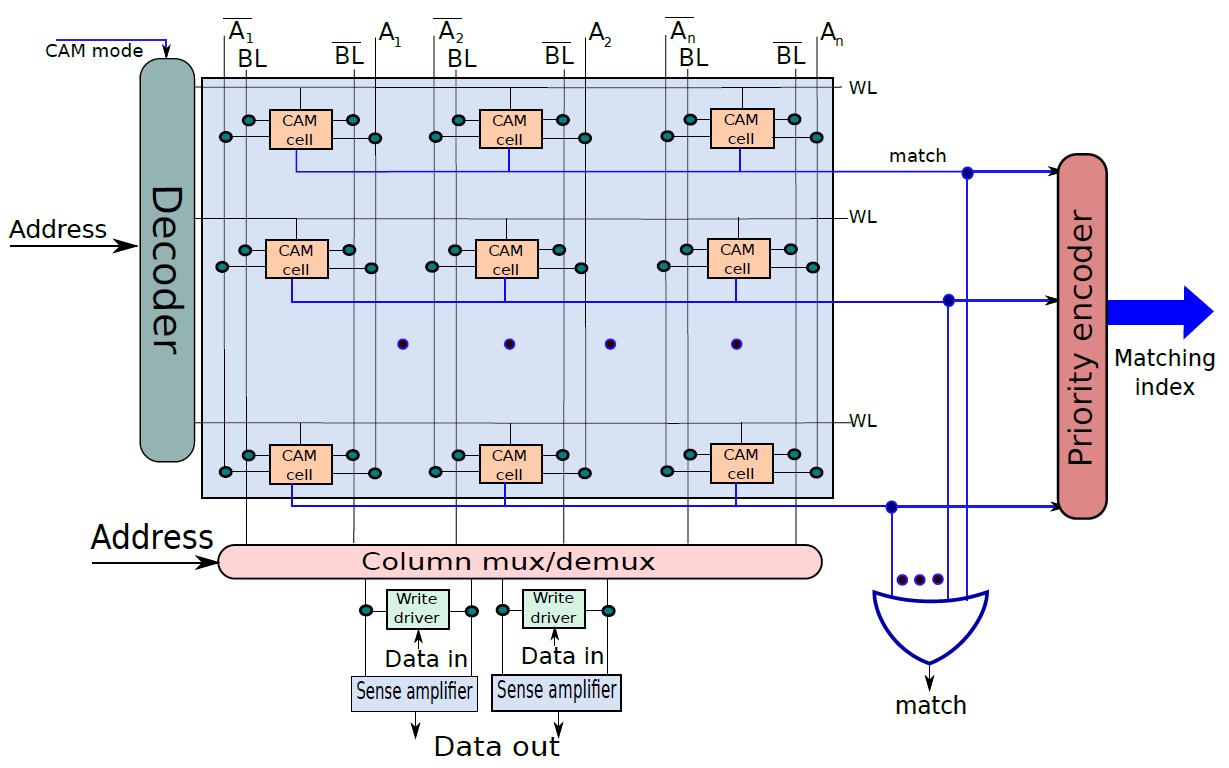

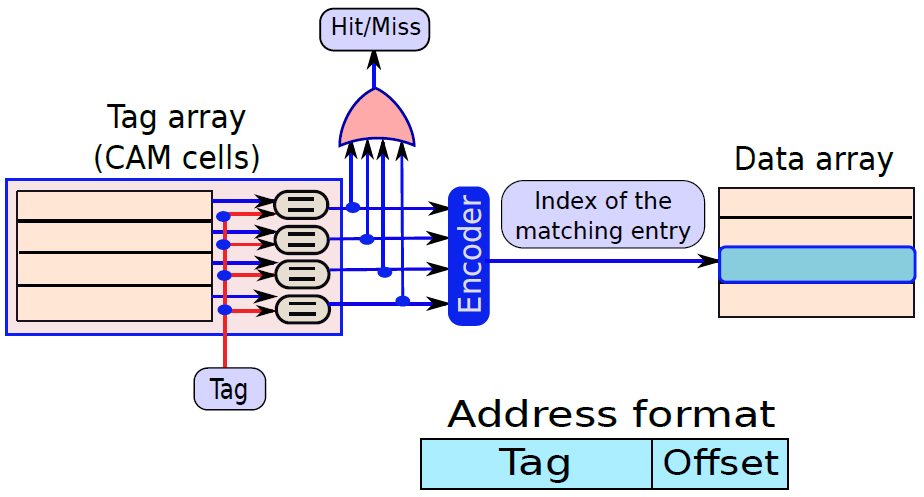

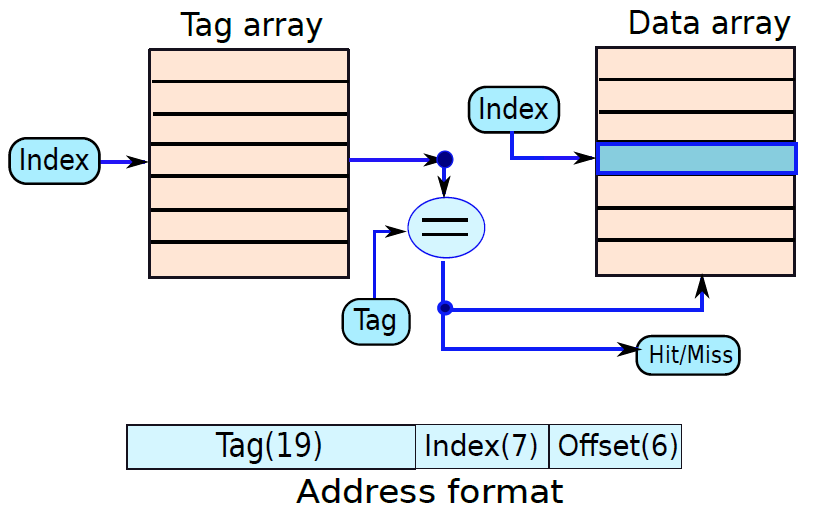

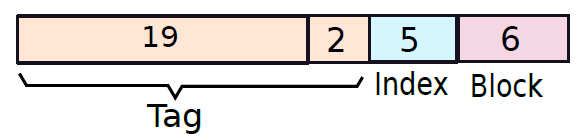

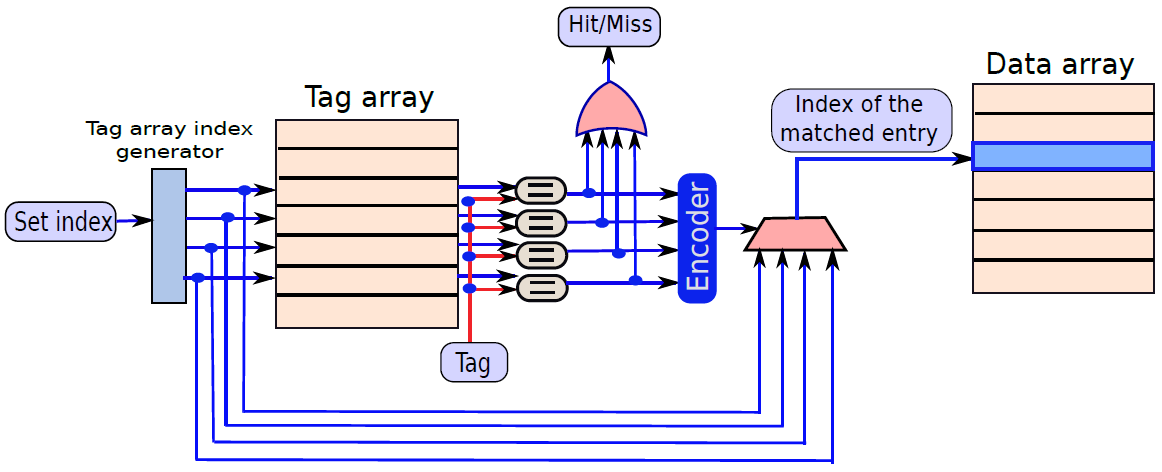

19.2.6.2 內容定址記憶體(CAM)

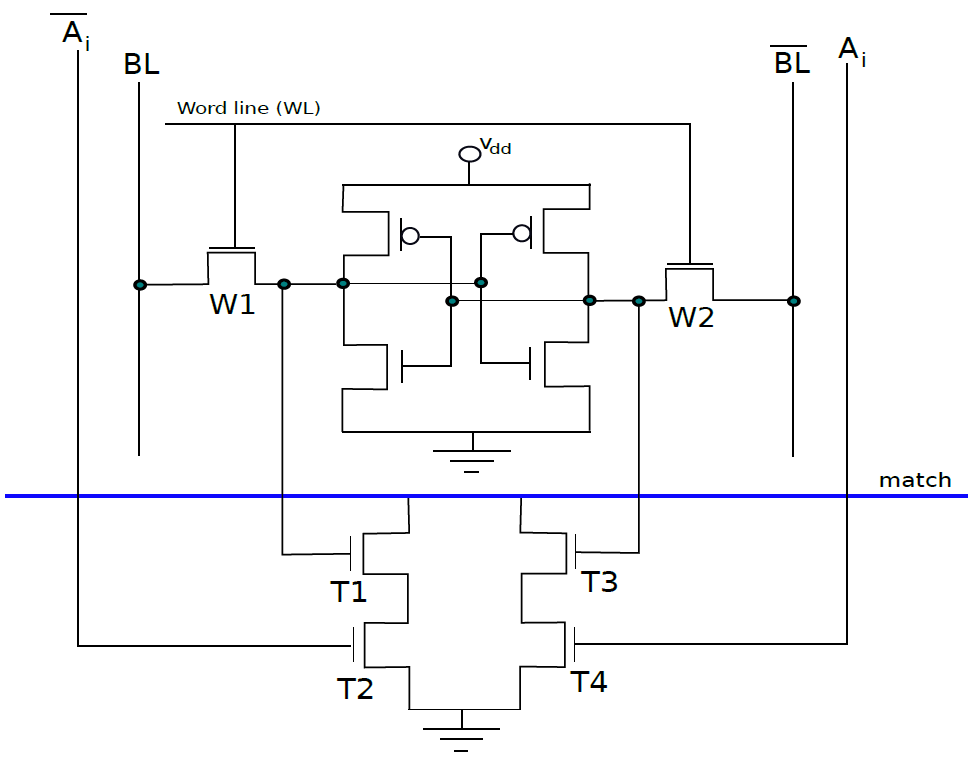

下圖是10電晶體CAM單元,如果SRAM單元中儲存的值V不等於輸入位\(A_i\),那麼我們希望將匹配線的值設定為0。在CAM單元中,上半部分是具有6個電晶體的常規SRAM單元,下半部有4個額外的電晶體。現在讓我們考慮電晶體T1,它連線到全域性匹配線,電晶體T2。T1由儲存在SRAM單元中的值V控制,T2由\(\overline{A_i}\)控制。假設V=\(\overline{A_i}\),如果兩者都為1,則電晶體T1和T2處於導通狀態,並且匹配線和地之間存在直接導電路徑。因此,匹配線的值將設定為0。然而,如果V和\(\overline{A_i}\)都為0,則通過T1和T2的路徑不導通。但是,在這種情況下,通過T3和T4的路徑變得導通,因為這些電晶體的柵極分別連線到\(\overline{V}\)和\(A_i\)。兩個柵極的輸入都是邏輯1,因此匹配線將被下拉到0。讀取器可以反過來驗證,如果V=\(A_i\),則不形成導通路徑。因此,如果儲存的值與輸入位\(A_i\)不匹配,則CAM單元將匹配線驅動到邏輯0。

10電晶體CAM單元。

下圖顯示了CAM單元陣列。該結構主要類似於SRAM陣列。我們可以通過索引定址一行,並執行讀/寫存取,此外可以將CAM單元的每一行與輸入A進行比較。如果任何行與輸入匹配,則相應的匹配線的值將為1。可以計算所有匹配線的邏輯OR,並確定CAM陣列中是否匹配,此外可以將CAM陣列的所有匹配線連線到優先順序編碼器,以查詢與資料匹配的行的索引。

CAM單元陣列。

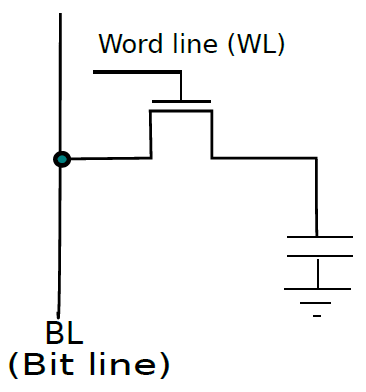

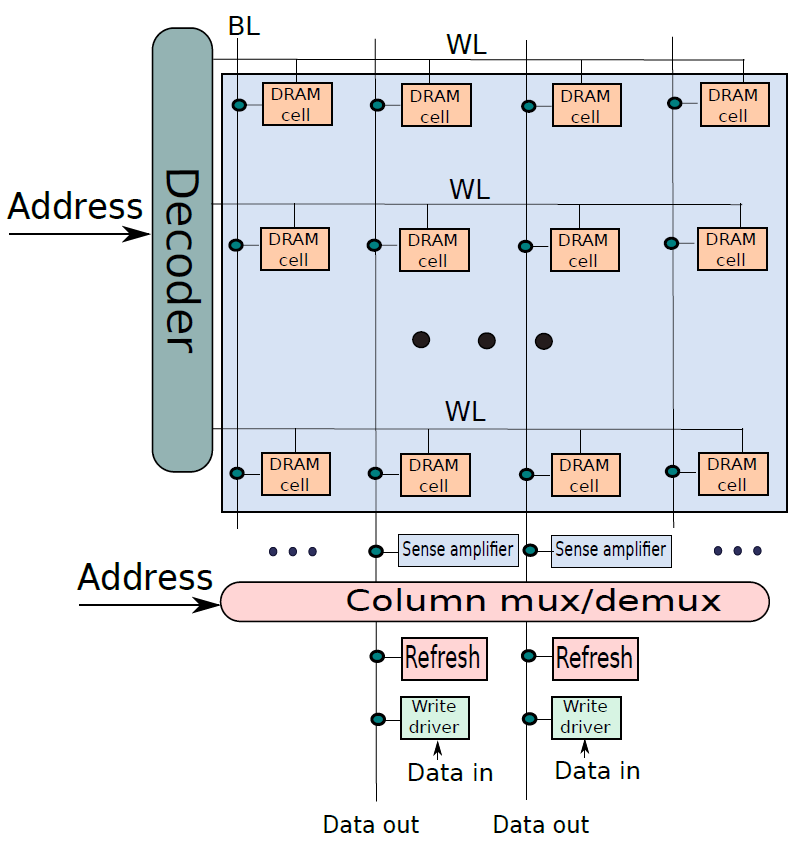

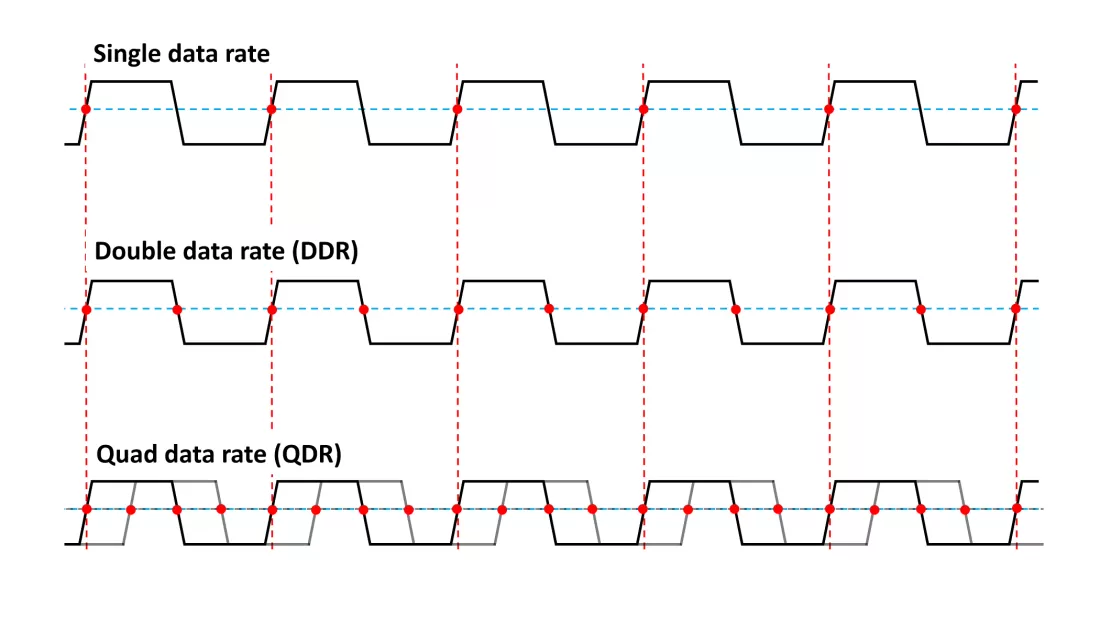

19.2.6.3 動態記憶體(DRAM)

現在來看看一種只使用一個電晶體來節省一點時間的記憶體技術,它非常密集、面積大,而且能效高,但比SRAM和鎖存器慢得多,適用於大型片外記憶體。

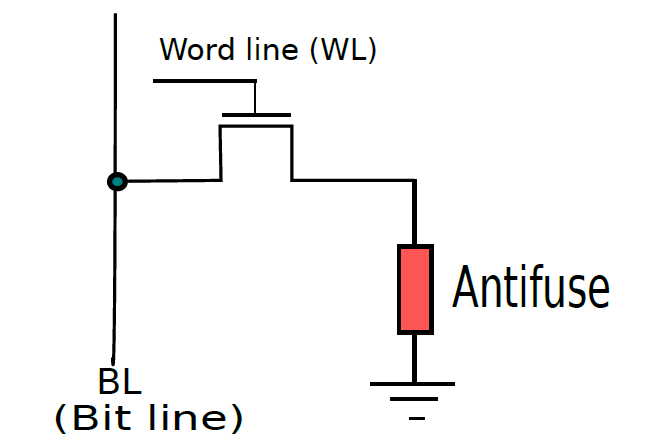

基本DRAM(動態記憶體)單元如下圖所示。單個電晶體的柵極連線到字線,從而啟用或禁用它,其中一個端子連線到儲存電荷的電容器。如果儲存的位是邏輯1,則電容器帶電,否則不帶電。

一個動態記憶體的單元。

DRAM和SRAM單元的對比圖。

因此,讀取和寫入值非常容易。我們需要首先設定字線,以便可以存取電容器。為了讀取該值,需要感測位線上的電壓。如果它處於地電位,則單元儲存0,否則如果它接近電源電壓,則儲存1。類似地,要寫入值,我們需要將位線(BL)設定為適當的電壓,並設定字線,電容器將相應地充電或放電。

然而,就DRAM而言,並非一切都是免費的。讓我們假設電容器被充電到等於電源電壓的電壓,實際上,電容器將通過電媒介和電晶體逐漸洩漏一些電荷。該電流很小,但在長時間內電荷的總損失可能很大,最終會使電容器放電。為了防止這種情況,有必要定期重新整理DRAM單元的值,亦即需要讀取並寫回資料值。這也需要在讀取操作之後完成,因為電容器在對位線充電時會損失一些電荷。現在讓我們嘗試製作一個DRAM單元陣列。

我們可以用建立SRAM單元陣列的方法構建DRAM單元陣列(下圖),有三點不同:

- 存在一條位線而不是兩條位線。

- 有一個連線到位線的專用重新整理電路。這在讀取操作後使用,也會定期呼叫。

- 在這種情況下,感測放大器出現在列複用器/解複用器之前。讀出放大器還為整個DRAM行(也稱為DRAM頁)快取資料。它們確保對同一DRAM行的後續存取是快速的,因為它們可以直接從讀出放大器進行服務。

DRAM單元陣列。

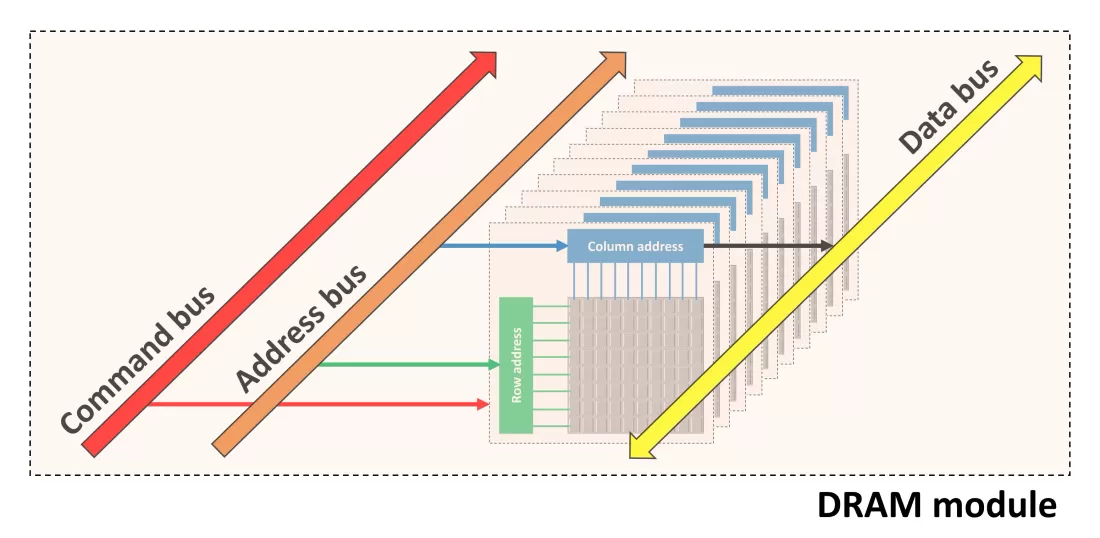

接下來簡述現代DRAM的時序方面。在過去的好日子裡,DRAM記憶體是非同步存取的,意味著DRAM模組沒有做出任何時序保證。但現在每個DRAM操作都與系統時鐘同步,因此,如今的DRAM晶片是同步DRAM晶片(SDRAM晶片)。

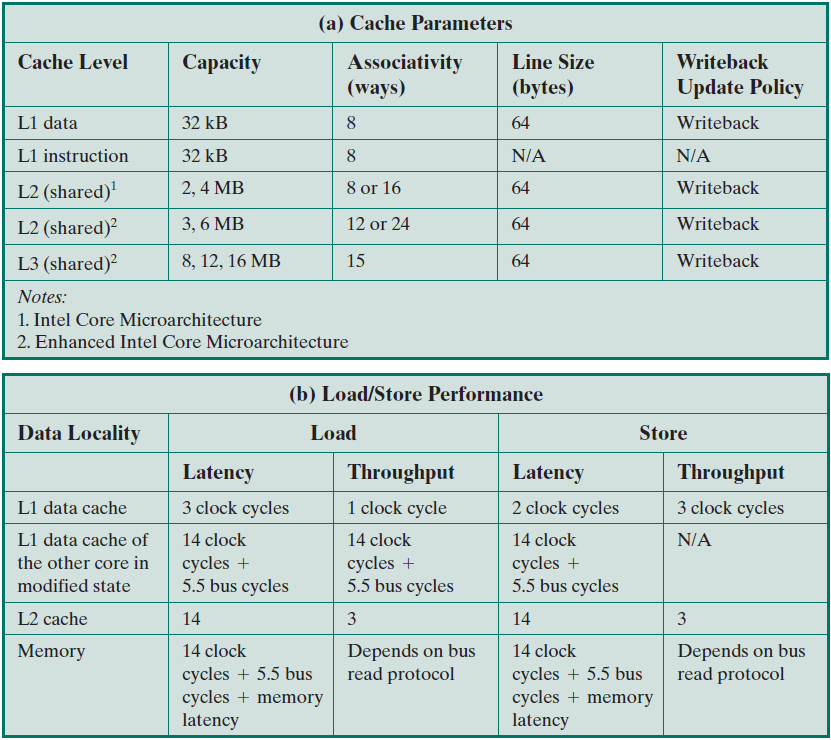

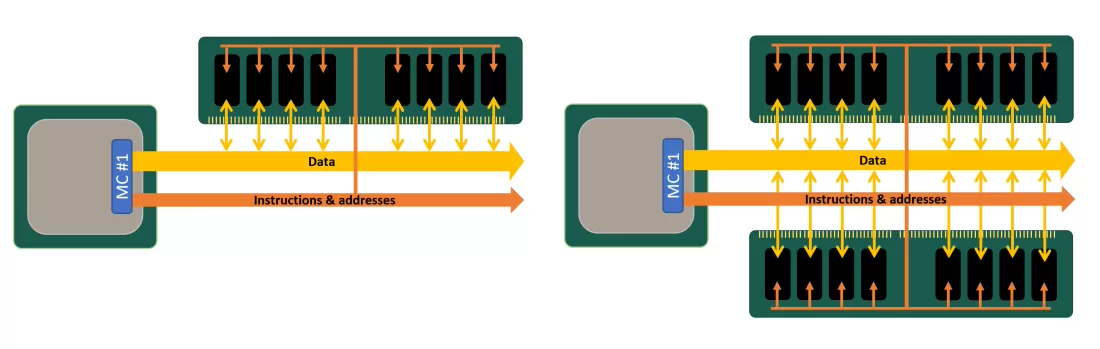

截至目前,同步DRAM記憶體通常使用DDR4或DDR5標準,DDR代表雙倍資料速率,使用最早標準DDR1的裝置在時鐘的上升沿和下降沿向處理器傳送8位元組的封包,DDR也被稱為雙峰(double pump)操作。DDR1的峰值資料速率為1.6 GB/s,後續的DDR世代通過以更高的頻率傳輸資料來擴充套件DDR1,例如,DDR2的資料速率是DDR1裝置的兩倍(3.2 GB/s),DDR3通過使用更高的匯流排頻率將峰值傳輸速率進一步提高了一倍,自2007年開始使用(峰值速率為6.4GB/s)。

19.2.6.4 唯讀記憶體(ROM)

唯讀記憶體可分為普通ROM和PROM(可程式化ROM),下面分別是它們的單元圖例。

(a) 儲存邏輯0的ROM單元;(b) 儲存邏輯1的ROM單元。

PROM單元。

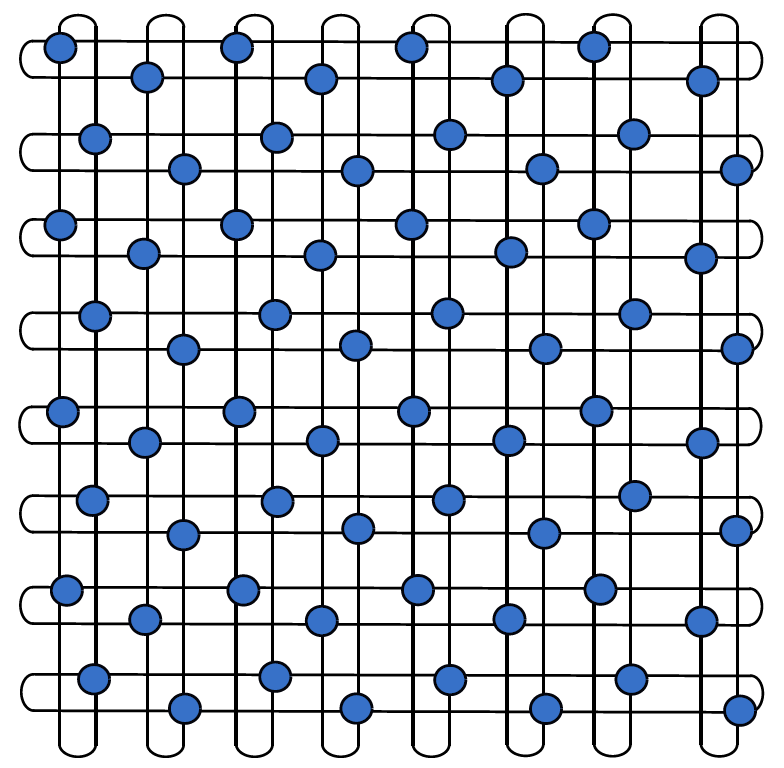

19.2.6.5 可程式化邏輯陣列

事實證明,我們可以很容易地用類似於PROM單元的儲存單元製作組合邏輯電路,這種器件被稱為可程式化邏輯陣列或PLA。PLA在實踐中用於實現由數十或數百個小項(minterm)組成的複雜邏輯函數,相對於由邏輯閘組成的硬連線電路的優勢在於它是靈活的,我們可以在執行時更改PLA實現的布林運算,相比之下,由矽製成的電路永遠不會改變其邏輯。其次,PLA的設計和程式設計更簡單,而且有很多軟體工具可以設計和使用PLA。最後,PLA可以有多個輸出,因此可以很容易地實現多個布林函數。這種額外的靈活性是有代價的,代價是效能。

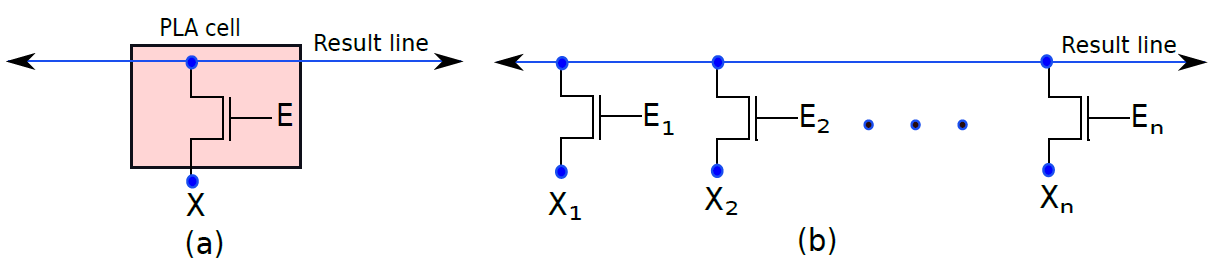

下圖(a)所示的PLA單元原則上類似於基本PROM單元。如果柵極處的值(E)等於1,則NMOS電晶體處於導通狀態。因此,NMOS電晶體的源極和漏極端子之間的電壓差非常小。換句話說,可以簡單地假設結果線的電壓等於訊號的電壓,X. If (E = 0),NMOS電晶體處於截止狀態。結果線是浮動的,並保持其預充電電壓。在這種情況下,我們建議推斷邏輯1。

現在讓我們構建一行PLA單元,其中每個PLA單元在其源極端子處連線到輸入線,如圖(b)所示。輸入編號為X1…Xn,所有NMOS電晶體的漏極連線到結果線,PLA單元的電晶體的柵極連線到一組使能訊號E1…En。如果任何一個使能訊號等於0,則該特定電晶體被禁用,我們可以將其視為從PLA陣列中邏輯移除。

一個PLA單元。

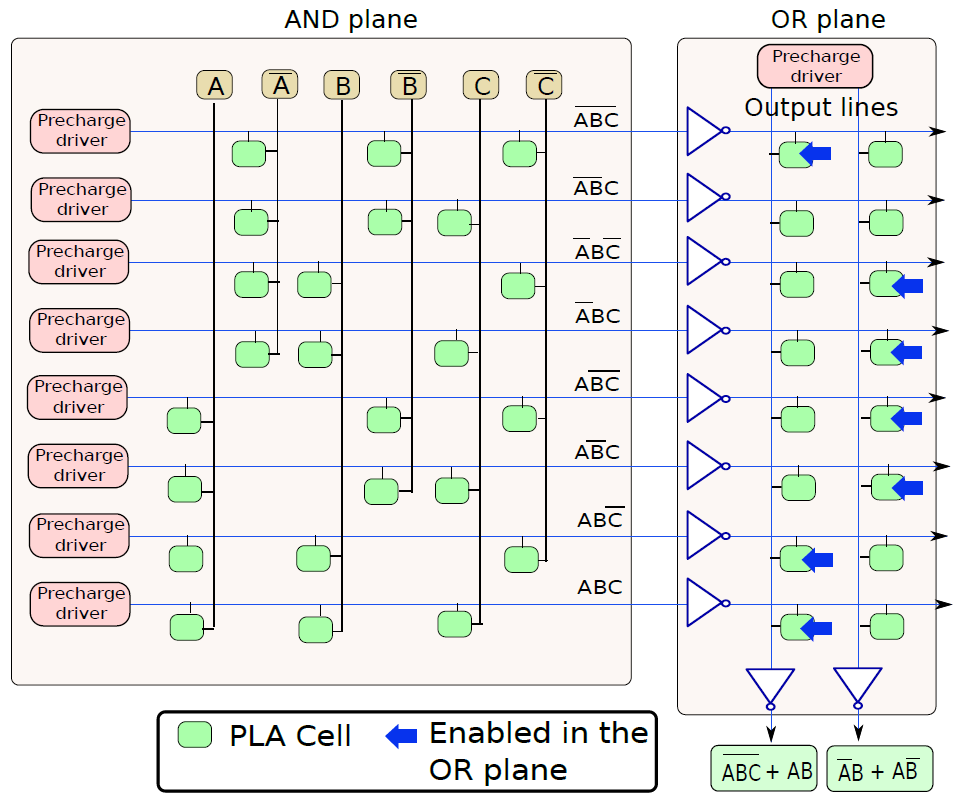

現在讓我們建立一個PLA單元格陣列,如下圖所示,每行對應一個minterm。對於我們的3變數範例,每行由6列組成,每個變數有2列(原始和補充),例如,前兩列分別對應於A和\(\overline{A}\)。在任何一行中,這兩列中只有一列包含PLA單元,因為A和\(\overline{A}\)不能同時為真。在第一行,計算最小項\(\overline{ABC}\)的值,因此第一行包含對應於\(\overline{A}\)、\(\overline{B}\)和\(\overline{C}\)的列中的PLA單元。我們在其餘行中為剩餘的minterm進行類似的連線,PLA陣列的這一部分被稱為AND平面,因為我們正在計算變數值(原始值或二補數值)的邏輯AND。PLA陣列的AND平面獨立於我們希望計算的布林函數,給定輸入,它計算所有可能的最小項的值。

PLA單元陣列。

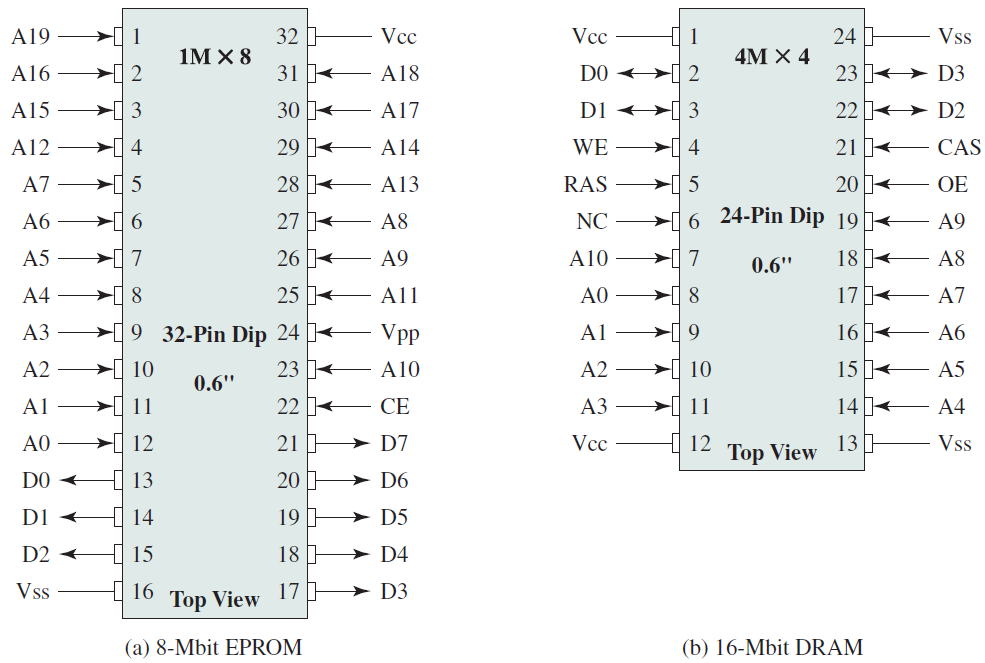

典型的記憶體封裝引腳和訊號。

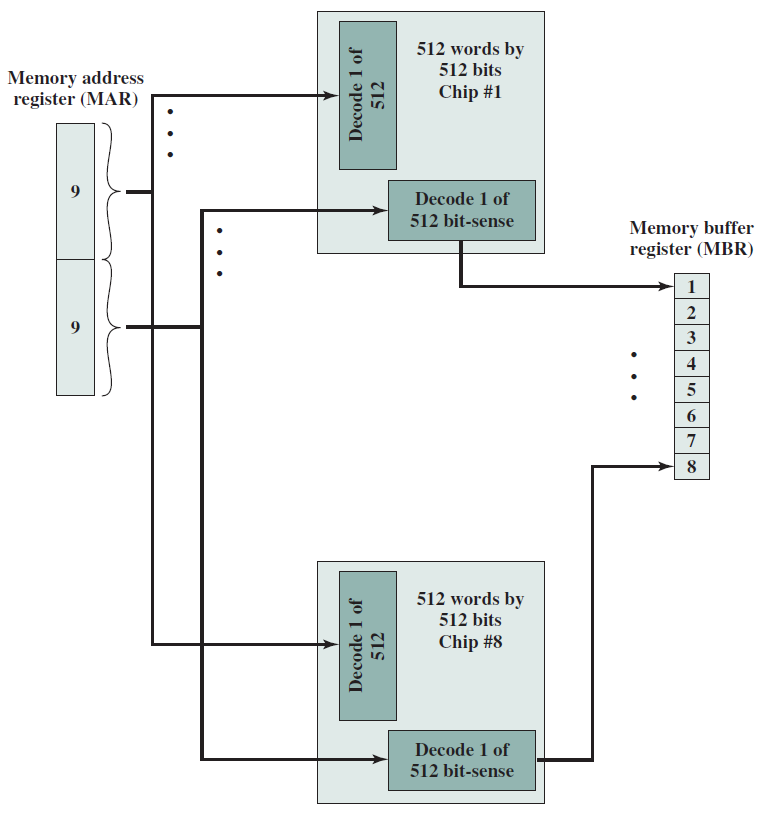

256 KB記憶體組織。

1MB記憶體組織。

DDR代次演進圖。

非易失性RAM技術。

上:簡化的DRAM讀取時序;下:Signetics 7489 SRAM的脈衝串。

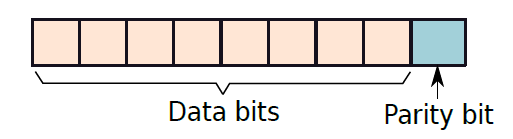

19.2.7 計算機算術

本節將設計算術運算的硬體演演算法,先闡整數運算的演演算法,如兩個二進位制數相加的基本演演算法,有很多方法可以完成這些基本操作,每種方法都有自己的優缺點。注意,二進位制減法的問題在概念上與2的二補數系統中的二進位制加法相同。因此,我們不需要單獨對待它。隨後,我們將看到,n個數的相加問題與乘法問題密切相關,而且這是一個硬體上的快速操作。遺憾的是,整數除法並不存在非常有效的方法。然而,我們將考慮兩種用於劃分正二進位制數的流行演演算法。

整數算術之後,我們將研究浮點(帶小數點的數位)算術的方法,大多數整數演演算法稍作修改後都可以移植到浮點數領域。與整數除法相比,浮點除法可以非常有效地完成。

19.2.7.1 加法

讓我們看看將兩個1位數位a和b相加的問題,a和b都可以取兩個值:0或1,因此,a和b有四種可能的組合,它們的二進位制和可以是00、01或10。當a和b均為1時,它們的和將是10,兩個1位數位的總和可能有兩位長。讓我們將結果的LSB稱為和,將MSB稱為進位,例如,把8和9相加,和是7,進位是1。

可以將和和進位的概念擴充套件到加三個1位數位。如果我們將三個1位數位相加,那麼結果的範圍是二進位制的00到11之間。

和(sum):總和是兩個或三個1位數位相加結果的LSB。

進位(carry):進位是兩個或三個1位數位相加結果的MSB。

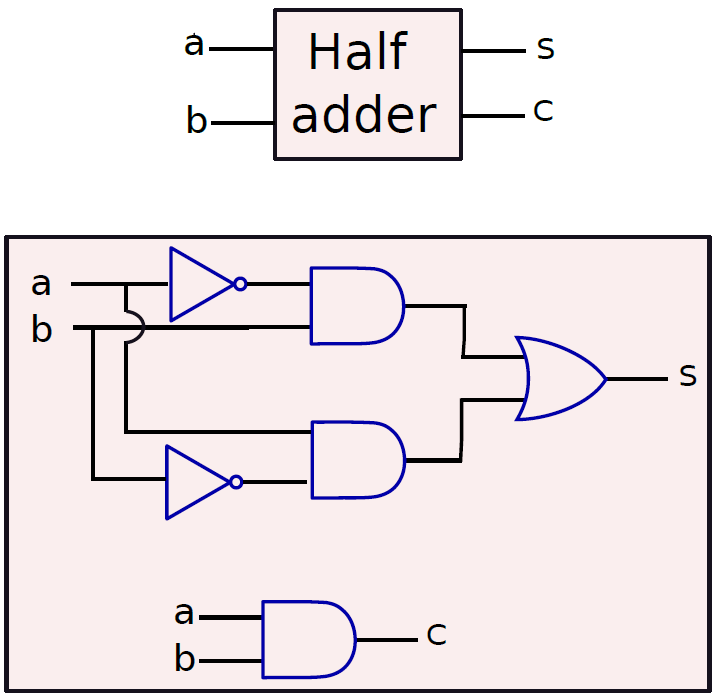

對於可以將兩個1位數位相加的加法器,將有兩個輸出位:和s和進位c,將兩個位相加的一個加法器稱為半加法器(half adder)。半加法的真值表如下表所示。

| a | b | s | c |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

半加法器。

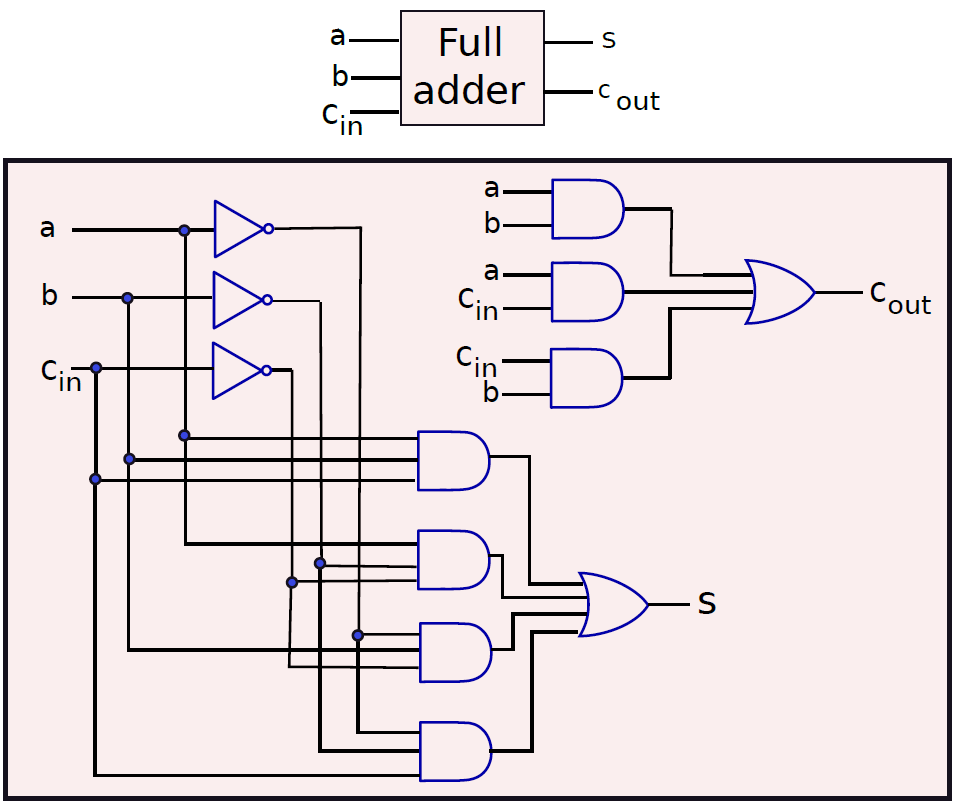

可以加3位的加法器稱為全加法器(full adder),它的電子構造如下:

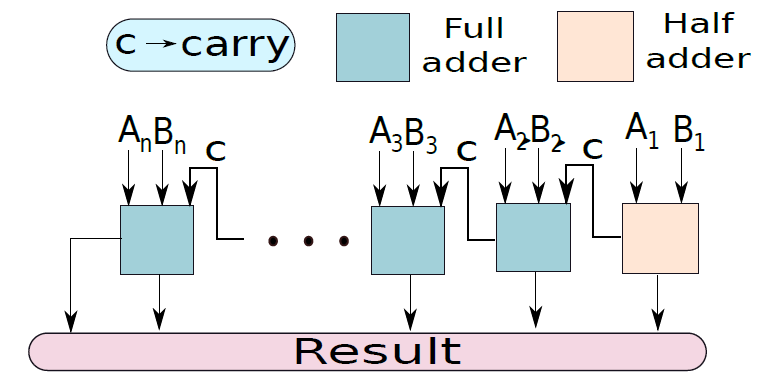

n位加法器被稱為紋波進位加法器(ripple carry adder),其設計如下所示:

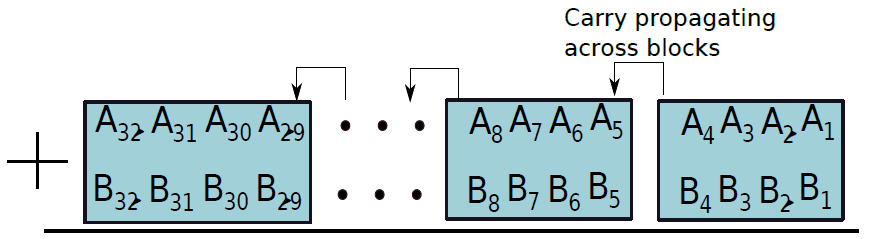

考慮將兩個數位A和B相加的問題,首先將位元集劃分為4位元的塊,如下圖所示,每個塊包含一個a片段和一個B片段。通過考慮塊的輸入進位將這兩個片段相加,並生成一組和位和一個進位,此進位是後續塊的輸入進位。

此外,還有超前進位加法器(Carry Lookahead Adder),其分為兩個階段,每個階段都擁有複雜的電子構造。

19.2.7.2 乘法

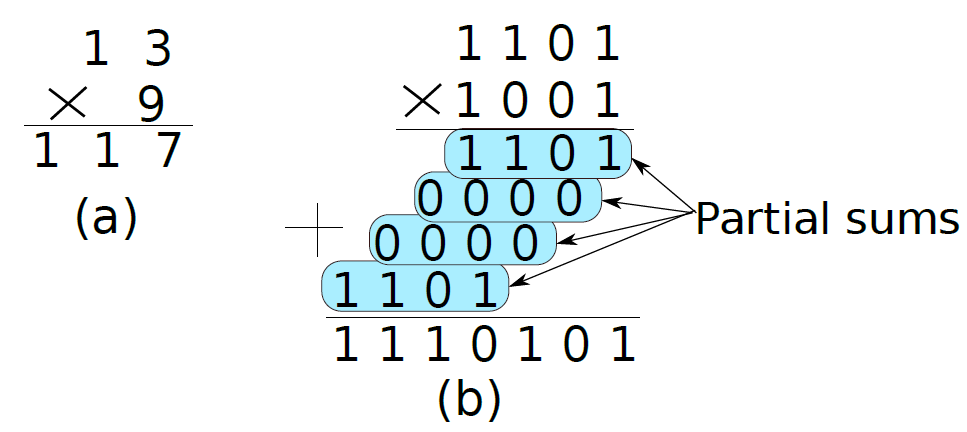

現與加法類似,先看看兩個十進位制數相乘的最簡單的方法,不妨嘗試將13乘以9。在這種情況下,13被稱為被乘數(multiplicand),9被稱為乘數(multiplier),117是乘積(product)。

下圖(a)顯示了十進位制的乘法,(b)顯示了二進位制的乘法。請注意,兩個二進位制數相乘的方法與十進位制數完全相同。我們需要考慮乘數從最小顯著位置到最大顯著位置的每一位。如果該位為1,那麼我們將被乘數的值寫在該行下方,否則我們將寫0。對於每個乘數位,我們將被乘數向左移動一位。其原因是每個乘數位代表2的更高冪。我們將每個這樣的值稱為部分和(見圖7.10(b))。如果乘法器有m位,那麼我們需要將m個部分和相加以獲得乘積。在這種情況下,乘積是十進位制117,二進位制1110101。讀者可以驗證它們實際上表示相同的數位。為了便於以後的表示,讓我們定義另一個稱為部分積的術語。它是部分和的連續序列的和。

(a)十進位制乘法;(b)二進位制乘法。

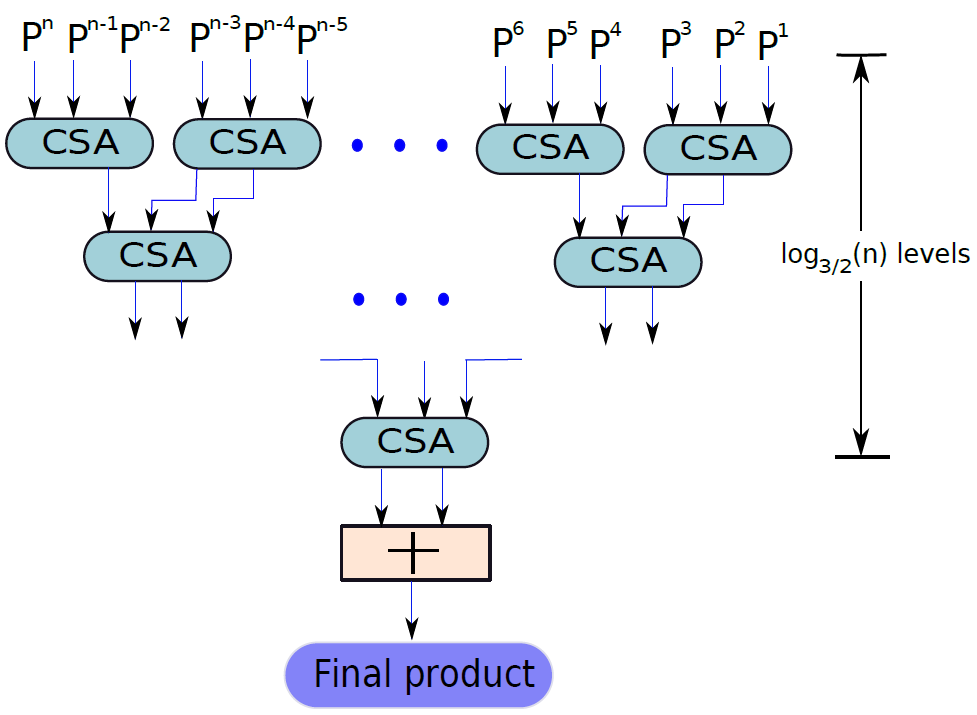

常規的乘法器是\(O(n^2)\),而改進版的Booth乘法器或Wallace樹形乘法器(下圖)可以做到\(O(log(n))\)的演演算法複雜度。

Wallace樹形乘數。

19.2.7.3 除法

現在讓我們看看整數除法。不幸的是,與加法、減法和乘法不同,除法是一個明顯較慢的過程。任何除法運算都可以表示如下:

N是被除數,D是除數,Q是商,R是餘數。假定除數和被除數為正,除法過程需要滿足以下屬性:

- \(R < D\)且\(R \ge 0\)。

- Q是滿足上述等式的最大正整數。

如果我們想除掉負數,那麼首先將它們轉換成正數,進行除法,然後調整商和餘數的符號,部分ISA試圖確保餘數始終為正。在這種情況下,需要將商減1,並將除數與餘數相加,使其為正。

實現除法的方式有迭代除法、佘數恢復除法(Restoring Division)、非餘數恢復除法(Non-Restoring Division)等。本文忽略這些演演算法的具體描述,有興趣的童鞋可以自行查閱資料。

19.2.7.4 浮點數運算

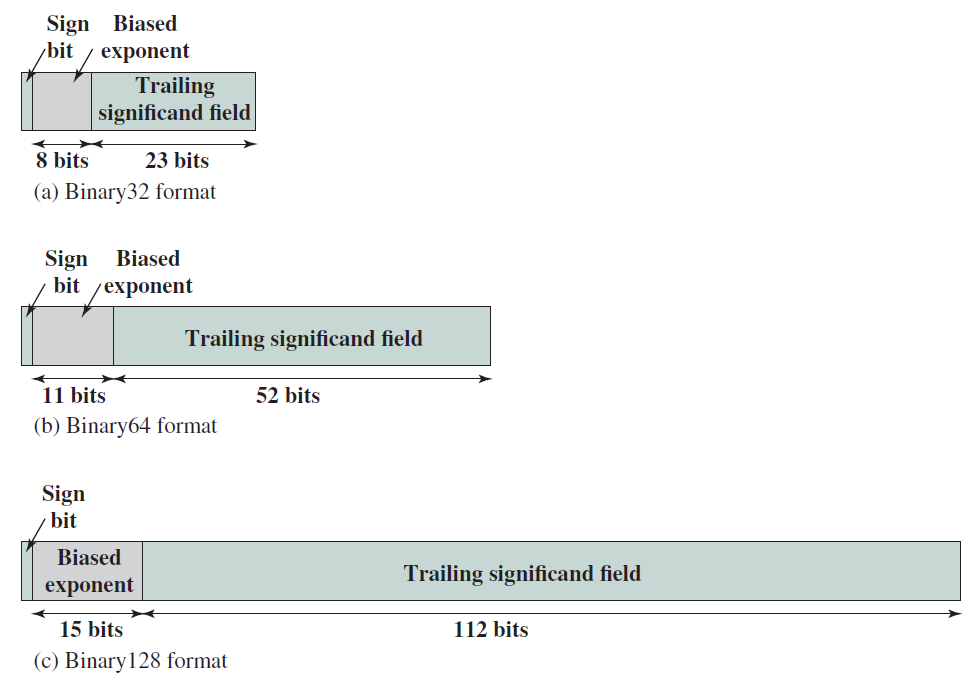

浮點加法和減法的問題實際上是同一問題的不同方面。A-B可以用兩種方式解釋,可以說正在從A中減去B,也可以說在將-B加到A中。因此,與其單獨看減法,不如將其視為加法的特例。浮點數的二進位制表示、屬性和特殊含義可以參見:17.2.2 浮點數。

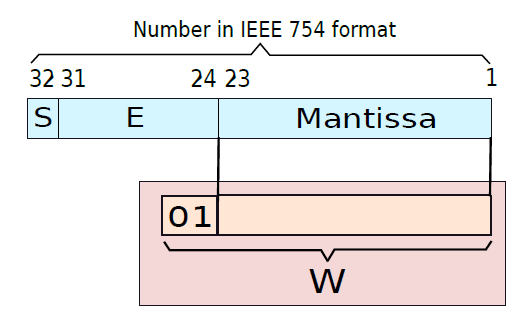

下圖顯示了一個範例,說明了如何將有效位解壓縮,並將其放入普通浮點數的暫存器中。在32位元IEEE 754格式中,尾數有23位,小數點前有0或1。因此,有效位需要24位元,如果我們希望新增前導符號位(0),那麼我們需要25位儲存。讓我們把這個號碼儲存在一個暫存器中,並稱之為W。

展開有效位並放入暫存器。

IEEE 754格式。

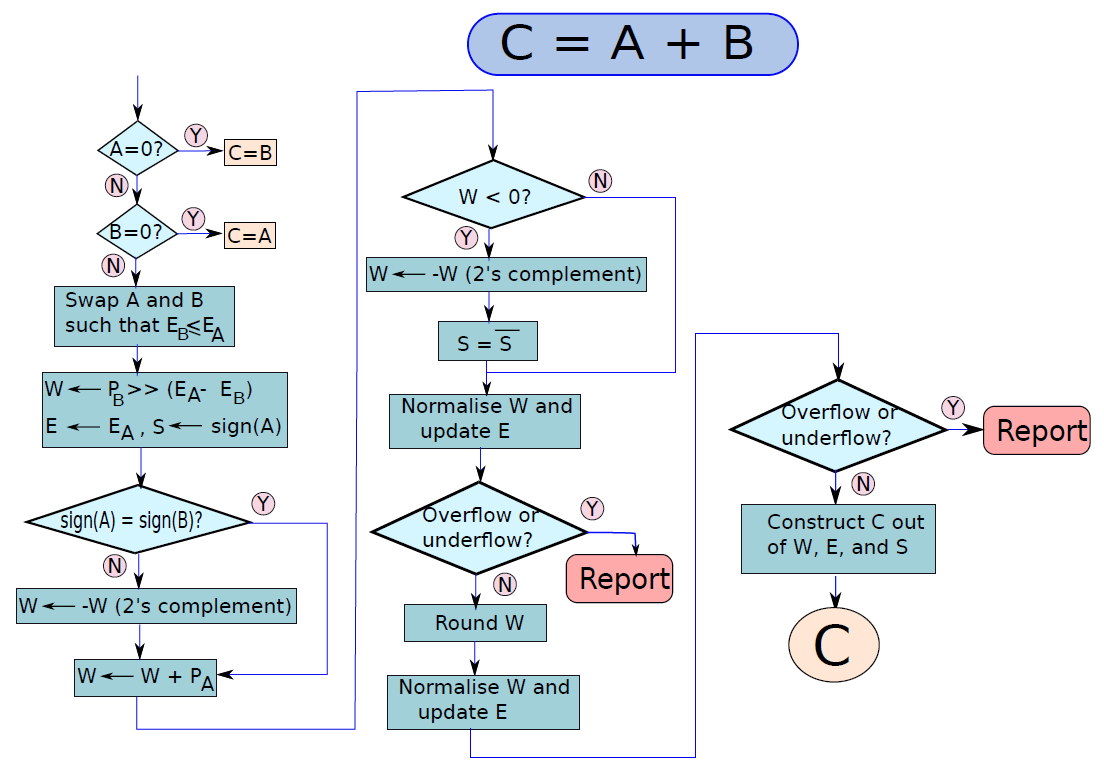

浮點數的運算涉及舍入等考量,下圖顯示了兩個浮點數相加的演演算法,考慮了0值。

累加兩個浮點值的流程圖。

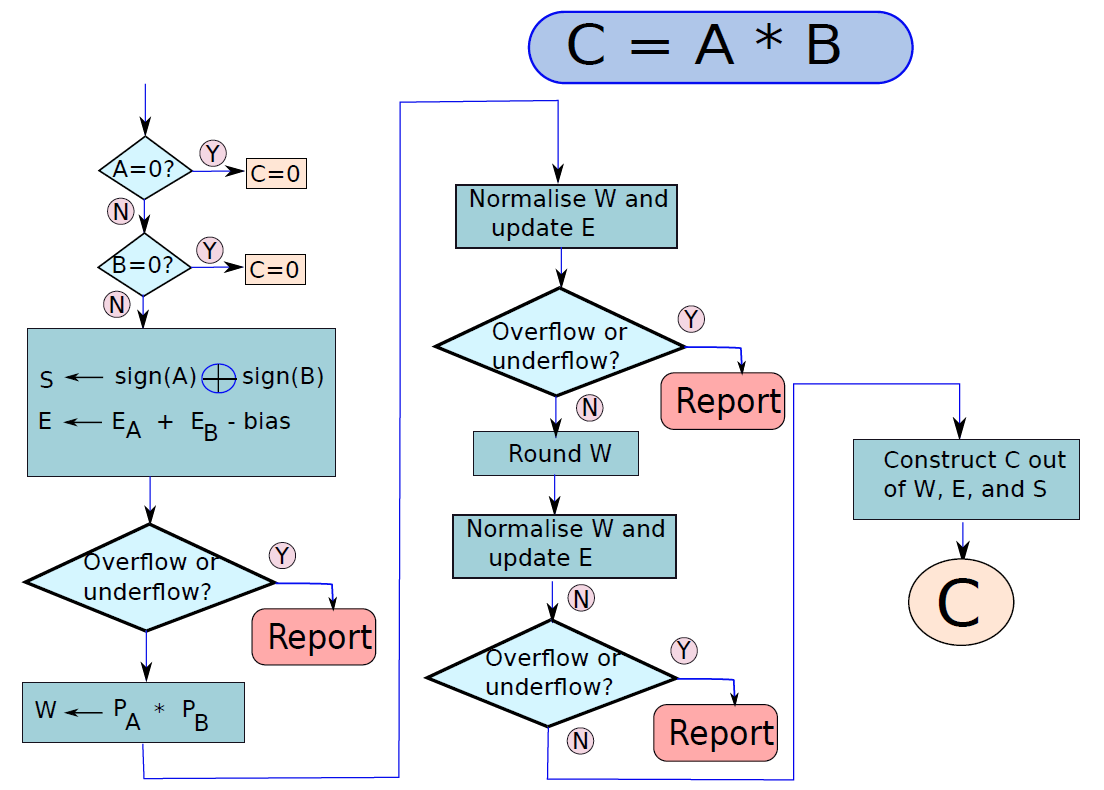

浮點數相乘演演算法與泛型加法演演算法的形式完全相同,只需幾步。讓我們嘗試乘以A x B以獲得乘積C,乘法的流程圖如下圖所示。在乘法的情況下,我們不必對齊指數,如下初始化演演算法,將B的符號和裝入暫存器W,W的寬度等於運算元大小的兩倍,就可以容納乘積。E暫存器初始化為\(E_A+E_B - bias\),因為在乘法的情況下,指數相加,減去bias以避免重複計數,計算結果的符號很簡單。

兩個浮點值相乘的流程圖。

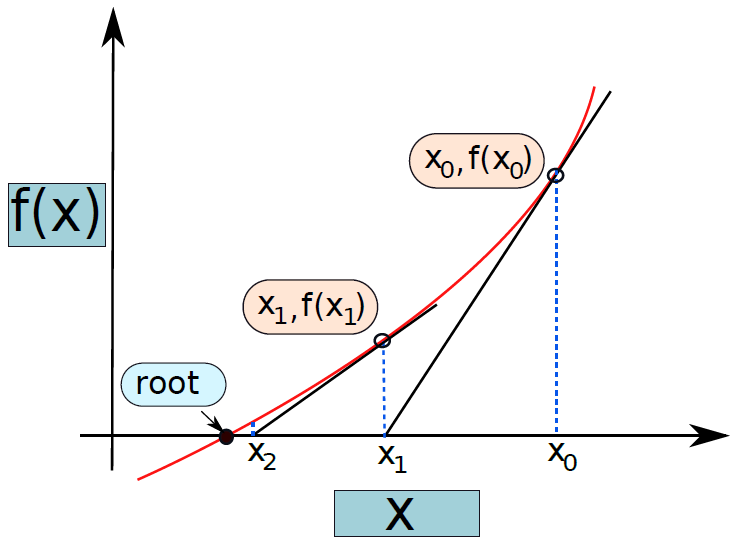

此外,還有Goldschmidt除法以及Newton-Raphson除法。

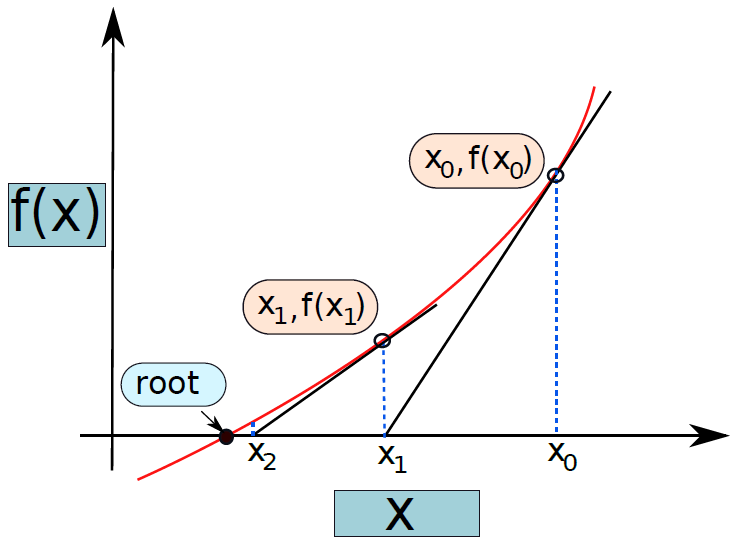

Newton-Raphson方法。

19.3 計算機架構和組織

19.3.1 計算機層級

計算機系統級層次結構是將計算機與使用者連線起來並使用計算機的不同級別的組合,還描述瞭如何在計算機上執行計算活動,並顯示了在不同級別的系統中使用的所有元素。通用的計算機系統級層次結構由7個級別組成:

| 層級 | 功能 | 舉例 | 解析 |

|---|---|---|---|

| 層6 | 使用者 | 可執行程式 | 包含使用者和可執行程式。 |

| 層5 | 高階語言 | C++、Java | 高階語言套件括 C++、Java、FORTRAN和許多其他語言,是使用者發出命令的語言。 |

| 層4 | 組合語言 | 組合程式碼 | 組合語言是計算機系統的下一個層次。機器只理解組合語言,因此按照順序,所有高階語言都在組合語言中進行了更改,組合程式碼是為它編寫的。 |

| 層3 | 系統軟體 | 作業系統 | 系統軟體種類繁多,主要幫助操作程序,並建立硬體和使用者介面之間的連線,可能包括作業系統、庫程式碼等。 |

| 層2 | 機器 | 指令集架構(ISA) | 在計算機系統中使用不同型別的硬體來執行不同型別的活動,包含指令集架構。 |

| 層1 | 控制層 | 微碼(microcode) | 控制是系統中使用微碼的級別,控制單元包括在這一級別的計算機系統中。 |

| 層0 | 數位邏輯 | 電路、門 | 數位邏輯是數位計算的基礎,提供了對計算機內電路和硬體如何通訊的基本理解,由各種電路和門等組成。 |

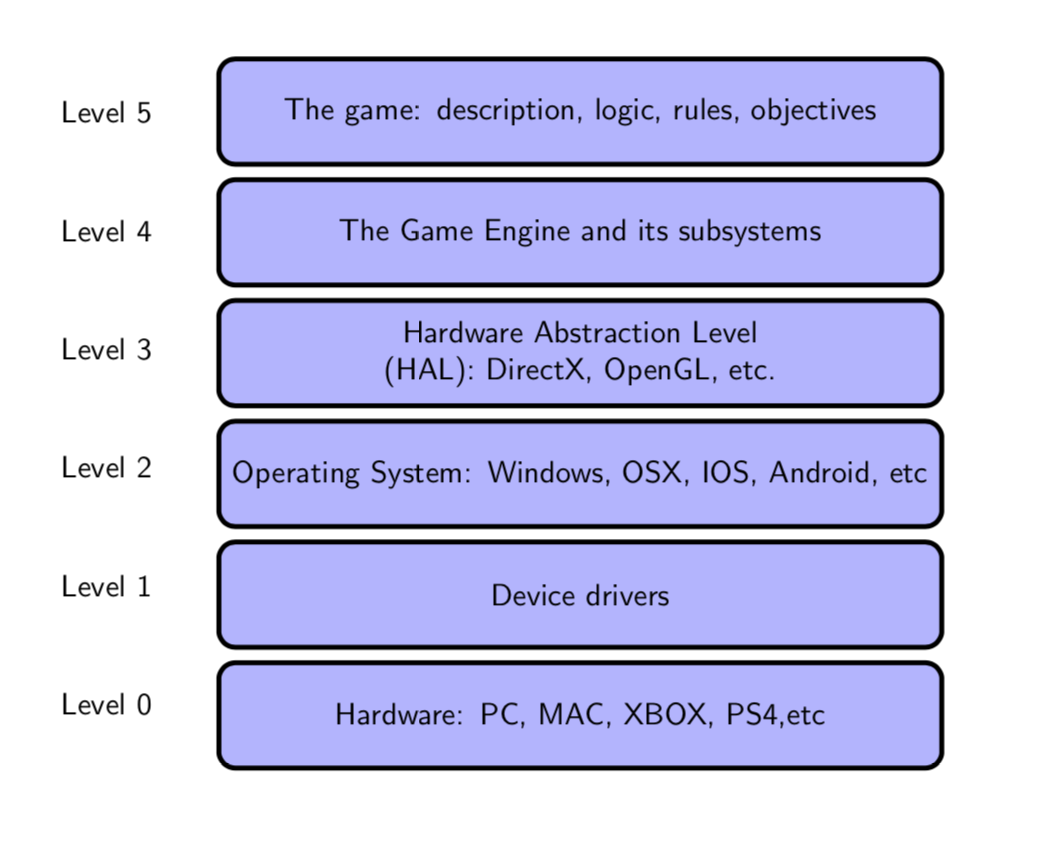

當然,也存在另一種層級劃分,從上到下分別是:遊戲應用、遊戲引擎、圖形API、作業系統、裝置驅動、硬體裝置。

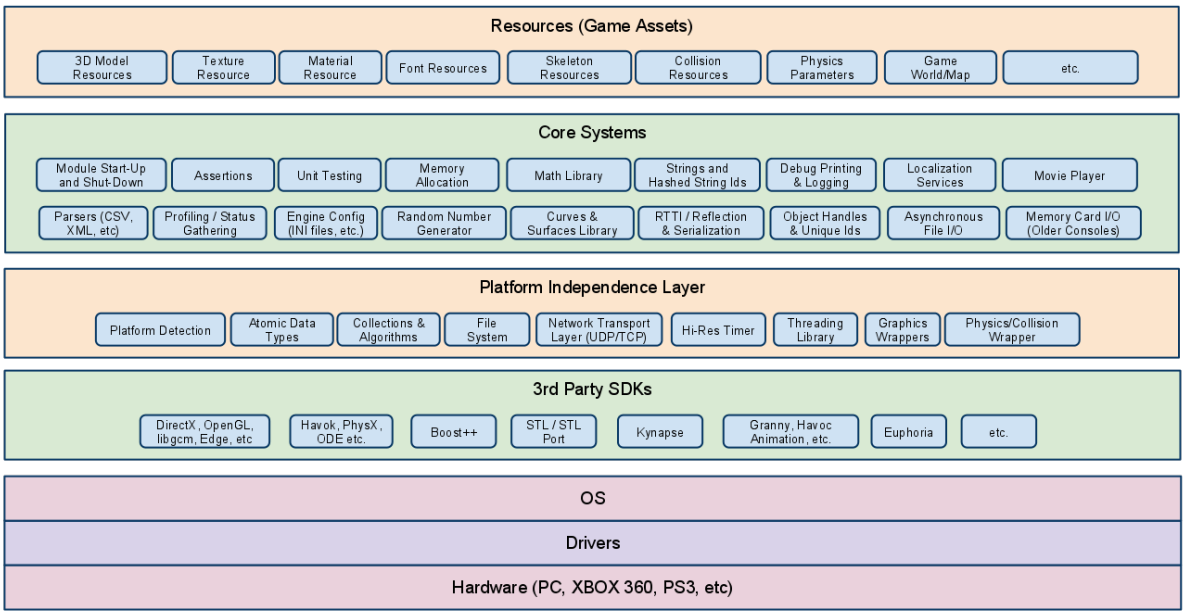

下圖是更加詳細的層級模組,其中作業系統(OS)處於圖形API等第三方SDK和驅動之間,充當著承上啟下的重要作用和通訊橋樑,是整個計算機層級架構極其重要的組成部分。

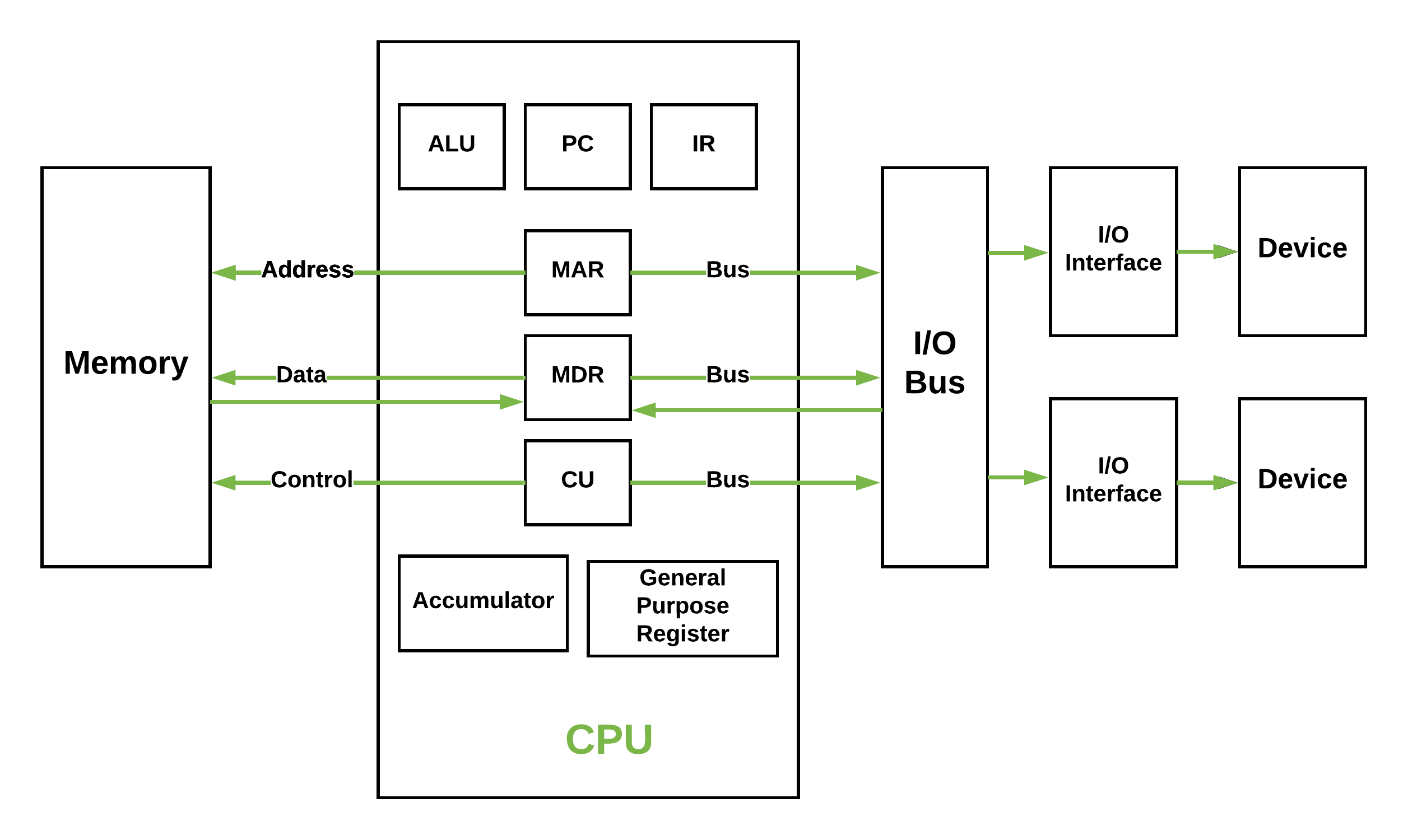

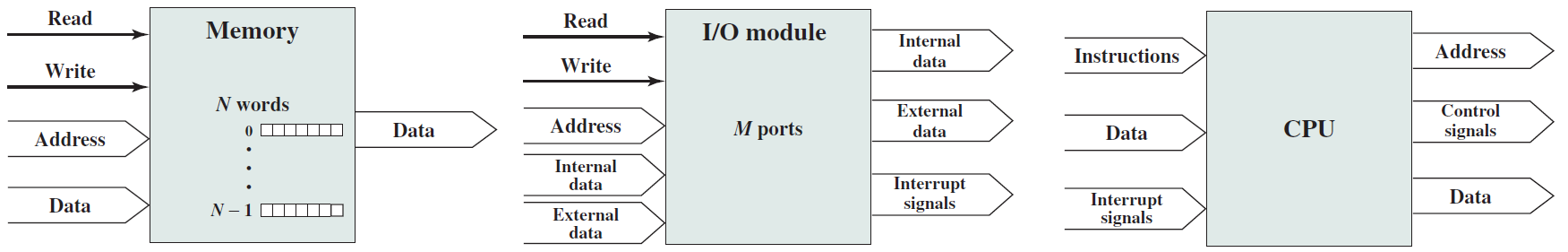

在底層,計算機硬體由處理器、記憶體和I/O元件組成,每種型別有一個或多個模組。這些元件以某種方式互連,以實現計算機的主要功能,即執行程式。有四個主要結構要素:

- 處理器:控制計算機的操作並執行其資料處理功能。當只有一個處理器時,它通常被稱為中央處理單元(CPU)。

- 主記憶體儲器:儲存資料和程式。易丟失,當計算機關閉時,記憶體中的內容會丟失。相反,即使計算機系統關閉,磁碟記憶體的內容也會保留。主記憶體儲器也稱為實記憶體或主記憶體儲器。

- I/O模組:在計算機及其外部環境之間行動資料外部環境由各種裝置組成,包括輔助記憶體裝置(如磁碟)、通訊裝置和終端。

- 系統匯流排:提供處理器、主記憶體儲器和I/O模組之間的通訊。

19.3.2 架構vs組織

計算機架構(Computer Architecture)是對計算機各個部分的需求和設計實現的功能描述,處理計算機系統的功能行為。在設計計算機時,它出現在計算機組織之前。

計算機組織(Computer Organization)出現在計算機體系架構之後,是操作屬性如何連結在一起並有助於實現架構規範的方式,處理的是結構關係。

簡單而言,架構是呈現給軟體設計師的計算機檢視,組織是計算機在硬體上的實際實現。

計算機的層級設計、硬體、軟體和架構、組織的關係圖。

數位計算機方框圖。

計算機體系架構和計算機組織之間的詳細區別如下表:

| 計算機架構 | 計算機組織 | |

|---|---|---|

| 1 | 描述計算機的功能。 | 描述計算機是如何做到的。 |

| 2 | 處理計算機的功能行為。 | 處理計算機的結構關係。 |

| 3 | 在上圖,很明顯它處理的是高層級的設計問題。 | 在上圖,也很明顯它處理的是低層級的設計問題。 |

| 4 | 表明硬體。 | 表明效能。 |

| 5 | 作為程式設計師,可以將架構視為一系列指令、定址模式和暫存器。 | 架構的實現稱為組織。 |

| 6 | 對於設計一臺計算機,它的架構是固定的。 | 為了設計一臺計算機,它的組織根據其架構而定。 |

| 7 | 也被稱為指令集架構 (ISA)。 | 通常被稱為微體系架構(microarchitecture)。 |

| 8 | 包括邏輯功能,例如指令集、暫存器、資料型別和定址模式。 | 由電路設計、外圍裝置和加法器等物理單元組成。 |

| 9 | 架構類別:馮諾依曼、Harvard、ISA、系統設計。 | CPU組織根據地址欄位的數量分為三類:單累加器組織、通用暫存器組織、堆疊組織。 |

| 10 | 使計算機的硬體可見。 | 提供了有關計算機效能的詳細資訊。 |

| 11 | 協調系統的硬體和軟體。 | 處理系統中的網路段。 |

| 12 | 軟體開發人員意識到它。 | 它逃脫了軟體程式設計師的檢測。 |

| 13 | 範例:Intel和AMD建立了x86處理器,Sun Microsystems和其他公司建立了SPARC處理器,Apple、IBM和摩托羅拉建立了PowerPC。 | 組織質量包括程式設計師看不到的硬體元素,例如計算機和外圍裝置的介面、記憶體技術和控制訊號。 |

19.3.3 馮·諾伊曼架構

歷史上有兩種型別的計算機:

- 固定程式計算機:它們的功能非常具體,不能重新程式設計,例如計算器。

- 儲存程式計算機:可以被程式設計以執行許多不同的任務,應用程式儲存在它們上面,因此得名。

現代計算機基於John Von Neumann(約翰·馮·諾依曼)引入的儲存程式概念。在這種儲存程式的概念中,程式和資料儲存在稱為記憶體的單獨儲存單元中,並被同等對待,意味著用這種架構構建的計算機將更容易重新程式設計。 其基本結構是這樣的:

有著輸入、處理、輸出等概念和組成的計算機模型稱為馮·諾伊曼架構,它是一種將程式指令記憶體和資料記憶體合併在一起的電腦設計概念結構,是一種實現通用圖靈機的計算裝置,以及一種相對於平行計算的序列式結構參考模型(referential model)。馮·諾伊曼隱式指導了將儲存裝置與中央處理器分開的概念,也被稱為ISA(指令集架構)計算機。

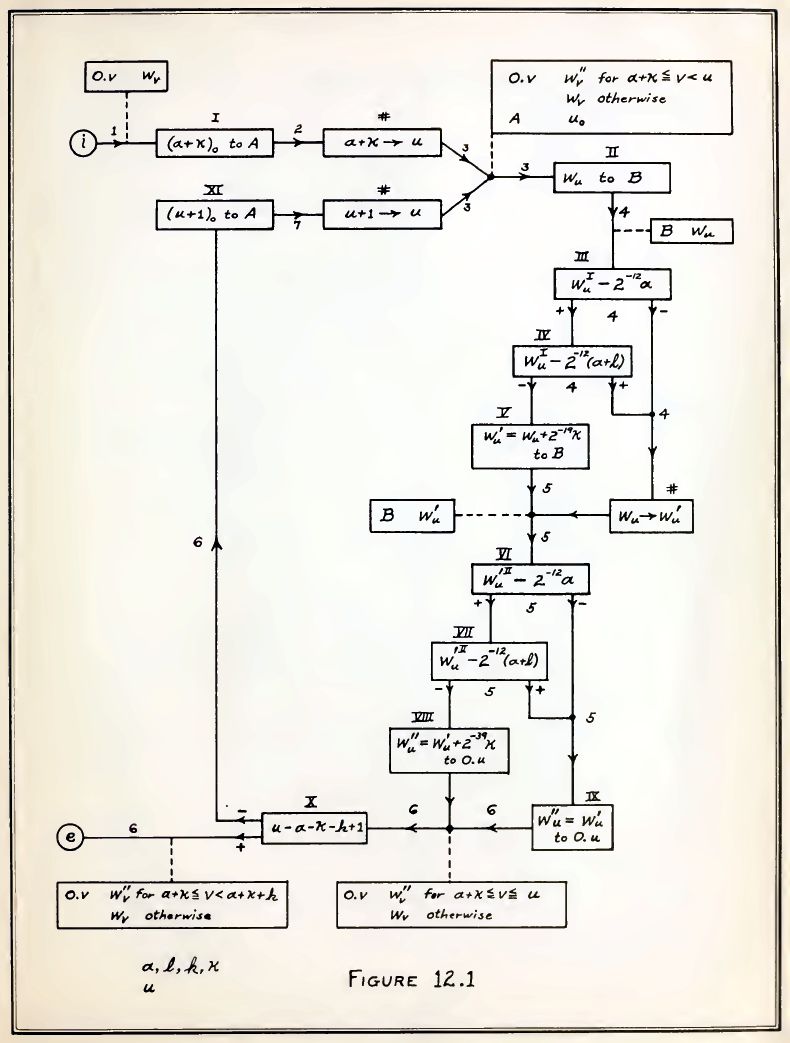

馮·諾依曼1947年出版的《電子計算儀器問題的規劃和編碼》中的流程圖。

馮·諾依曼結構的抽象組成如下:

更進一步地,它約定了用二進位制進行計算和儲存,還定義計算機基本結構為5個部分,分別是中央處理器(CPU)、記憶體、輸入裝置、輸出裝置、匯流排。

結合上圖,各部分結構的具體描述如下:

-

記憶體:程式碼跟資料在RAM跟ROM中是線性儲存, 資料儲存的單位是一個二進位制位,最小的儲存單位是位元組。

-

匯流排:匯流排是用於 CPU 和記憶體以及其他裝置之間的通訊,匯流排主要有三種:

-

地址匯流排:用於指定 CPU 將要操作的記憶體地址。

-

資料匯流排:用於讀寫記憶體的資料。

-

控制匯流排:用於傳送和接收訊號,比如中斷、裝置復位等訊號,CPU收到訊號後響應,這時也需要控制匯流排。

-

-

輸入/輸出裝置:輸入裝置向計算機輸入資料,計算機經過計算後,把資料輸出給輸出裝置。比如鍵盤按鍵時需要和CPU進行互動,這時就需要用到控制匯流排。

-

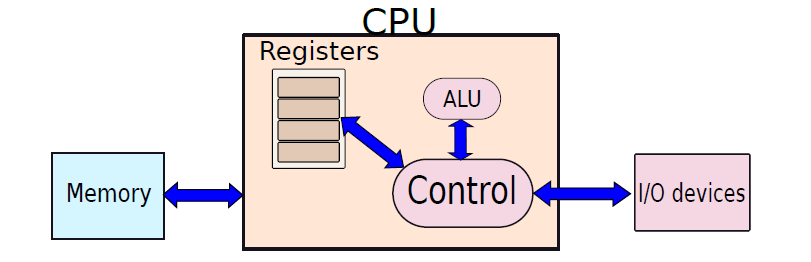

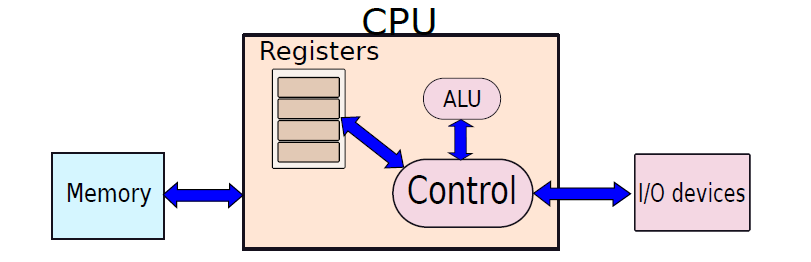

CPU:中央處理器,類比人腦,作為計算機系統的運算和控制核心,是資訊處理、程式執行的最終執行單元。它的結構如下所示:

- 控制單元(CU):處理所有處理器控制訊號,指導所有輸入和輸出流,獲取指令程式碼,並控制資料在系統中的移動方式。

- 算術邏輯單元 (ALU) :處理CPU可能需要的所有計算(如加法、減法、比較),執行邏輯運算、位移運算和算術運算。

- 主記憶體儲器單元(暫存器):CPU用暫存器儲存計算時所需資料,暫存器一般有以下幾種:

- 累加器(Accumulator):儲存ALU的計算結果。

- 程式計數器(PC):跟蹤要處理的下一條指令的記憶體位置,然後PC將下一個地址傳遞給記憶體地址暫存器 (MAR)。

- 記憶體地址暫存器(MAR):儲存需要從記憶體中取出或儲存到記憶體中的指令的記憶體位置。

- 記憶體資料暫存器(MDR):儲存從記憶體中獲取的指令或任何要傳輸到記憶體並儲存在記憶體中的資料。

- 指令暫存器(IR):可分為兩種:

- 當前指令暫存器(CIR):在等待編碼和執行時儲存最近獲取的指令。

- 指令緩衝暫存器(IBR):不立即執行的指令放在指令緩衝暫存器IBR中。

- 通用暫存器(GPR):存放需要進行運算的資料,比如需進行加法運算的兩個資料。

在馮諾伊曼體系下計算機指令執行的簡要過程如下:

- CPU讀取程式計數器獲得指令記憶體地址,CPU控制單元操作地址匯流排從記憶體地址拿到資料,資料通過資料匯流排到達CPU被存入指令暫存器。

- CPU分析指令暫存器中的指令,如果是計算型別的指令交給邏輯運算單元,如果是儲存型別的指令交給控制單元執行。

- CPU 執行完指令後程式計數器的值通過自增指向下個指令,比如32位元CPU會自增4。

- 自增後開始順序執行下一條指令,不斷迴圈執行直到程式結束。

馮諾依曼瓶頸(Von Neumann bottleneck)是無論做什麼來提升效能,都無法擺脫這樣一個事實,即一次只能執行一條指令,並且只能按順序執行,這兩個因素都阻礙了CPU的能力。我們可以為馮諾依曼處理器提供更多快取、更多RAM或更快的元件,但如果要在CPU效能方面取得原始收益,則需要對CPU設定進行有影響力的檢查。 這種架構非常重要,用於PC乃至超級計算機。

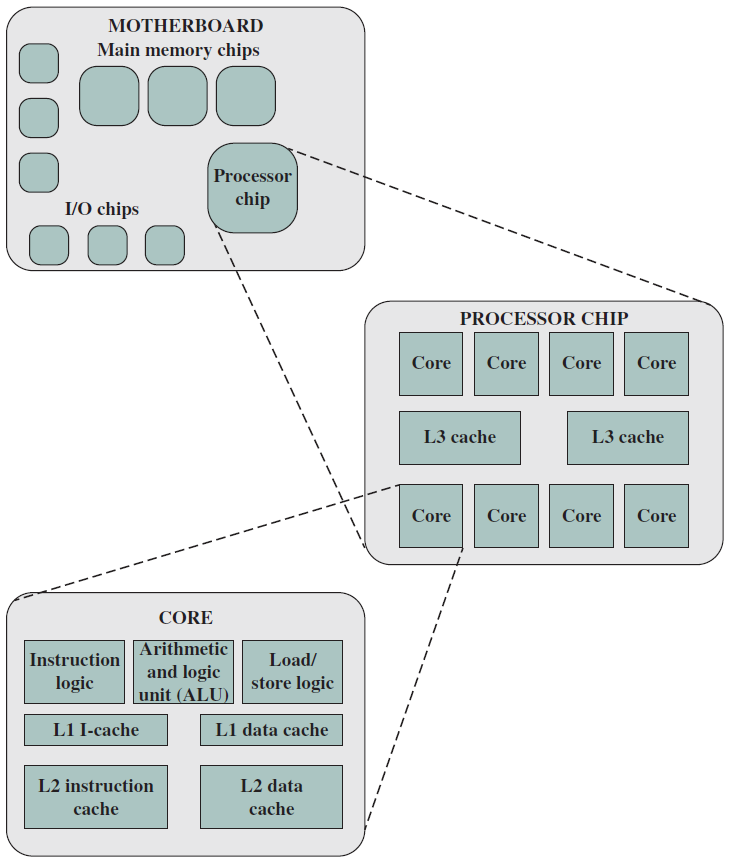

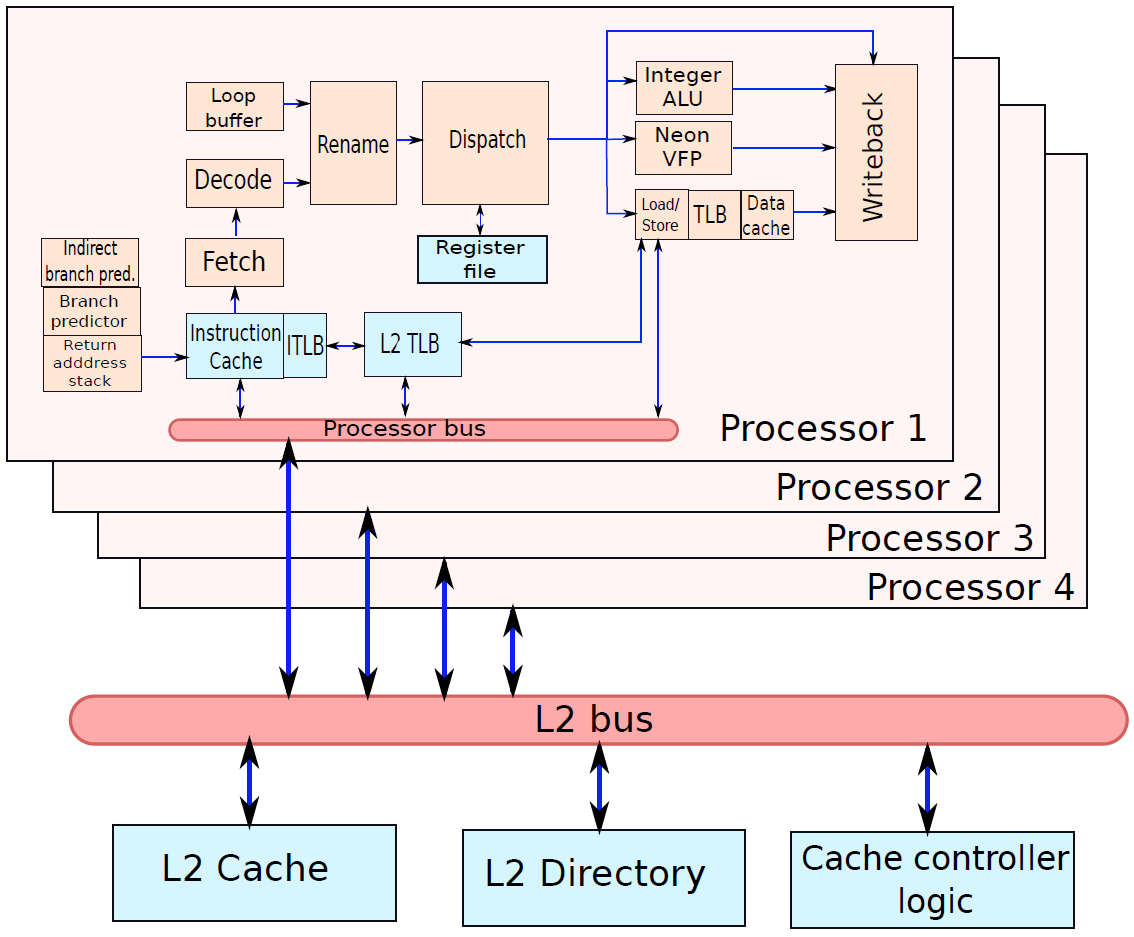

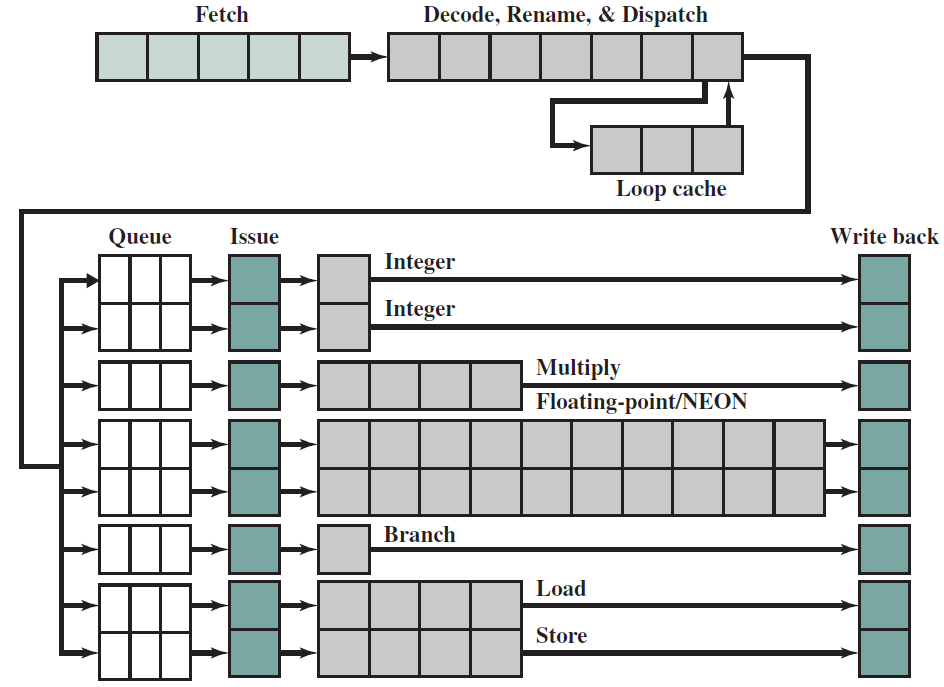

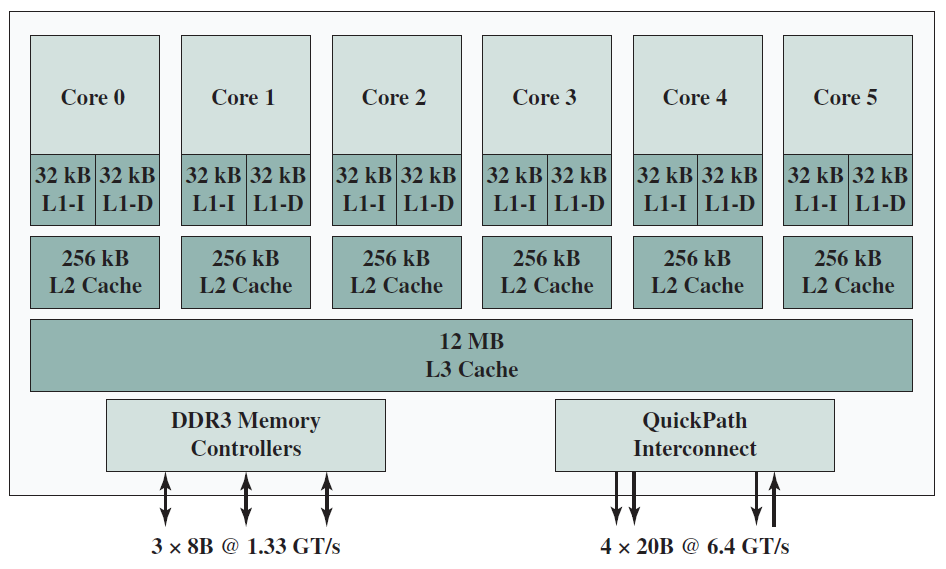

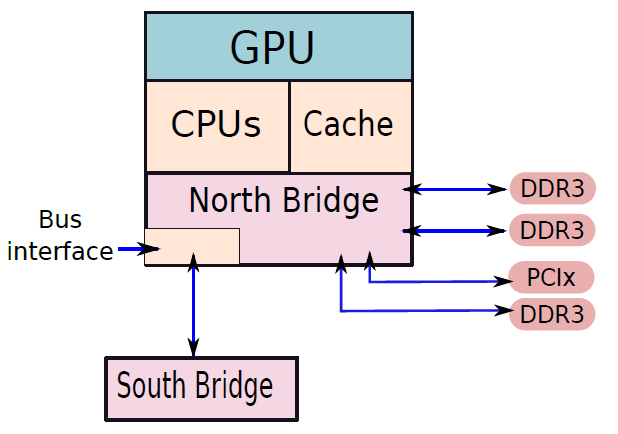

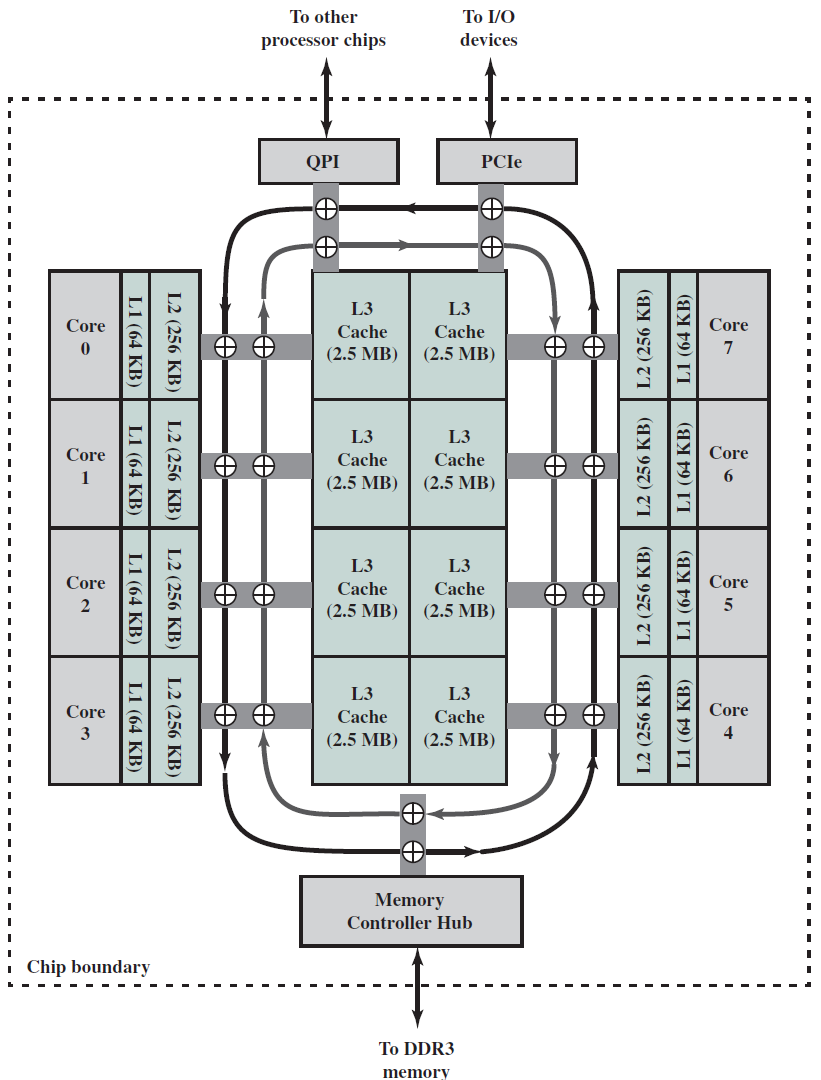

19.3.4 多核結構

下圖是典型多核計算機主要部件的簡化檢視。大多數計算機,包括智慧手機和平板電腦中的嵌入式計算機,以及個人計算機、筆記型電腦和工作站,都安裝在主機板上。印刷電路板(PCB)是一種剛性的平板,用於固定和互連晶片和其他電子部件,該電路板由通常為兩到十層的層組成,這些層通過蝕刻到電路板中的銅路徑將元件互連。計算機中的主要印刷電路板稱為系統板或主機板,而插入主機板插槽的較小的印刷電路板則稱為擴充套件板。主機板上最突出的元素是晶片,晶片是一塊半導體材料,通常是矽,在其上製造電子電路和邏輯閘,所得產品稱為積體電路。

多核計算機主要元件的簡化檢視。

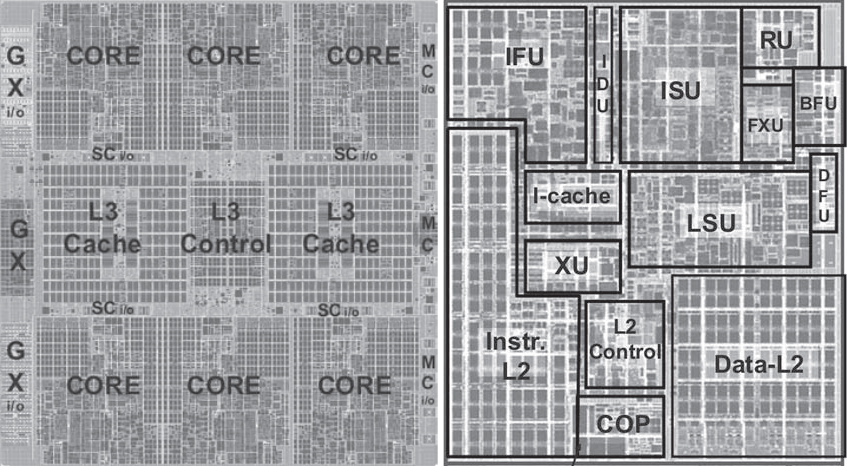

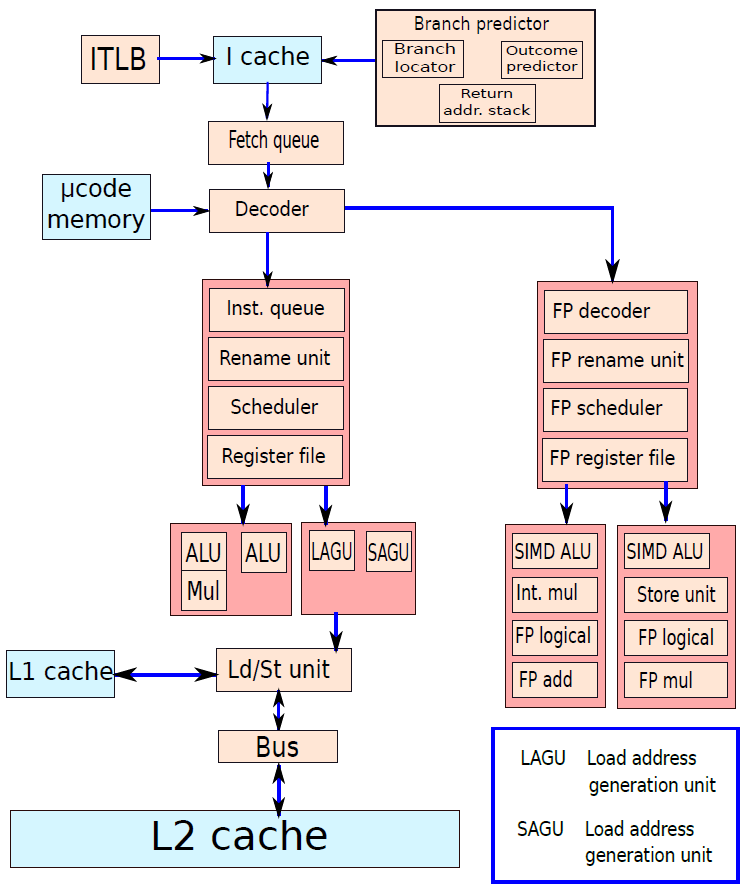

下圖左是IBM zEnterprise EC12大型計算機處理器晶片的照片,有27.5億個電晶體,有六個核心(處理器),還有兩個標記為L3快取的大區域,由所有六個處理器共用,L3控制邏輯控制L3快取記憶體和核心之間以及L3快取記憶體與外部環境之間的流量。此外,在核心和L3快取之間還有儲存控制(SC)邏輯,記憶體控制器(MC)功能控制對晶片外部記憶體的存取,GX I/O匯流排控制存取I/O的通道介面卡的介面。下圖右則展示了單個核的內部結構,只是構成單個處理器晶片的矽表面區域的一部分。

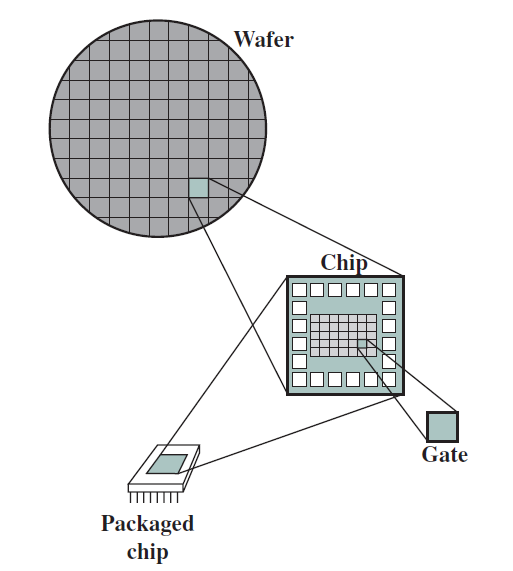

晶片(Wafer)、晶片(Chip)和門(Gate)之間的關係如下:

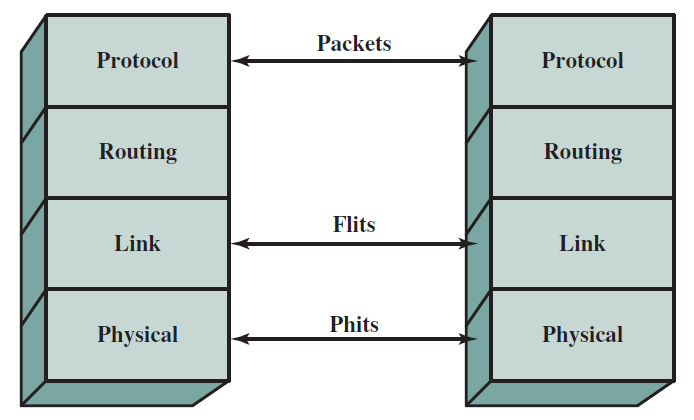

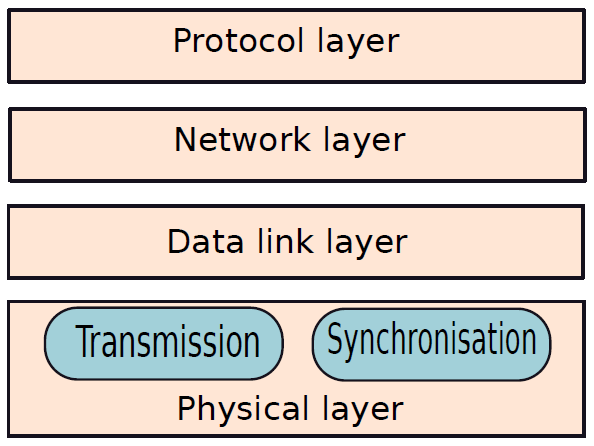

QPI(QuickPath Interconnect)是Intel於2008年推出的對等互連方法,QPI和其他對等互連方案的重要特徵是多個直接連線、分層協定架構和分組資料傳輸。

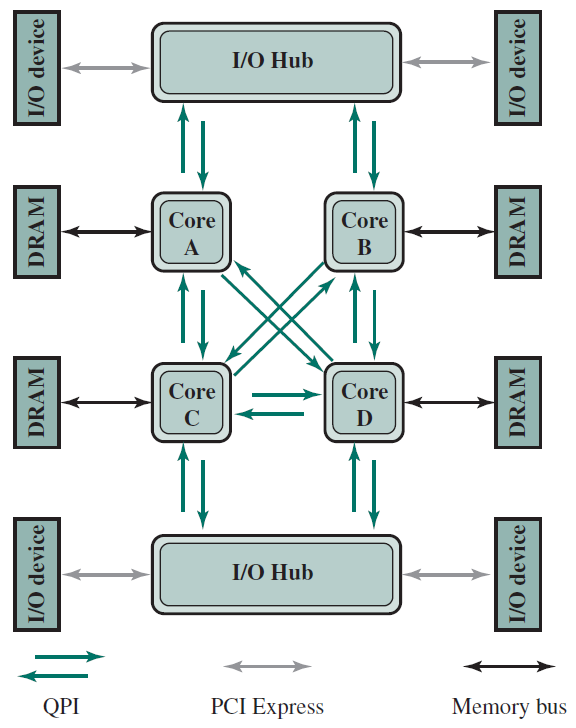

下圖說明了QPI在多核計算機上的典型使用。QPI鏈路(由圖中的綠色箭頭對錶示)形成了一個交換結構,使資料能夠在整個網路中移動,可以在每對核心處理器之間建立直接QPI連線。如果圖中的核心A需要存取核心D中的記憶體控制器,則它通過核心B或C傳送請求,後者必須將該請求轉發到核心D的記憶體控制器。同樣,具有八個或更多處理器的大型系統可以使用具有三個鏈路的處理器構建,並通過中間處理器路由流量。

使用QPI的多核設定。

QPI層示意圖。

不同的晶片組織。

多核組織備選方案。

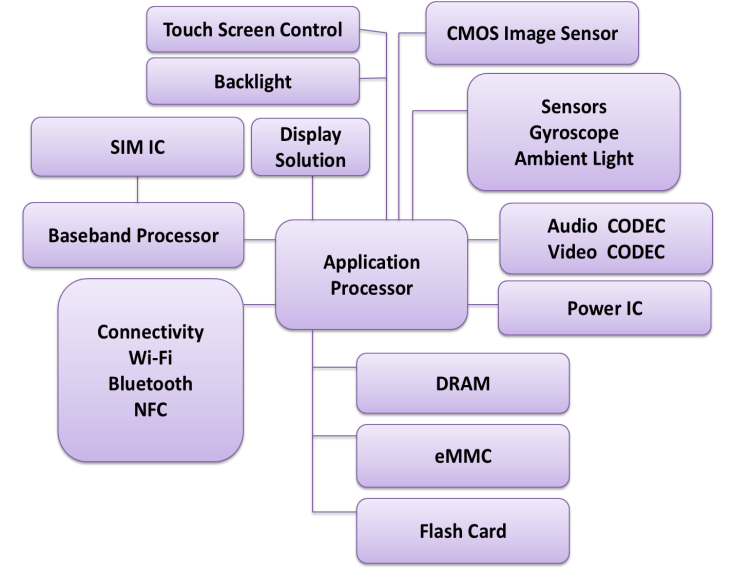

19.3.5 嵌入式系統

術語嵌入式系統是指在產品中使用電子裝置和軟體,而不是通用計算機,如平板電腦或桌上型電腦系統。每年售出數百萬臺電腦,包括筆記型電腦、個人電腦、工作站、伺服器、大型電腦和超級計算機,相比之下,每年生產數十億個嵌入大型裝置的計算機系統。如今,許多(也許是大多數)使用電力的裝置都有嵌入式計算系統,在不久的將來,幾乎所有這樣的裝置都將具有嵌入式計算系統。

具有嵌入式系統的裝置型別幾乎太多,無法列出,樣例包括手機、數碼相機、攝像機、計算器、微波爐、家庭安全系統、洗衣機、照明系統、恆溫器、印表機、各種汽車系統(如變速器控制、巡航控制、燃油噴射、防抱死制動和懸掛系統)、網球拍、牙刷以及自動化系統中的多種型別的感測器和致動器。

通常,嵌入式系統與其環境緊密耦合,導致與環境互動的需要所施加的實時約束。約束條件(如所需的運動速度、所需的測量精度和所需的持續時間)決定了軟體操作的時間,如果必須同時管理多個活動,會帶來更復雜的實時約束。

下圖概括地顯示了嵌入式系統組織,除了處理器和記憶體之外,還有許多元素與典型的桌上型電腦或筆記型電腦不同:

嵌入式系統的可能組織。

- 可能存在多種介面,使系統能夠測量、操作和以其他方式與外部環境互動。嵌入式系統通常通過感測器和致動器與外部世界互動(感知、操縱和通訊),因此通常是反應系統,反應系統與環境持續互動,並以該環境確定的速度執行。

- 人機介面可以像閃光燈一樣簡單,也可以像實時機器人視覺一樣複雜。在許多情況下,沒有人機介面。

- 診斷埠可用於診斷所控制的系統,而不僅僅用於診斷計算機。

- 可使用專用現場可程式化(FPGA)、專用(ASIC)或甚至非數位硬體來提高效能或可靠性。

- 軟體通常具有固定的功能,並且特定於應用程式。

- 效率對於嵌入式系統至關重要。需針對能量、程式碼尺寸、執行時間、重量、體積以及成本進行了優化。

與通用計算機系統也有幾個值得注意的相似之處:

- 即使使用名義上固定功能的軟體,現場升級以修復錯誤、提高安全性和新增功能的能力對於嵌入式系統來說也變得非常重要,而不僅僅是在消費類裝置中。

- 一個相對較新的發展是支援多種應用的嵌入式系統平臺,良好例子是智慧手機和音訊/視訊裝置(如智慧電視)。

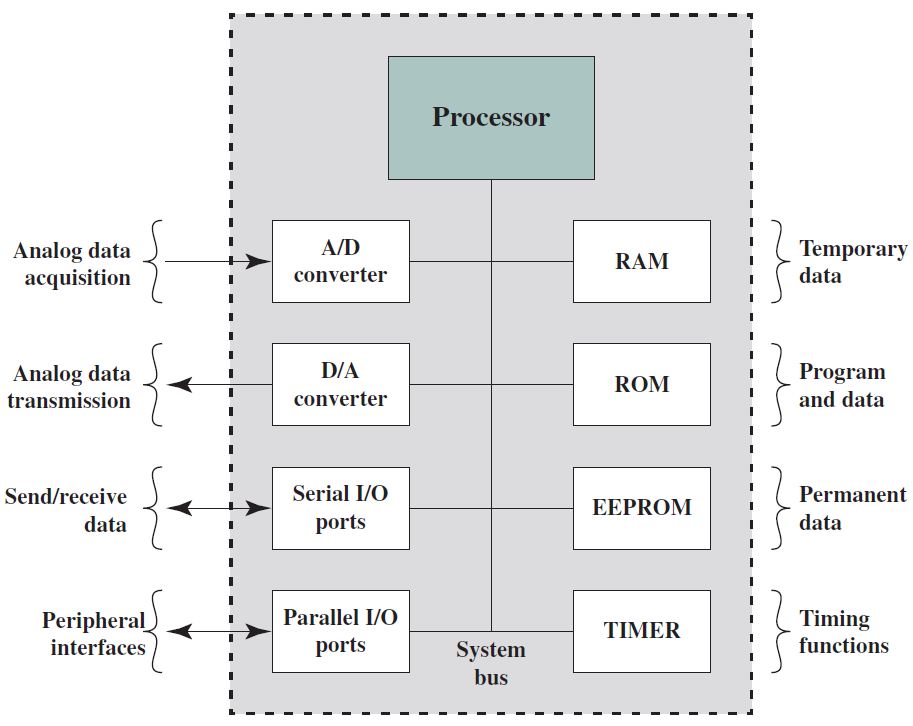

19.3.5.1 微處理器與微控制器

早期的微處理器晶片包括暫存器、ALU和某種控制單元或指令處理邏輯。隨著電晶體密度的增加,有可能增加指令集架構的複雜性,最終增加記憶體和多個處理器,現代微處理器晶片包括多個核心和大量的快取記憶體。

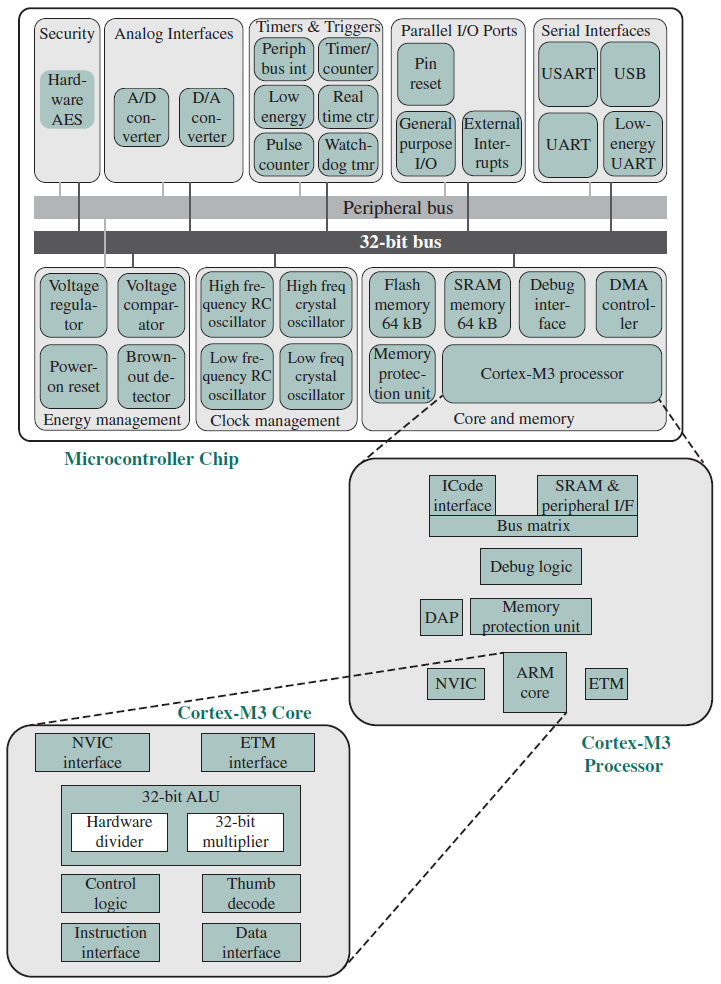

微控制器晶片對可用的邏輯空間進行了實質上不同的使用,下圖概括地顯示了微控制器晶片上常見的元件。微控制器是包含處理器、用於程式的非易失性記憶體(ROM)、用於輸入和輸出的易失性記憶體(RAM)、時鐘和I/O控制單元的單個晶片。微控制器的處理器部分具有比其他微處理器低得多的矽面積和高得多的能量效率。

也被稱為「晶片上的計算機」,每年數十億個微控制器單元被嵌入到從玩具到家電到汽車的各種產品中,比如單個車輛可以使用70個或更多個微控制器。通常,特別是對於更小、更便宜的微控制器,它們被用作特定任務的專用處理器,比如微控制器在自動化過程中被大量使用。通過提供對輸入的簡單反應,它們可以控制機器、開啟和關閉風扇、開啟和閉合閥門等,是現代工業技術的組成部分,是生產能夠處理極其複雜功能的機械的最廉價的方法之一。

微控制器具有多種物理尺寸和處理能力,處理器的範圍從4位元到32位元架構。微控制器往往比微處理器慢得多,通常工作在MHz範圍,而不是微處理器的GHz速度。微控制器的另一個典型特徵是它不提供人機互動,被程式設計用於特定任務,嵌入其裝置中,並在需要時執行。

19.3.5.2 嵌入式與深度嵌入式系統

嵌入式系統的一個子集,以及相當多的子集,被稱為深度嵌入式系統(Deeply embedded system)。儘管這個術語在技術和商業文獻中被廣泛使用,但你會在網際網路上無法明確地尋找一個直截了當的定義。通常,我們可以說,一個深度嵌入式系統有一個處理器,其行為很難被程式設計師和使用者觀察到。深度嵌入式系統使用微控制器而不是微處理器,一旦裝置的程式邏輯被燒錄到ROM(唯讀記憶體)中,就不可程式化,並且與使用者沒有互動。

深度嵌入式系統是專用的、單用途的裝置,可以檢測環境中的某些東西,執行基本級別的處理,然後對結果進行處理。深度嵌入式系統通常具有無線能力,並以聯網設定出現,例如部署在大面積(例如,工廠、農業領域)上的感測器網路,物聯網在很大程度上依賴於深度嵌入式系統。典型地,深度嵌入式系統在記憶體、處理器大小、時間和功耗方面具有極端的資源限制。

19.3.6 ARM架構

ARM架構是指從RISC設計原則演變而來的處理器架構,用於嵌入式系統。本節將簡述之。

ARM指令集是高度規則的,旨在高效實現處理器和高效執行。所有指令均為32位元長,遵循常規格式,使得ARM ISA適合在廣泛的產品上實現。

增強基本ARM ISA的是Thumb指令集,是ARM指令集的重新編碼子集。Thumb旨在提高使用16位元或更窄記憶體資料匯流排的ARM實現的效能,並允許比ARM指令集提供的程式碼密度更好的程式碼密度。Thumb指令集包含記錄為16位元指令的ARM 32位元指令集的子集。前些年定義的版本是Thumb-2。

ARM Holdings許可了許多專用微處理器和相關技術,但其產品線的大部分是Cortex系列微處理器架構。有三種Cortex架構,方便地用縮寫A、R和M標記。

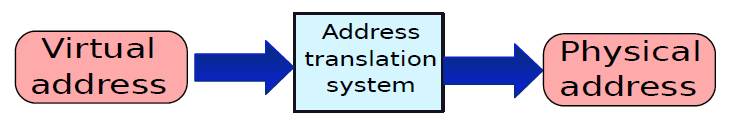

-

Cortex-A和Cortex-A50:是應用處理器,適用於智慧手機和電子書閱讀器等移動裝置,以及數位電視和家庭閘道器(如DSL和有線網際網路資料機)等消費裝置。這些處理器以更高的時脈頻率(超過1GHz)執行,並支援記憶體管理單元(MMU),是全功能作業系統(如Linux、Android、MS Windows和行動作業系統)所需的。MMU是通過將虛擬地址轉換為實體地址來支援虛擬記憶體和分頁的硬體模組。這兩種架構同時使用ARM和Thumb-2指令集,主要區別在於Cortex-A是32位元機器,而Cortex-A50是64位元機器。

-

Cortex-R:設計用於支援實時應用程式,其中需要通過對事件的快速響應來控制事件的定時。它們可以在相當高的時脈頻率(例如200MHz到800MHz)下執行,並且具有非常低的響應延遲。Cortex-R包括對指令集和處理器組織的增強,以支援深度嵌入式實時裝置。這些處理器中的大多數沒有MMU,有限的資料需求和有限數量的同時處理消除了對虛擬記憶體的複雜硬體和軟體支援的需求。Cortex-R確實具有專為工業應用設計的記憶體保護單元(MPU)、快取和其他記憶體功能。MPU是一種硬體模組,它禁止記憶體中的一個程式意外存取分配給另一個活動程式的記憶體。使用各種方法,在程式周圍建立一個保護邊界,並且禁止程式內的指令參照該邊界之外的資料。使用Cortex-R的嵌入式系統包括汽車制動系統、大容量儲存控制器、網路和列印裝置。

-

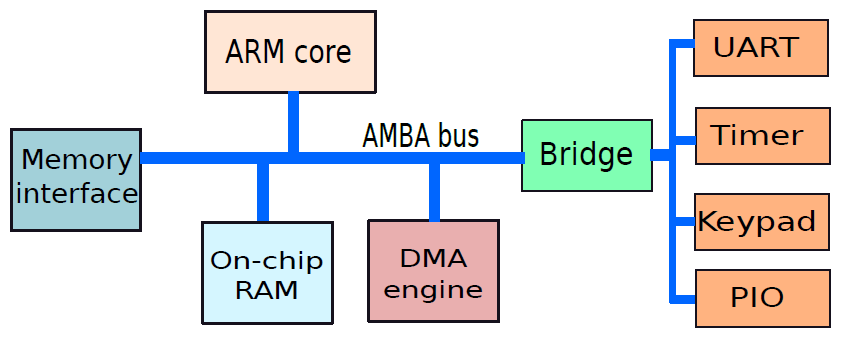

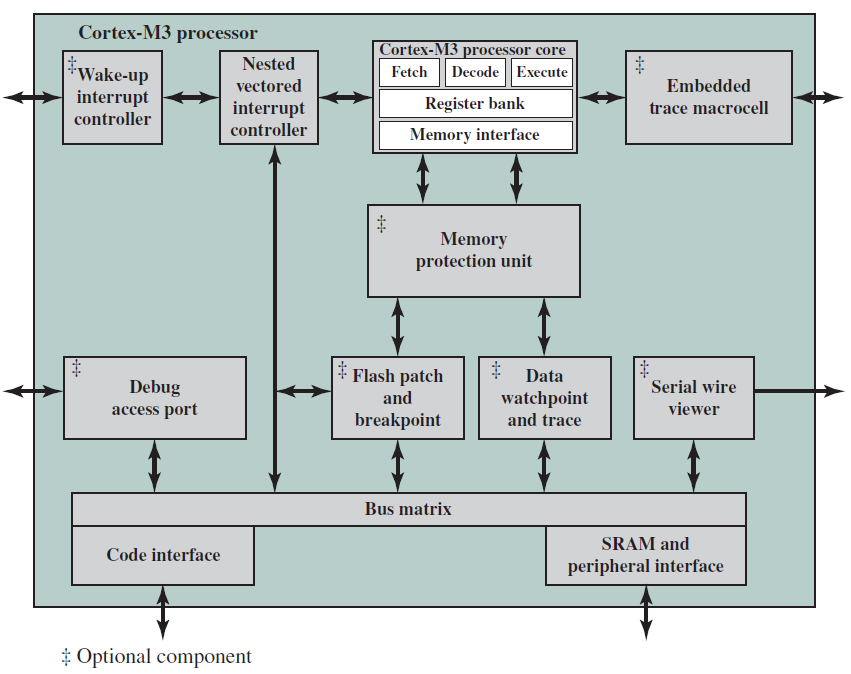

Cortex-M:主要是為微控制器領域開發的,在微控制器領域,快速、高確定性中斷管理的需求與極低門計數和最低可能功耗的需求相結合。與Cortex-R系列一樣,Cortex-M架構有一個MPU,但沒有MMU。Cortex-M僅使用Thumb-2指令集,其市場包括物聯網裝置、工廠和其他企業使用的無線感測器/致動器網路、汽車車身電子裝置等。Cortex-M系列包含Cortex-M0、Cortex-M0+、Cortex-M3、Cortex-M4等版本。下圖是基於Cortex-M3的典型微控制器晶片:

19.3.7 雲端計算

儘管雲端計算的一般概念可以追溯到20世紀50年代,但云端計算服務在2000年代初首次出現,尤其是針對大型企業。從那時起,雲端計算已經擴充套件到中小型企業,最近還擴充套件到了消費者。蘋果的iCloud於2012年推出,在推出一週內就擁有2000萬用戶,2008年推出的基於雲的筆記和歸檔服務Evernote在不到6年的時間內就接近了1億使用者。本節將簡要概述。

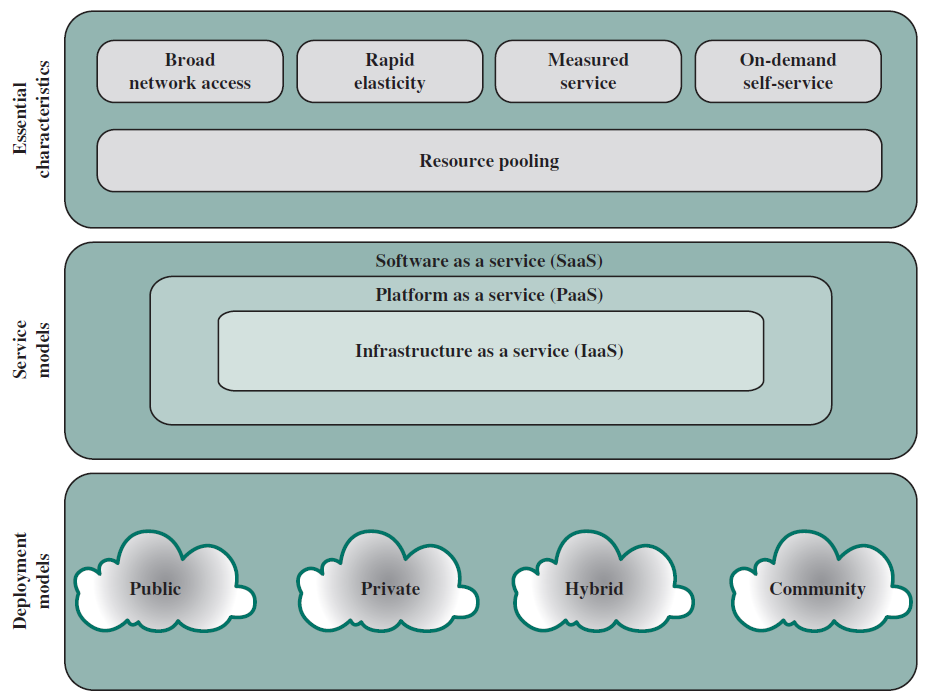

在許多組織中,越來越突出的趨勢是將大部分甚至所有資訊科技(IT)運營轉移到稱為企業雲端計算的網際網路連線基礎設施。與此同時,個人電腦和移動裝置的個人使用者越來越依賴雲端計算服務來備份資料、同步裝置和使用個人雲端計算進行共用。NIST在NIST SP-800-145(NIST雲端計算定義)中對雲端計算的定義如下:

雲端計算(Cloud computing):是一種模型,用於實現對可設定計算資源(例如,網路、伺服器、儲存、應用程式和服務)的共用池的無處不在、方便的按需網路存取,這些資源可以通過最小的管理工作量或服務提供商互動快速調配和釋出。

基本上,通過雲端計算,可以獲得規模經濟、專業網路管理和專業安全管理,這些功能對大小公司、政府機構以及個人電腦和移動使用者都有吸引力。個人或公司只需支付所需的儲存容量和服務費用,無論是公司還是個人,使用者都無需設定資料庫系統、獲取所需的硬體、進行維護和備份資料,所有這些都是雲服務的一部分。

理論上,使用雲端計算儲存資料並與其他人共用資料的另一大優勢是雲提供商負責安全。客戶並不總是受到保護,雲提供商之間出現了許多安全故障,例如Evernote在2013年初成為頭條新聞,當時它告訴所有使用者在發現入侵後重置密碼。

雲網路是指必須具備的網路和網路管理功能,以支援雲端計算。大多數雲端計算解決方案都依賴於網際網路,但這只是網路基礎設施的一部分。雲網路的一個範例是在提供商和訂戶之間提供高效能和/或高可靠性網路,在這種情況下,企業和雲之間的部分或全部流量繞過網際網路,使用雲服務提供商擁有或租用的專用專用網路設施。更一般地說,雲聯網是指存取雲所需的網路能力的集合,包括利用網際網路上的專門服務、將企業資料中心連結到雲,以及在關鍵點使用防火牆和其他網路安全裝置來強制執行存取安全政策。

我們可以將雲端儲存視為雲端計算的一個子集,本質上,雲端儲存由遠端託管在雲伺服器上的資料庫儲存和資料庫應用程式組成,使小型企業和個人使用者能夠利用可根據其需求擴充套件的資料儲存,並利用各種資料庫應用程式,而無需購買、維護和管理儲存資產。

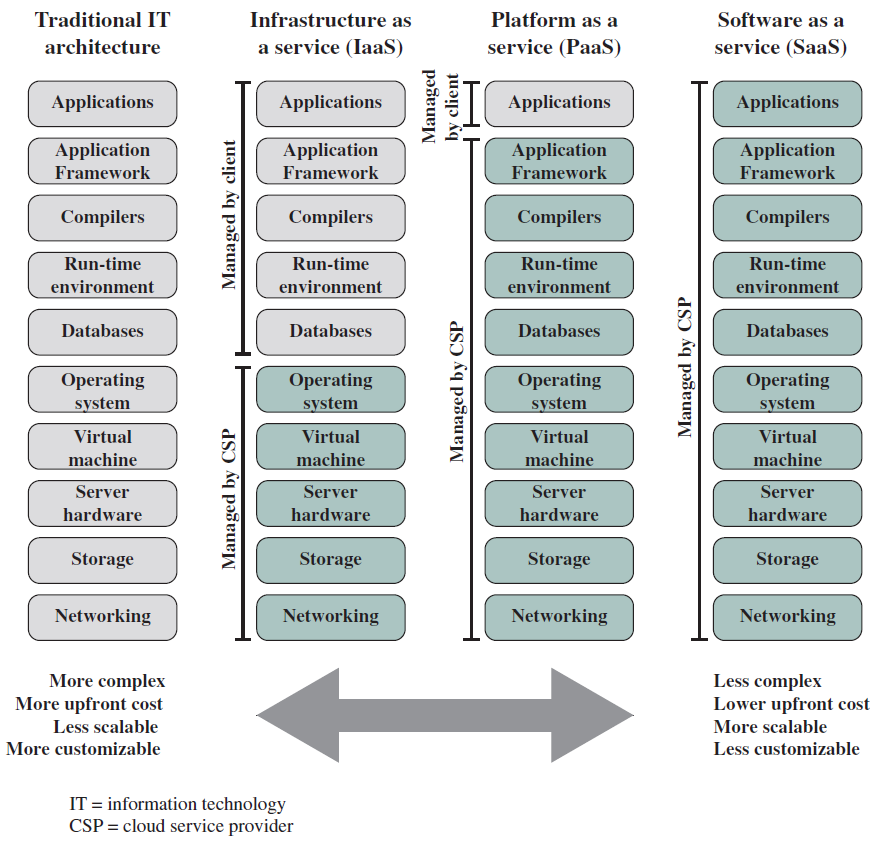

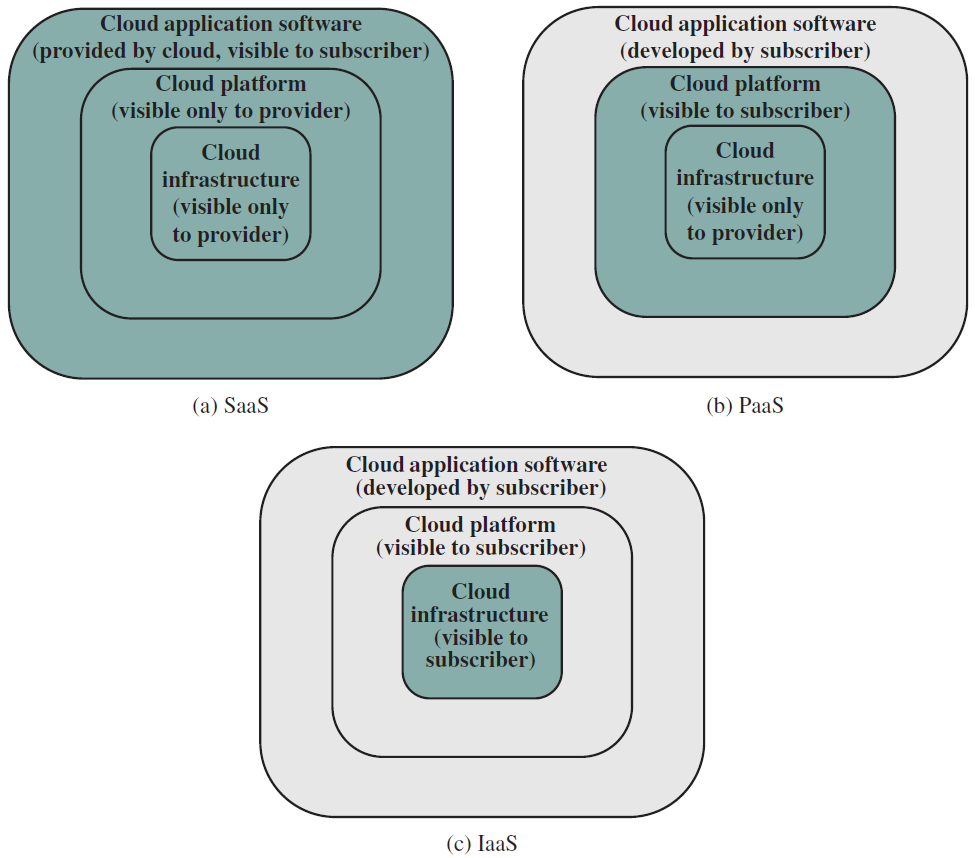

雲端計算的基本目的是提供方便的計算資源租賃,雲服務提供商(CSP)維護通過網際網路或專用網路可用的計算和資料儲存資源,客戶可以根據需要租用這些資源的一部分。實際上,所有云服務都是使用三種模型之一提供的(下圖):SaaS、PaaS和IaaS。

替代資訊科技架構。

雲端計算元素。

雲服務模型。

19.4 ISA

19.4.1 ISA定義

就像任何語言都有有限的單詞一樣,處理器可以支援的基本指令/基本命令的數量也必須是有限的,這組指令通常稱為指令集(instruction set),基本指令的一些範例是加法、減法、乘法、邏輯或和邏輯非。請注意,每條指令需要處理一組變數和常數,最後將結果儲存在變數中,這些變數不是程式設計師定義的變數,是計算機內的內部位置。我們將指令集架構定義為:

指令集架構(instruction set architecture,ISA)是處理器支援的所有指令的語意,包括指令本身及其運算元的語意,以及與外圍裝置的介面。

指令集架構是軟體感知硬體的方式,我們可以將其視為硬體輸出到外部世界的基本功能列表。Intel和AMD CPU使用x86指令集,IBM處理器使用PowerPC R指令集,HP處理器使用PA-RISC指令集,ARM處理器使用ARMR指令集(或其變體,如Thumb-1和Thumb-2)。因此,不可能在基於ARM的系統上執行為Intel系統編譯的二進位制檔案,因為指令集不相容,但在大多數情況下,可以重用C/C++程式。要在特定架構上執行C/C++程式,我們需要為該特定架構購買一個編譯器,然後適當地編譯C/C++程式。

19.4.2 基礎指令

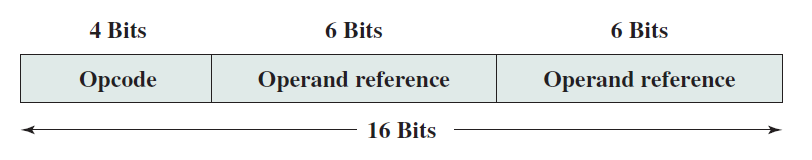

基本計算機具有16位元指令暫存器 (IR),可以表示記憶體參照或暫存器參照或輸入輸出指令。一種簡單的指令格式可以是如下形式:

基礎指令可分為以下幾類:

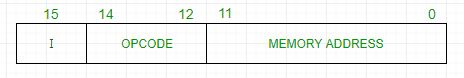

- 記憶體參照

這些指令將記憶體地址稱為運算元,另一個運算元總是累加器。下圖為直接和間接定址指定12位元地址、3位元運算碼(111除外)和1位定址模式。

範例:IR暫存器內容是0001XXXXXXXXXXXX,即ADD指令取指譯碼後發現是ADD操作的記憶體參照指令,因此:

DR ← M[AR]

AC ← AC + DR, SC ← 0

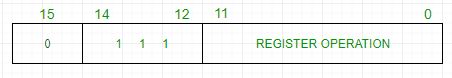

- 暫存器參照

這些指令對暫存器而不是記憶體地址執行操作。下圖的IR(14 – 12) 為 111(將其與記憶體參照區分開),IR(15) 為 0(將其與輸入/輸出指令區分開),其餘12位元指定暫存器操作。

範例:IR暫存器內容是0111001000000000,即CMA在取指和解碼週期後發現它是二補數累加器的暫存器參照指令,因此:

AC ← ~AC

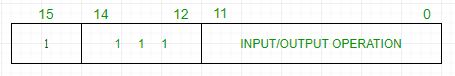

- 輸入/輸出

這些指令用於計算機和外部環境之間的通訊。下圖的IR(14 – 12) 為 111(將其與記憶體參照區分開來),IR(15) 為 1(將其與暫存器參照指令區分開),其餘 12 位指定 I/O 操作。

範例:IR暫存器內容是1111100000000000,即INP經過取指和解碼迴圈後發現它是用於輸入字元的輸入/輸出指令。因此,來自外圍裝置的INPUT字元。

包含在16位元IR暫存器中的指令集是:

- 算術、邏輯和移位指令(與、加、補、左迴圈、右迴圈等)。

- 將資訊移入和移出記憶體(儲存累加器,載入累加器)。

- 帶有狀態條件的程式控制指令(分支、跳過)。

- 輸入輸出指令(輸入字元、輸出字元)。

指令具體的描述如下表:

| 符號 | 16進位制碼 | 描述 |

|---|---|---|

| AND | 0xxx、8xxx | 與任意字到AC |

| ADD | 1xxx、9xxx | 累加任意字到AC |

| LDA | 2xxx、Axxx | 載入記憶體字到AC |

| STA | 3xxx、Bxxx | 儲存AC字到記憶體 |

| BUN | 4xxx、Cxxx | 無條件分支 |

| BSA | 5xxx、Dxxx | 分支並儲存返回地址 |

| ISZ | 6xxx、Exxx | 如果為0,則遞增並跳過 |

| CLA | 7800 | 清理AC |

| CLE | 7400 | 清除E(溢位位) |

| CMA | 7200 | 補充AC |

| CME | 7100 | 補充E |

| CIR | 7080 | 右迴圈AC和E |

| CIL | 7040 | 左迴圈AC和E |

| INC | 7020 | 遞增AC |

| SPA | 7010 | 如果AC>0,跳過下一條指令 |

| SNA | 7008 | 如果AC<0,跳過下一條指令 |

| SZA | 7004 | 如果AC=0,跳過下一條指令 |

| SZE | 7002 | 如果E=0,跳過下一條指令 |

| HLT | 7001 | 停止計算機 |

| INP | F800 | 輸入字元到AC |

| OUT | F400 | 輸出字元到AC |

| SKI | F200 | 跳過輸入標誌 |

| SKO | F100 | 跳過輸出標誌 |

| ION | F080 | 中斷開啟 |

| IOF | F040 | 中斷關閉 |

19.4.3 指令集設計準則

現在讓我們開始為處理器設計指令集的艱難過程,可以將指令集視為軟體和硬體之間的法律合同,雙方都需要履行各自的合同。軟體部分需要確保使用者編寫的所有程式都能成功有效地轉譯成基本指令,同樣,硬體需要確保指令集中的所有指令都是有效實現的。雙方都需要做出合理的假設,ISA需要具有一些必要的特性和一些有效性所需的特性。

-

完整。ISA應能夠實現所有使用者程式,是絕對必要的要求,我們希望ISA能夠代表使用者為其編寫的所有程式。例如,如果我們有一個ISA,只有一條ADD指令,那麼我們將無法減去兩個數位。為了實現迴圈,ISA應該有一些方法來一遍遍地重新執行同一段程式碼。如果沒有這種對和while迴圈的支援,C程式中的迴圈將無法運作。

請注意,對於通用處理器,我們正在檢視所有可能的程式。然而,許多用於嵌入式裝置的處理器功能有限,例如執行字串處理的簡單處理器不需要支援模擬點數(帶小數點的數位)。我們需要注意的是,不同的處理器被設計用於做不同的事情,因此它們的ISA可能不同。然而,底線是任何ISA都應該是完整的,因為它應該能夠用機器程式碼錶達使用者打算為其編寫的所有程式。

-

簡明。指令集的有限大小,最好不要有太多的指示。實現一條指令需要相當多的硬體,執行大量指令將不必要地增加處理器中電晶體的數量並增加其複雜性。因此,大多數指令集都有64到1000條指令。例如,MIPS指令集包含64條指令,而截至2012年,Intel x86指令集大約有1000條指令。請注意,對於ISA中的指令數量,1000條被認為是相當大的數位。

-

通用。指令應捕獲通用案例,程式中的大多數常見指令都是簡單的算術指令,如加法、減法、乘法、除法。最常見的邏輯指令是邏輯和、或、互斥或、和非。因此,為這些常見操作中的每一個指定一條指令是有意義的。

很少使用的計算的指令不是一個好主意。例如,實現計算\(\sin^{-1}(x)\)的指令可能沒有意義,可以提供使用現有的數學技術(如泰勒級數展開)實現的專用庫函數來計算\(\sin^{-1}(x)\)。由於大多數程式很少使用此函數,因此如果此函數執行時間相對較長,它們不會受到不利影響。

-

簡單。指令應該儘量簡單。假設有很多新增數位序列的程式,為了設計專門針對此類程式客製化的處理器,我們有幾個關於add指令的選項。我們可以實現一條將兩個數位相加的指令,也可以實現一個可以獲取運算元列表並生成列表和的指令。這裡的複雜性顯然存在差異,不能說哪種實現更快。前一種方法要求編譯器生成更多指令,但是,每個新增操作都執行得很快。後一種方法生成的指令數量更少,但是,每條指令執行的時間更長。前一種型別的ISA稱為精簡指令集(Reduced Instruction Set),後一種ISA稱為複雜指令集(Complex Instruction Set)。

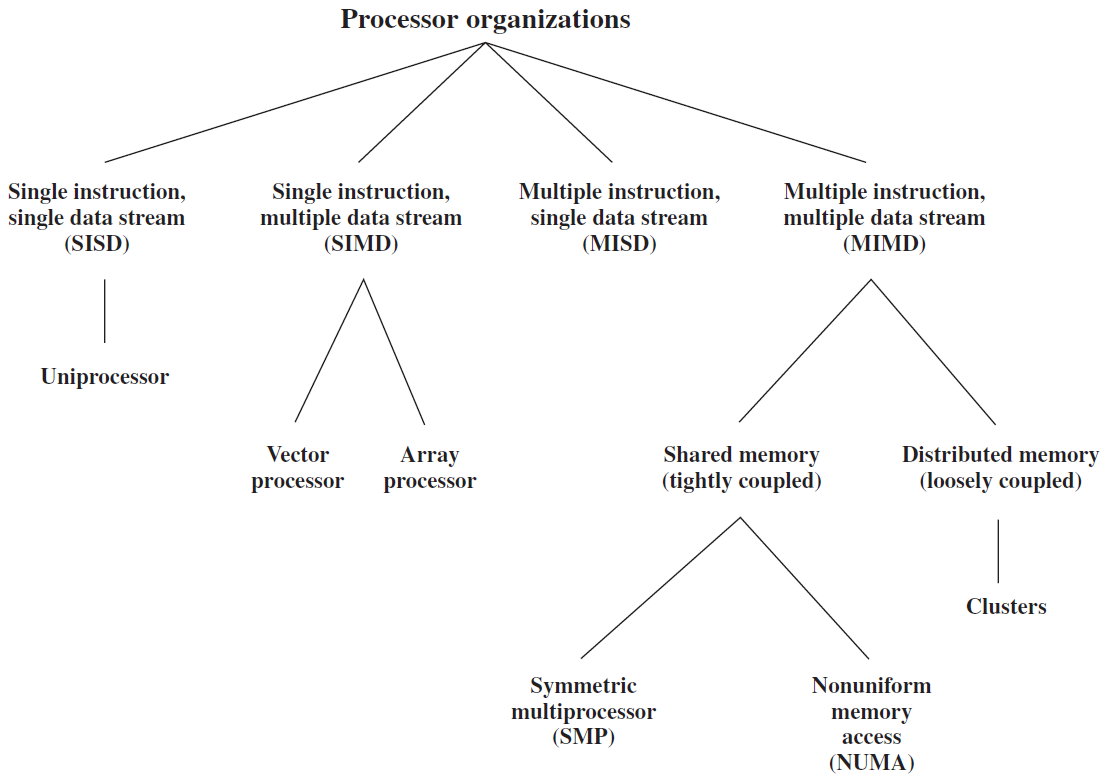

精簡指令集計算機(reduced instruction set computer,RISC)實現具有簡單規則結構的簡單指令,指令的數量通常很小(64到128)。範例:ARM、IBM PowerPC、HP PA-RISC。

複雜指令集計算機(complex instruction set computer,CISC)實現高度不規則的複雜指令,採用多個運算元,並實現複雜功能。其次,指令的數量很大(通常為500+)。範例:Intel x86、VAX。

直到90年代末,RISC與CISC的爭論一直是一個非常有爭議的問題。然而,從那時起,設計師、程式設計師和處理器供應商一直傾向於RISC設計風格,共識似乎是採用少量相對簡單的、具有規則結構和格式的指令。值得注意的是,這一點仍有爭議,因為CISC指令有時更適合某些型別的應用。現代處理器通常使用混合方法,其中既有簡單的指令,也有一些複雜的指令。然而,在底層,CISC指令被轉譯成RISC指令。因此,我們認為行業稍微偏向RISC指令,認為有簡單的指示是一種可取的特性。

ISA需要完整、簡潔、通用和簡單,且必須完整,而其餘屬性是可取的(但附有爭議)。

19.4.4 圖靈機和指令完整性

如何驗證ISA的完整性?這是一個非常有趣、困難且理論上深刻的問題。確定給定ISA對於給定程式集是否完整的問題是一個相當困難的問題,一般情況要有趣得多。我們需要回答這個問題:給定ISA,它能代表所有可能的程式嗎?

假設有一個ISA,其中包含基本的加法和乘法指令,我們能用這個ISA執行所有可能的程式嗎?答案是否定的,因為我們不能用現有的基本指令減去兩個數位。如果我們將減法指令新增到指令庫中,我們可以計算一個數的平方根嗎?即使我們可以,是否可以保證我們可以進行所有型別的計算?要回答這些令人煩惱的問題,我們需要首先設計一臺通用機器。

通用機器(universal machine)是可以執行任何程式的機器。

它是一臺可以執行所有程式的機器,可以把這臺機器的每一個基本動作都當作一條指令。通用機器的一組動作就是它的ISA,而這個ISA是完整的。當說ISA是完整的時,相當於說可以專門基於給定的ISA構建通用機器,可以通過解決通用機器的設計問題來解決ISA的完整性問題。它們是雙重問題,就通用機器而言,推理更容易。

20世紀初,電腦科學家開始思考通用機器的設計,他們想知道什麼是可計算的,什麼不是,以及不同類別機器的能力。其次,能夠計算所有可能程式結果的理論機器的形式是什麼?電腦科學的這些基本結果構成了當今現代電腦架構的基礎。

阿蘭·圖靈(Alan Turing)是第一個提出一種極其簡單和強大的通用機器的人,這臺機器恰如其分地以他的名字命名,被稱為圖靈機器(Turing machine)。這只是一個理論實體,通常用作數學推理工具,可以建立圖靈機的硬體實現,然而極為困難,並且需要不成比例的資源。儘管如此,圖靈機構成了當今計算機的基礎,而現代ISA是從圖靈機的基本動作中派生出來的。因此,非常有必要研究它的設計。

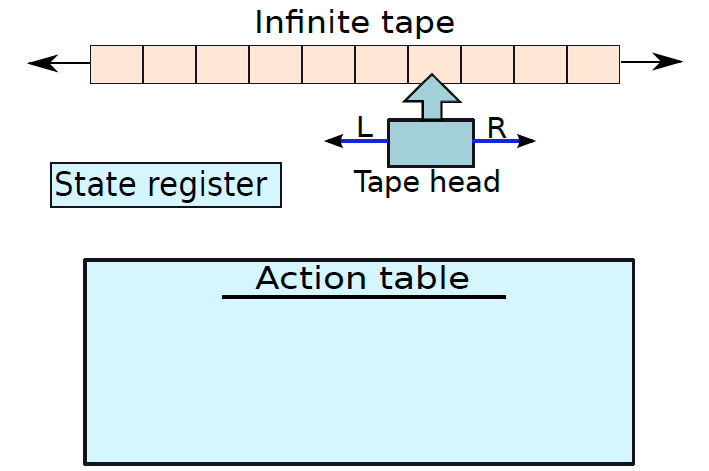

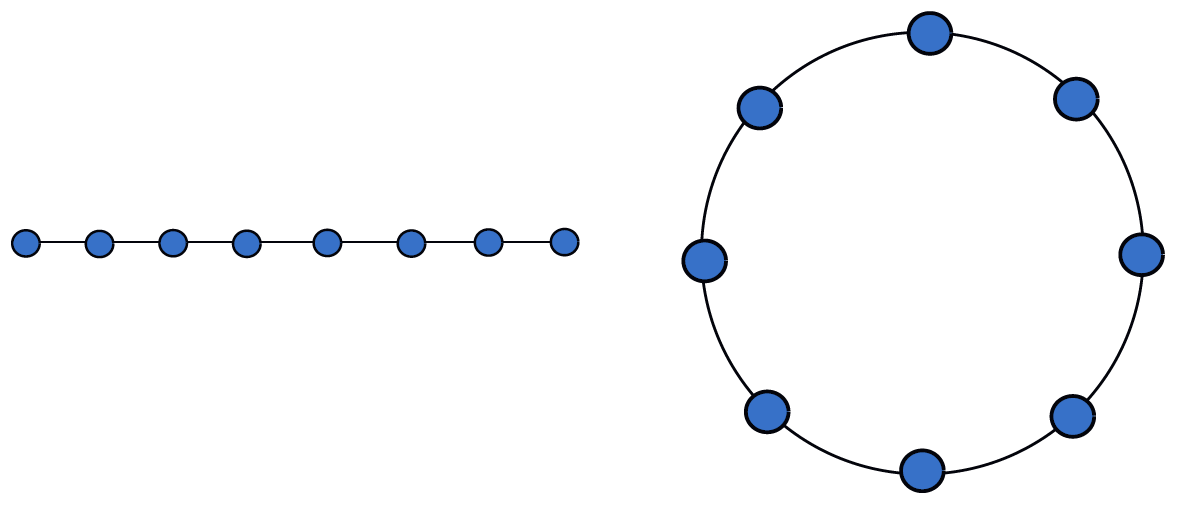

下圖顯示了圖靈機的一般結構,它包含一個內部磁帶,磁帶是一個單元陣列,每個單元格可以包含有限字母表中的符號,有一個特殊符號$用作特殊標記,一個專用的磁帶頭指向磁帶中的一個單元。在一組狀態中,有一小塊記憶體可以儲存當前狀態,該儲存元件稱為狀態暫存器。

圖靈機的操作非常簡單。在每一步中,磁帶頭從狀態暫存器中讀取當前單元中的符號及其當前狀態,並查詢一個表,該表包含每個符號和狀態組合的操作集,這個專用表稱為轉換函數表或動作表。這個表中的每個條目都說明了三件事——是否將磁帶頭向左或向右移動一步、下一個狀態及應寫入當前單元格的符號。因此,在每一步中,磁帶頭都可以覆蓋單元格的值,改變狀態暫存器中的狀態,並移動到新單元格。唯一的限制是新單元格必須位於當前單元格的最左邊或最右邊。形式上,它的格式為:

其中\(L\)代表左邊,\(R\)代表右邊。

範例:設計一個圖靈機來判斷字串的形式是否為aaa...abb...bb。答案:讓我們定義兩個狀態\(\left(S_{a}, S_{b}\right)\)和兩個特殊狀態——exit和error。如果狀態等於退出或錯誤,則計算停止。圖靈機可以開始從右向左掃描輸入,開始於狀態\((S_b)\)。動作表如下:

以上只是圖靈機的簡單應用案例,但實際場景中,複雜程度遠遠不止於此。我們可以立即得出結論,為即使是簡單的問題設計圖靈機也是不可能的。因為動作表會包含很多狀態,並且很快就會超出大小,但基線是可以用這個簡單的裝置解決複雜的問題。事實上,這臺機器可以解決各種問題,如天氣建模、金融計算和微分方程的求解!

Church-Turing論文捕捉到了這一觀察結果,該論文說,任何物理計算裝置都可以計算的所有函數都可以由圖靈機計算。用外行的話說,任何可以在人類已知的任何計算機上用確定性演演算法計算的程式,也可以用圖靈機計算。

這篇論文在過去的半個世紀裡一直堅定不移。到目前為止,研究人員還無法找到比圖靈機器更強大的機器,意味著沒有程式可以由圖靈機之外的另一種機器計算。有一些程式可能需要很長時間才能在圖靈機上進行計算,但它們也會佔用所有其他計算機上的無限時間。我們可以用所有可能的方式擴充套件圖靈機,可以考慮多個磁帶、多個磁帶頭或每個磁帶中的多個磁軌。可以看出,這些機器中的每一個都像一個簡單的圖靈機一樣強大。

上面描述的圖靈機不是通用機器,因為它包含一個動作表,該動作表特定於機器正在計算的函數。一個真正的通用機器將具有相同的動作表、符號以及每個功能的相同狀態集。如果我們能設計一個能模擬另一個圖靈機的圖靈機,我們就能製造一個通用圖靈機——通用且不會特定於正在計算的函數。

讓被模擬的圖靈機被稱為M,通用圖靈機則被稱為U。讓我們首先為M的動作表建立一個通用格式,並將其儲存在U磁帶上的指定位置,每個動作都需要5個引數——舊狀態、舊符號、方向(左或右)、新狀態、新符號。我們可以使用一組常見的基本符號,可以是10位十進位制數位(0-9),如果一個函數需要更多的符號,那麼我們可以考慮將一個符號包含在一組由特殊分隔符劃分的連續單元中。讓這樣的符號稱為模擬符號。同樣,模擬動作表中的狀態也可以編碼為十進位制數。對於方向,我們可以使用0表示左側,1表示右側。因此,單個動作表條目可能看起來像(@1334@34@0@1335@10@),其中「@」是分隔符,該條目表示,如果遇到符號34,我們將從狀態1334移動到1335。我們向左移動(0),並寫一個值10。因此,我們找到了一種對用於計算某個函數的圖靈機的動作表、符號集和狀態進行編碼的方法。

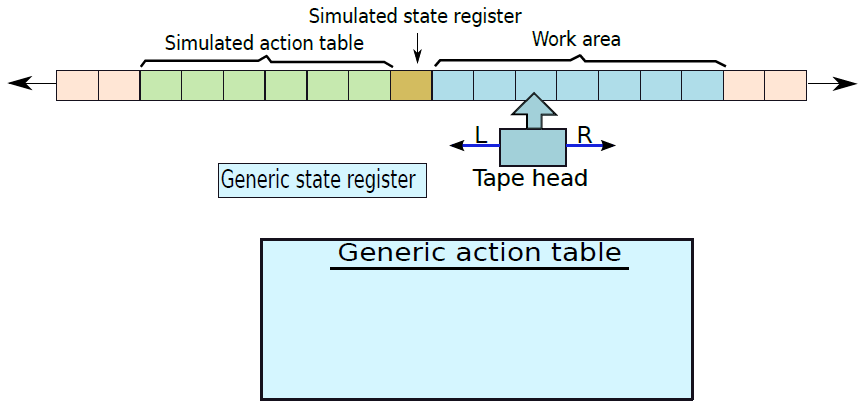

類似地,我們可以指定磁帶的一個區域來包含M的狀態暫存器,稱之為模擬狀態暫存器。讓M的磁帶在U的磁帶中有一個專用的空間,我們把這個空間稱為工作區(work area)。這種組織如下圖所示。

通用圖靈機的佈局。

磁帶因此分為三部分,第一部分包含模擬動作表,第二部分包含模擬狀態暫存器,最後一部分包含包含一組模擬符號的工作區。通用圖靈機(U)有一個非常簡單的動作表和一組狀態,其思想是在模擬動作表中查詢與模擬狀態暫存器中的值和磁帶頭下的模擬符號相匹配的正確條目。然後,通用圖靈機需要通過移動到新的模擬狀態來執行相應的動作,並在需要時覆蓋工作區中的模擬符號。為了做每一個基本動作,U需要做幾十次磁帶頭運動。然而,結論是我們可以構造一個通用的圖靈機。

可以構造一個通用的圖靈機,它可以模擬任何其他的圖靈機器。

自20世紀50年代以來,研究人員設計了更多型別的具有自己的狀態和規則集的假想機器,這些機器中的每一臺都已被證明至多與圖靈機一樣強大。所有機器和計算系統都有一個通用名稱,它們都像圖靈機一樣具有表達力和功能。這種系統可以說是圖靈完整的(Turing complete)。因此,任何通用機器和ISA都是圖靈完整的。

任何等同於圖靈機的計算系統都被稱為圖靈機。

因此,如果ISA是圖靈完整的,我們需要證明ISA是完整的或通用的。

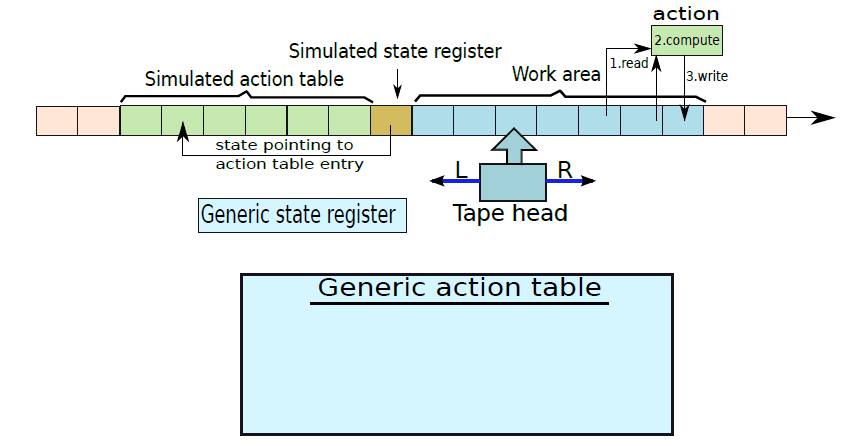

現在考慮一個更適合實際實現的通用圖靈機的變體(下圖),讓它具有以下特性。請注意,這樣的機器已經被證明是圖靈完整的。

一種改進的通用圖靈機

1、磁帶為半無限(semi-infinite,僅在一個方向上延伸至無限)。

2、模擬狀態是指向模擬動作表中的條目的指標。

3、每個狀態的模擬動作表中有一個唯一的條目。在查詢模擬動作表時,我們不關心磁帶頭下的符號。

4、一個動作指示磁帶頭存取工作區中的一組位置,並根據它們的值使用簡單的算術函數計算一個新值。它將此新值寫入工作區中的新位置。

5、預設的下一個狀態是動作表中的後續狀態。

6、如果磁帶上某個位置的符號小於某個值,動作也可以任意改變狀態,意味著模擬磁帶頭將開始從模擬動作表中的新區域提取動作。

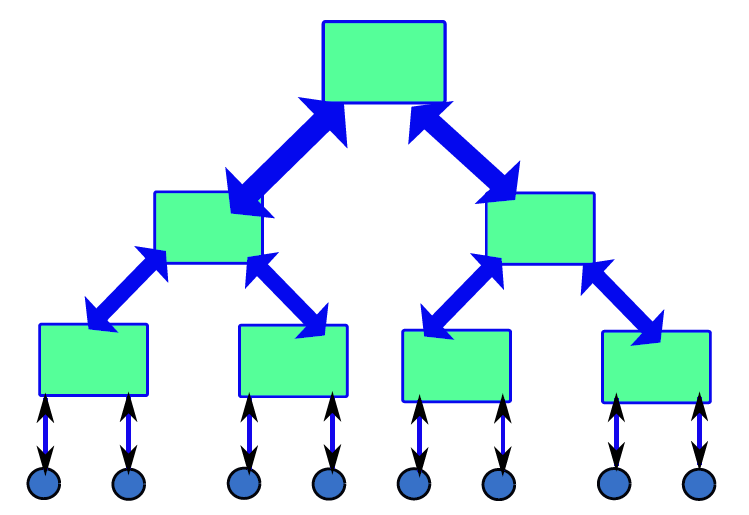

這臺圖靈機建議採用以下形式的機器組織。有大量指令(動作表),這個指令陣列通常被稱為程式。有一個狀態暫存器,用於維護指向陣列中當前指令的指標,稱為程式計數器,可以更改程式計數器以指向新指令。有一個大的工作區,可以儲存、檢索和修改符號,此工作區也稱為資料區。指令表(程式)和工作區(資料)儲存在我們改進的圖靈機的磁帶上。在實際的機器中,有限磁帶可被看作記憶體。記憶體是一個大的儲存單元陣列,其中儲存單元包含一個基本符號。記憶體的一部分包含程式,另一部分包含資料。

此外,每條指令都可以讀取記憶體中的一組位置,計算它們上的一個小算術函數,並將結果寫回記憶體,還可以根據記憶體中的值跳轉到任何其他指令。有一個專用單元來計算這些算術函數,寫入記憶體,並跳轉到其他指令,被稱為CPU(中央處理單元)。下圖顯示了該機器的概念組織。

基本指令處理器。

上面我們已經捕獲了圖靈機的所有方面:狀態轉換、磁帶頭的移動、重寫符號以及基於磁帶頭下符號的決策。這種機器與馮·諾依曼機器非常相似,後者構成了當今計算機的基礎。

現在,讓我們嘗試為改進的圖靈機設計一個ISA,有可能有一個只包含一條指令的完整ISA,考慮一個與改進的圖靈機相容並且已經被證明是圖靈完備的指令。

sbn a, b, c

sbn表示減法,如果為負數則分支,此指令從a中減去b(a和b是記憶體位置),將結果儲存在a中。如果a<0,則跳轉到指令表中位置c處的指令,否則,控制轉移到下一條指令。例如,我們可以使用此指令將儲存在位置a和b中的兩個數位相加。請注意,退出是程式末尾的一個特殊位置。

1: sbn temp, b, 2

2: sbn a, temp, exit

這裡假設記憶體位置temp已經包含值0。第一條指令將\(-b\)儲存在temp中,不管結果的值如何,它都跳到下一條指令。請注意,識別符號(數位:)是指令的序列號。在第二條指令中,計算\(a = a + b = a - (-b)\)。因此,成功地相加了兩個數位,現在可以使用這段基本程式碼將數位從1加到10。我們假設變數計數器初始化為9,索引初始化為10,一初始化為1,和初始化為0。

1: sbn temp, temp, 2 // temp = 0

2: sbn temp, index, 3 // temp = -1 * index

3: sbn sum, temp, 4 // sum += index

4: sbn index, one, 5 // index -= 1

5: sbn counter, one, exit // loop is finished, exit

6: sbn temp, temp, 7 // temp = 0

7: sbn temp, one, 1 // (0 - 1 < 0), hence goto 1

我們觀察到,這個小的操作序列執行for迴圈。退出條件在第5行,迴圈返回發生在第7行。在每一次迭代中,它都計算\(-sum += index\)。

有許多類似的單指令ISA已經被證明是完整的,例如,如果小於等於,則進行減法和分支,如果借用(borrow),則進行反向減法和跳過,以及具有通用記憶體移動操作的計算機。

用一條指令編寫一個程式是非常困難的,而且程式往往很長。沒有理由吝嗇指令的數量,通過考慮大量的指令,可以使複雜程式的實現變得更加輕鬆。讓我們嘗試將基本的sbn指令分解為幾個指令:

- 算術指令。可以有一組算術指令,如加法、減法、乘法和除法。

- 移動指令。可以有移動指令,在不同的記憶體位置移動值,允許將常數值載入到記憶體位置。

- 分支指令。需要根據計算結果或儲存在記憶體中的值來改變程式計數器以指向新指令的分支指令。

記住這些基本原則,我們可以設計許多不同型別的完整ISA。需要注意的是,我們只需要三種型別的指令:算術(資料處理)、移動(資料傳輸)和分支(控制)。

在任何指令集中,至少需要三種型別的指令:

1、需要算術指令來執行加法、減法、乘法和除法等運算。大多數指令集也有這類專門的指令來執行邏輯運算,如邏輯OR和NOT。

2、需要資料傳輸指令,可以在記憶體位置之間傳輸值,並可以將常數載入到記憶體位置。

3、需要能夠根據指令運算元的值在程式中的不同點開始執行指令的分支指令。

暫存器機(register machine)是指包含無限數量的命名儲存位置,這些儲存位置稱為暫存器。暫存器可以隨機存取,所有指令都使用暫存器名作為運算元。CPU存取暫存器,獲取運算元,然後處理它們。還存在混合機器,它們可以增加儲存空間帶有暫存器的標準Von Neumann機器。暫存器是可以儲存符號的儲存位置。

記憶體通常是非常大的結構,在現代處理器中,整個記憶體可以包含數十億個儲存位置,這種大小的記憶體的任何實際實現在實踐中都相當緩慢。硬體中有一個一般的經驗法則,大則慢,小則快。因此,為了實現快速操作,每個處理器都有一組可以快速存取的暫存器,暫存器的數量通常在8到64之間。算術和分支操作中的大多數運算元都存在於這些暫存器中,由於程式傾向於在任何時間點重複使用一小組變數,因此使用暫存器可以節省許多記憶體存取。然而,有時需要將記憶體位置引入暫存器或將暫存器中的值寫回記憶體位置。在這些情況下,我們使用專用的載入和儲存指令,在記憶體和暫存器之間傳輸值。大多數程式都有大多數純暫存器指令,載入和儲存指令的數量通常約為已執行指令總數的三分之一。

假設我們要將數位的3次方加到儲存位置b和c中,並將結果儲存在儲存位置a中。帶有暫存器的機器需要以下指令,假設r1、r2和r3是暫存器的名稱,沒有使用任何特定的(通用的、概念性的)ISA。

1: r1 = mem[b] // load b

2: r2 = mem[c] // load c

3: r3 = r1 * r1 // compute b^2

4: r4 = r1 * r3 // compute b^3

5: r5 = r2 * r2 // compute c^2

6: r6 = r2 * r5 // compute c^3

7: r7 = r4 + r6 // compute b^3 + c^3

4: mem[a] = r7 // save the result

mem是表示記憶體的陣列,需要首先將值載入到暫存器中,然後執行算術計算,然後將結果儲存回記憶體。上面的程式碼通過使用暫存器來節省記憶體存取,如果增加計算的複雜性,將節省更多的記憶體存取,因此,使用暫存器的執行速度會更快。最終的處理器組織如下圖所示。

很明顯,安排計算在堆疊上工作是不可取的,將有許多冗餘負載和儲存。儘管如此,對於打算計算長數學表示式的機器,以及程式大小是一個問題的機器,通常會選擇堆疊。很少有基於堆疊的機器的實際實現,如Burroughs Large Systems、UCSD Pascal和HP 3000(經典)。Java語言在編譯過程中假設一臺基於堆疊的機器,由於基於堆疊的機器很簡單,Java程式實際上可以在任何硬體平臺上執行。當我們執行編譯後的Java程式時,Java虛擬機器器(JVM)會動態地將Java程式轉換為另一個可以在帶有暫存器的機器上執行的程式。

基於累加器的機器使用一個暫存器,稱為累加器(accumulator)。每條指令都將單個記憶體位置作為輸入運算元,例如,加法運算將累加器中的值與記憶體地址中的值相加,然後將結果儲存回累加器。早期無法容納暫存器的機器曾經有累加器,累加器能夠減少記憶體存取的次數並加速程式。

累加器的某些方面已經滲透到英特爾x86處理器組中,這些處理器是2012年桌上型電腦和筆記型電腦最常用的處理器。對於大數的乘法和除法,這些處理器使用暫存器eax作為累加器。對於其他通用指令,任何暫存器都可以指定為累加器。

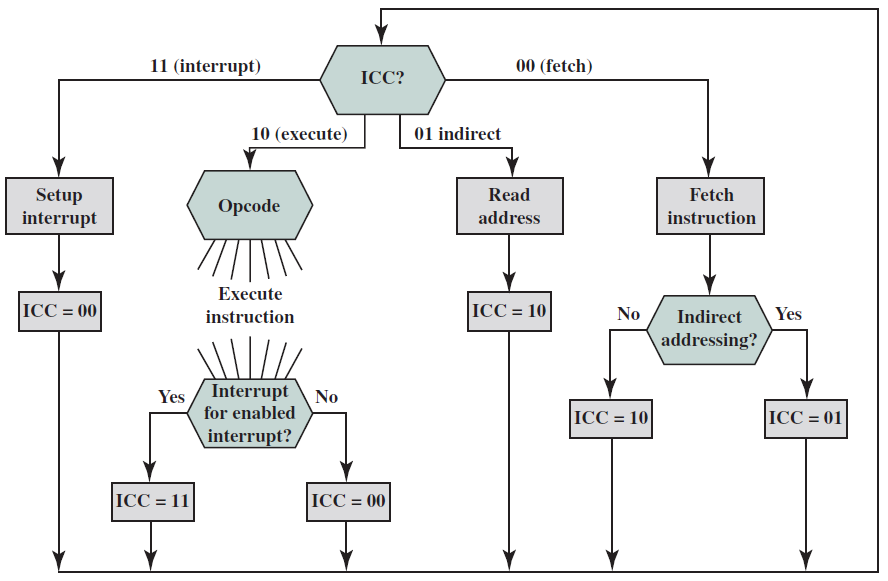

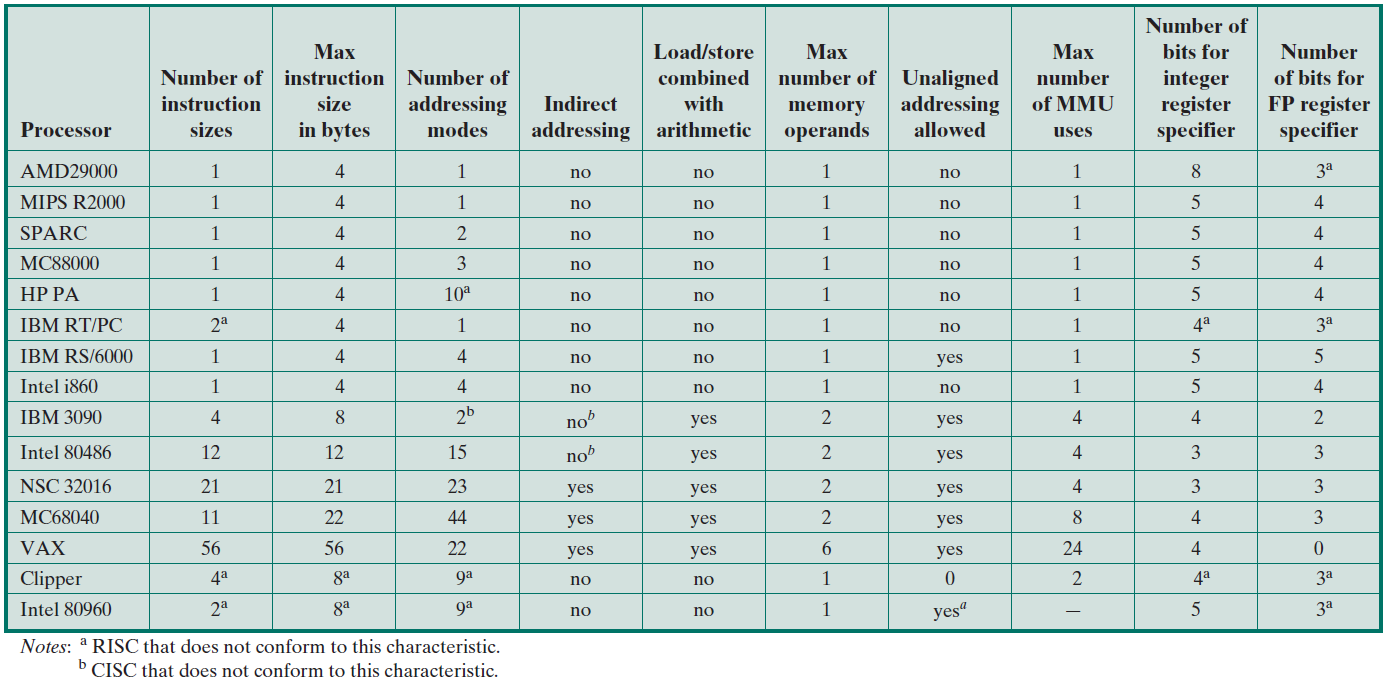

19.4.5 常見ISA

目前市面上流行的指令集包含ARM指令集和x86指令集。ARM是高階RISC機器(Advanced RISC Machines),是一家總部位於英國劍橋的標誌性公司,截至2012年,包括蘋果iPhone和iPad在內的大約90%的移動裝置都執行在基於ARM的處理器上。同樣,截至2012年超過90%的桌上型電腦和筆記型電腦執行在基於Intel或AMD的x86處理器上。ARM是RISC指令集,x86是CISC指令集。

還有許多其他為各種處理器量身客製化的指令集,移動計算機的另一個流行指令集是MIPS指令集,基於MIPS的處理器也用於汽車和工業電子中的各種處理器。

對於大型伺服器,通常使用IBM(PowerPC)、Sun(如今的Oracle,UltraSparc)或HP(PA-RISC)處理器。每個處理器系列都有自己的指令集,這些指令集通常是RISC指令集,大多數ISA共用簡單的指令,如加法、減法、乘法、移位和載入/儲存指令。除了這個簡單的集合,他們使用了大量更專業的指令。在ISA中選擇正確的指令集取決於處理器的目標市場、工作負載的性質以及許多設計時間限制,下表顯示了流行的指令集列表。

| ISA | 型別 | 年份 | 廠商 | 位數 | 位元組順序 | 暫存器數 |

|---|---|---|---|---|---|---|

| VAX | CISC | 1977 | DEC | 32 | little | 16 |

| SPARC | RISC | 1986 | Sun | 32 | bi | 32 |

| SPARC | RISC | 1993 | Sun | 64 | bi | 32 |

| PowerPC | RISC | 1992 | Apple, IBM, Motorola | 32 | bi | 32 |

| PowerPC | RISC | 2002 | Apple, IBM | 64 | bi | 32 |

| PA-RISC | RISC | 1986 | HP | 32 | big | 32 |

| PA-RISC | RISC | 1996 | HP | 64 | big | 32 |

| m68000 | CISC | 1979 | Motorola | 16 | big | 16 |

| m68000 | CISC | 1979 | Motorola | 32 | big | 16 |

| MIPS | RISC | 1981 | MIPS | 32 | bi | 32 |

| MIPS | RISC | 1999 | MIPS | 64 | bi | 32 |

| Alpha | RISC | 1992 | DEC | 64 | bi | 32 |

| x86 | CISC | 1978 | Intel, AMD | 16 | little | 8 |

| x86 | CISC | 1985 | Intel, AMD | 32 | little | 8 |

| x86 | CISC | 2003 | Intel, AMD | 64 | 64 little | 16 |

| ARM | RISC | 1985 | ARM | 32 | bi (little default) | 16 |

| ARM | RISC | 2011 | ARM | 64 | bi (little default) | 31 |

19.4.6 指令實現機制

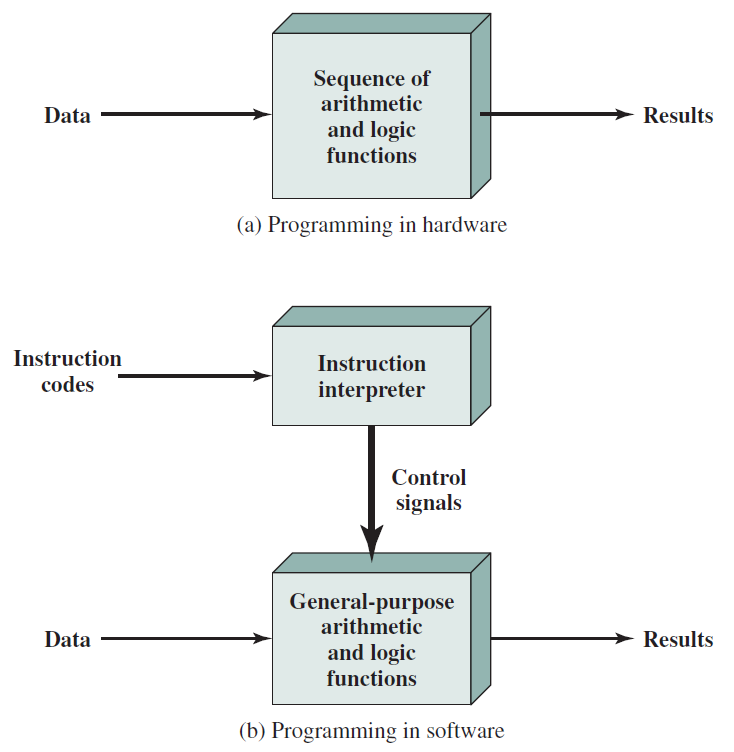

有一小組基本邏輯元件,可以以各種方式組合起來儲存二進位制資料,並對該資料執行算術和邏輯運算。如果要執行特定的計算,則可以構造專門為該計算設計的邏輯元件的設定。我們可以將以所需設定連線各種元件的過程視為程式設計的一種形式。生成的「程式」是硬體形式的,稱為硬連執行緒序(hardwired program)。

現在考慮這個替代方案。假設我們構造了算術和邏輯函數的通用設定,這組硬體將根據施加到硬體的控制訊號對資料執行各種功能。在客製化硬體的原始情況下,系統接受資料併產生結果(下圖a)。使用通用硬體,系統接受資料和控制訊號併產生結果,因此程式設計師只需要提供一組新的控制訊號,而不是為每個新程式重新佈線硬體。

硬體和軟體方法。

如何提供控制訊號?答案很簡單,但很微妙。整個程式實際上是一系列步驟,在每個步驟中,對一些資料執行一些算術或邏輯運算。對於每個步驟,都需要一組新的控制訊號。讓我們為每一組可能的控制訊號提供一個唯一的程式碼,並在通用硬體中新增一個可以接受程式碼並生成控制訊號的段(上圖b)。

程式設計現在更容易了。我們需要做的是提供一個新的程式碼序列,而不是為每個新程式重新佈線硬體。實際上,每個程式碼都是一條指令,部分硬體解釋每個指令並生成控制訊號。為了區分這種新的程式設計方法,一系列程式碼或指令被稱為軟體。

19.4.6.1 儲存指令

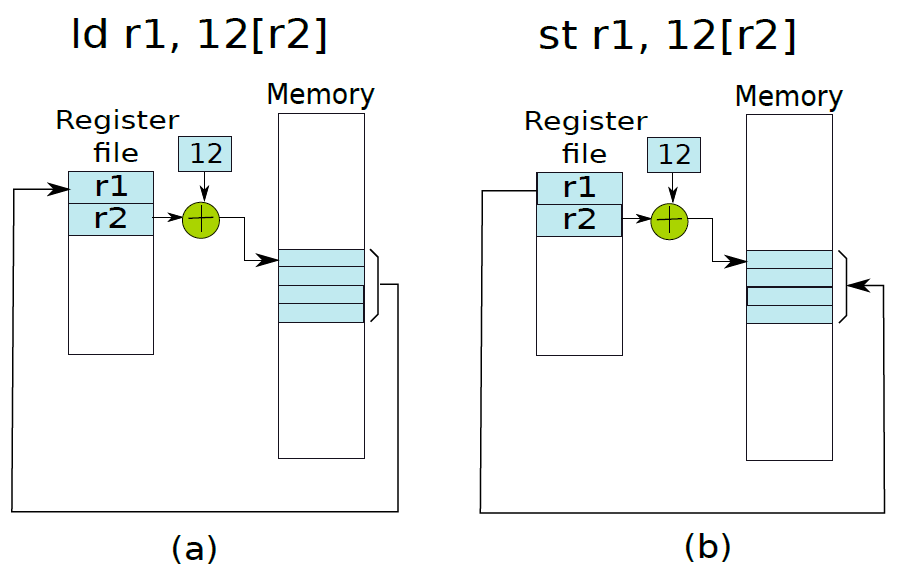

讓我們考慮載入指令:ld r1, 12[r2],此處將記憶體地址計算為r2和數位12的內容之和。ld指令存取此記憶體地址,獲取儲存的整數並將其儲存在r1中。假設計算的記憶體地址指向整數的第一個儲存位元組(即小端表示),所以記憶體地址包含LSB。詳情如下圖(a)所示。儲存操作則相反,將r1的值儲存到記憶體地址(r2+12)中,如下圖(b)所示。

19.4.6.2 函數

回顧一下實現一個簡單函數的基本要求。假設地址為A的指令呼叫函數foo,在執行函數foo之後,需要立即返回A處指令之後的指令,該指令的地址為A+4(如果我們假設A處的指令長度為4位元組)。這個過程被稱為從函數返回,地址(a+4)被稱為返回地址。

返回地址(Return address)是程序在執行函數後需要分支到的指令的地址。

因此,實現函數有兩個基本方面:1、呼叫或呼叫函數的過程;2、涉及從函數返回。

函數本質上是一塊組合程式碼,呼叫一個函數本質上是讓PC指向這段程式碼的開頭。我們可以將標籤與每個函數相關聯,標籤應該與函數中的第一條指令相關聯,呼叫函數就像分支到函數開頭的標籤一樣簡單。然而,這只是故事的一部分,我們還需要實現返回功能。因此,我們不能使用無條件分支指令來實現函數呼叫。

因此,讓我們提出一個專用的函數呼叫指令,它分支到函數的開頭,同時儲存函數需要返回的地址(稱為返回地址)。讓我們考慮下面的C程式碼,並假設每個C語句對應於一行組合程式碼。

a = foo(); /* Line 1 */

c = a + b; /* Line 2 */

在這個小程式碼片段中,我們使用函數呼叫指令來呼叫foo函數,返回地址是第2行中指令的地址。呼叫指令必須將返回地址儲存在專用儲存位置,以便以後可以檢索。大多數RISC指令集都有一個專用暫存器,稱為返回地址暫存器(不妨稱為ra),用於儲存返回地址,返回地址暫存器由函數呼叫指令自動填充。當我們需要從函數返回時,我們需要分支返回地址暫存器中包含的地址。

如果foo呼叫另一個函數會發生什麼?在這種情況下,ra中的值將被覆蓋。我們稍後將討論這個問題。現在讓我們考慮將引數傳遞給函數並返回返回值的問題。

假設函數foo呼叫函數foobar。foo被稱為呼叫者(caller),foobar被稱為被呼叫者(callee)。請注意,呼叫方與被呼叫方的關係是不固定的。foo可以呼叫foobar,foobar也可以在同一個程式中呼叫foo。根據哪個函數呼叫另一個函數來決定單個函數呼叫的呼叫者和被呼叫者。

呼叫者和被呼叫者都看到相同的暫存器檢視。因此,我們可以通過暫存器傳遞引數,同樣也可以通過暫存器來傳遞返回值。然而,正如我們在下面列舉的,在這個簡單的想法中有幾個問題(假設我們有16個暫存器)。

1、一個函數可以接受16個以上的引數,比我們現有的通用暫存器數量還要多,因此需要新增額外的空間來儲存引數。

2、函數可以返回大量資料,例如C中的大型結構。這段資料可能不可能在暫存器中儲存。

3、被呼叫者可能會覆蓋呼叫者將來可能需要的暫存器。

因此,我們觀察到,通過暫存器傳遞引數和返回值只適用於簡單的情況,不是一個非常靈活和通用的解決方案。儘管如此,我們的討論提出了兩個要求:

- 空間問題。我們需要額外的空間來傳送和返回更多的引數。

- 覆蓋問題。我們需要確保被呼叫方不會覆蓋呼叫方的暫存器。

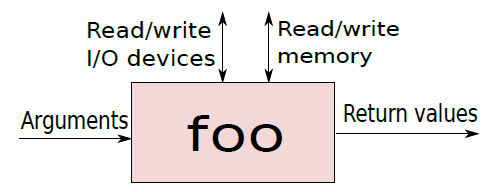

為了解決這兩個問題,需要更深入地瞭解函數是如何工作的。可以將函數foo想象成一個黑匣子,它接受一系列引數並返回一組值。要執行它的工作,foo可以花費一納秒、一週甚至一年的時間。foo可以呼叫其他函數來完成它的工作、將資料傳送到I/O裝置以及存取記憶體位置。下圖是函數foo的視覺化。

總而言之,通用函數處理引數,根據需要從記憶體和I/O裝置讀取和寫入值,然後返回結果。關於記憶體和I/O裝置,目前我們並不特別關心,有大量可用記憶體,空間不是主要限制,讀寫I/O裝置通常也與空間限制無關。主要問題是暫存器,因為它們供不應求。

讓我們先解決空間問題,可以通過暫存器和記憶體傳輸值。為了簡單起見,如果我們需要傳輸少量資料,我們可以使用暫存器,否則我們可以通過記憶體傳輸它們。類似地,對於返回值,我們可以通過記憶體傳輸值。如果我們使用記憶體傳輸資料,那麼我們不受空間限制。然而,這種方法缺乏靈活性,因為呼叫者和被呼叫者之間必須就要使用的記憶體位置達成嚴格的協定。請注意,我們不能使用一組固定的記憶體位置,因為被呼叫方可以遞迴呼叫自己。

void foobar()

{

...

foobar();

...

}

精明的讀者可能會認為,被呼叫方可以從記憶體中讀取引數並將其轉移到記憶體中的其他臨時區域,然後呼叫其他函數。然而,這種方法既不優雅,也不十分有效。稍後將研究更優雅的解決方案。

因此可以得出結論,我們已經部分解決了空間問題。如果需要在呼叫者和被呼叫者之間傳輸一些值,或者反之亦然,可以使用暫存器。但是,如果引數/返回值不在可用暫存器集中,那麼需要通過記憶體傳輸它們。對於通過記憶體傳輸資料,我們需要一個優雅的解決方案,它不需要呼叫者和被呼叫者之間就用於傳輸資料的記憶體位置達成嚴格的協定。

將暫存器儲存在記憶體中並隨後恢復的概念稱為暫存器溢位(register spilling)。

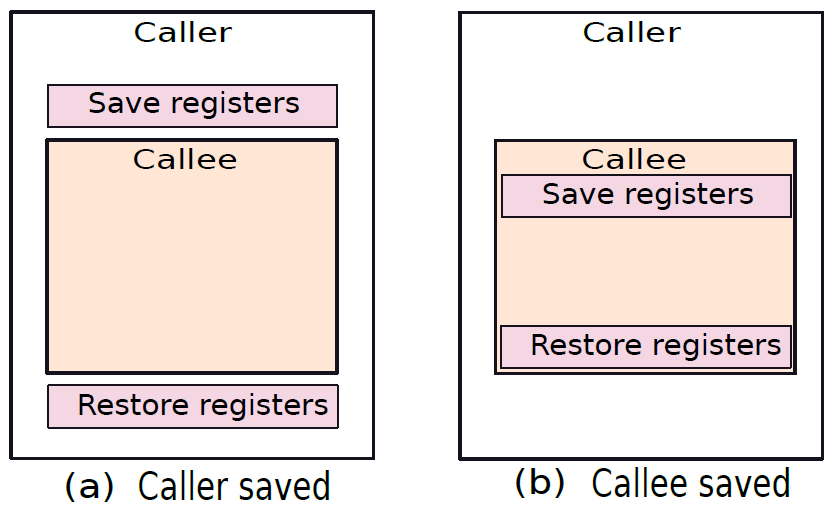

要解決覆蓋問題,有兩種解決方案:1、呼叫者可以將所需的暫存器集儲存在記憶體中的專用位置,可以在被呼叫方完成後檢索其暫存器集,並將控制權返回給呼叫方。2、讓被呼叫方儲存和恢復它需要的暫存器。這兩種方法都如下圖所示。這種將暫存器值儲存在記憶體中,然後再檢索的方法稱為溢位。

呼叫方儲存和被呼叫方儲存的暫存器。

我們又遇到了同樣的問題,即呼叫者和被呼叫者都需要就需要使用的記憶體位置達成嚴格的協定。現在讓我們一起努力解決這兩個問題。

我們簡化了向函數傳遞引數和從函數傳遞引數,以及使用記憶體中的專用位置儲存/恢復暫存器的過程。然而,該解決方案被發現是靈活的,對於大型現實世界程式來說,實現起來可能相當複雜。為了簡化這個想法,讓我們在函數呼叫中定義一個模式。

典型的C或Java程式從主函數開始。然後,該函數呼叫其他函數,這些函數可能反過來呼叫其他函數。最後,當主函數退出時,執行終止。每個函數定義一組區域性變數,並對這些變數和函數引數執行計算,它還可以呼叫其他函數。最後,函數返回一個值,很少返回一組值(C中的結構)。請注意,函數終止後,不再需要區域性變數和引數。因此,如果其中一些變數或引數儲存在記憶體中,我們需要回收空間。其次,如果函數溢位了暫存器,那麼這些記憶體位置也需要在它退出後釋放。最後,如果被呼叫方呼叫另一個函數,則需要將返回地址暫存器的值儲存在記憶體中,還需要在函數退出後釋放此位置。

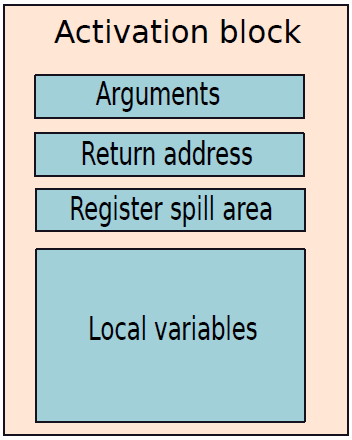

最好將所有這些資訊連續儲存在一個記憶體區域中,被稱為函數的啟用塊(activation block),下圖顯示了啟用塊的記憶體對映。

啟用塊包含引數、返回地址、暫存器溢位區(對於呼叫方儲存和被呼叫方儲存的方案)和區域性變數。一旦函數終止,就可以完全擺脫啟用塊。一個函數如果想要返回一些值,那麼可以使用暫存器這樣做,但是它如果想要返回一個大的結構,那麼就可以將其寫入呼叫方的啟用塊中,呼叫方可以在其啟用塊中提供一個可以寫入該資料的位置。後面有可能更優雅地做到這一點,在解釋如何做到這一點之前,需要了解如何在記憶體中安排啟用塊。

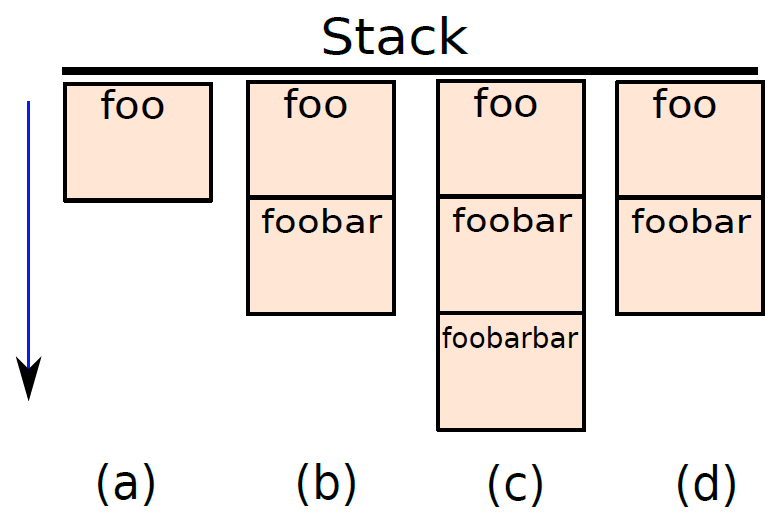

我們可以有一個儲存區域,其中所有的啟用塊都儲存在相鄰的區域中。考慮一個例子,假設函數foo呼叫函數foobar,foobar又呼叫foobarbar。下圖顯示了4個記憶體狀態:(a)在呼叫foobar之前,(b)在呼叫foobarbar之前,(c)在呼叫foobarbar之後,(d)在foobarar返回之後。

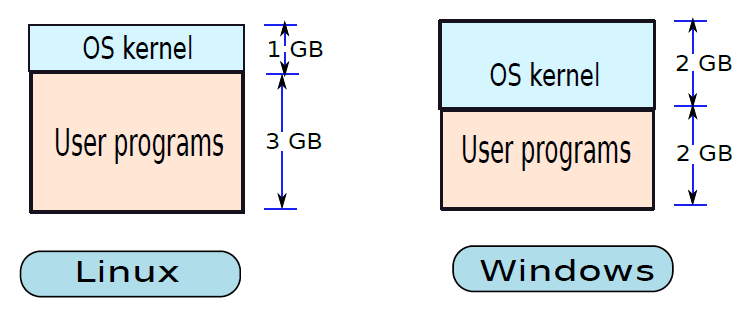

在這個記憶體區域中有一個後進先出的行為,最後呼叫的函數是要完成的第一個函數,這種後進先出的結構傳統上被稱為電腦科學中的堆疊(stack),因此專用於儲存啟用塊的儲存區域稱為堆疊。傳統上,堆疊被認為是向下增長的(向更小的記憶體地址增長),意味著主功能的啟用塊從非常高的位置開始,新的啟用塊被新增到現有啟用塊的正下方(朝向較低的地址)。堆疊的頂部實際上是堆疊中最小的地址,而堆疊的底部是最大的地址。堆疊的頂部表示當前正在執行的函數的啟用塊,堆疊的底部表示初始主函數。

堆疊(stack)是儲存程式中所有啟用塊的記憶體區域,一般情況是向下增長的。在呼叫函數之前,我們需要將其啟用塊推播到堆疊中,當函數完成執行時,需要將其啟用塊彈出到堆疊中。

堆疊指標暫存器(stack pointer register)儲存指向堆疊頂部的指標。

大多數架構將指向堆疊頂部的指標儲存在一個稱為堆疊指標的專用暫存器中,常被稱為sp。請注意,對於許多架構,堆疊是純軟體結構。對於他們來說,硬體不知道堆疊。但對於某些架構(如x86),硬體知道堆疊並使用它來推播返回地址或其他暫存器的值。即使在這種情況下,硬體也不知道每個啟用塊的內容,結構由程式集程式設計師或編譯器決定。在所有情況下,編譯器都需要顯式新增組合指令來管理堆疊。

為被呼叫方建立新的啟用塊涉及以下步驟。

1、將堆疊指標減小啟用塊的大小。

2、複製引數的值。

3、如果需要,通過寫入相應的記憶體位置來初始化任何區域性變數。

4、如果需要,溢位任何暫存器(儲存到啟用塊)。

從函數返回時,必須銷燬啟用塊,可以通過將啟用塊的大小新增到堆疊指標來完成。

通過使用堆疊,我們解決了所有問題。呼叫方和被呼叫方不能覆蓋彼此的區域性變數,區域性變數儲存在啟用塊中,兩個啟用塊不重疊。除了變數之外,還可以通過在啟用塊中顯式插入儲存暫存器的指令來阻止被呼叫方重寫呼叫方的暫存器。實現這一點有兩種方法:呼叫者儲存的方案和被呼叫方儲存的方案。其次,無需就將用於傳遞引數的記憶體區域達成明確協定,堆疊可以用於此目的,呼叫者可以簡單地將引數推播到堆疊上,這些引數將被推播到被呼叫方的啟用塊中,被呼叫方可以輕鬆使用它們。同樣,當從函數,被呼叫方可以通過堆疊傳遞返回值,需要先通過減少堆疊指標來銷燬其啟用塊,然後才能將返回值推播到堆疊上。呼叫方將知道被呼叫方的語意,因此在被呼叫方返回後,可以假定其啟用塊已被被呼叫方有效地放大,返回值佔用了額外的空間。

ARM使用B/BL/BX/BLX等語句呼叫函數和返回函數,而x86使用call等指令呼叫函數,此外,x86和ARM都可使用ret指令返回地址。下面是ARM的函數呼叫範例程式碼:

.globl main

.extern abs

.extern printf

.text

output_str:

.ascii "The answer is %d\n\0"

@ returns abs(z)+x+y

@ r0 = x, r1 = y, r2 = z

.align 4

do_something:

push {r4, lr}

add r4, r0, r1

mov r0, r2

bl abs ; 呼叫abs

add r0, r4, r0

pop {r4, pc}

main:

push {ip, lr}

mov r0, #1

mov r1, #3

mov r2, #-4

bl do_something ; 呼叫do_something

mov r1, r0

ldr r0, =output_str

bl printf

mov r0, #0

pop {ip, pc}

有趣的指令是pushpop和bl,只需獲取提供的暫存器列表並將其推到堆疊上,或者將其彈出並放入提供的暫存器中。bl只不過是帶連結的分支,分支後的下一條指令的地址被載入到連結暫存器lr中。

一旦我們正在呼叫的例程被執行,lr就可以被複制回pc,將使CPU能夠在bl指令之後從程式碼中繼續。在do_someting中,我們將連結暫存器推播到堆疊,這樣就可以再次將其彈出返回,即使對abs的呼叫將覆蓋連結暫存器的原始內容。程式儲存r4,因為Arm過程呼叫標準規定在函數呼叫之間必須保留r4-r11(下圖),並且被呼叫的函數負責該保留,意味著do_someting需要將r0+r1的結果儲存在一個不會被abs破壞的暫存器中,並且我們還必須儲存用於儲存該結果的任何暫存器的內容。當然,在這種特殊情況下,我們可以只使用r3,但是需要考慮的。我們推播並彈出暫存器,儘管我們不必保留它,因為過程呼叫標準要求堆疊64位元對齊。這在使用堆疊操作時提供了效能優勢,因為它們可以利用CPU內的64位元資料路徑。

我們可以直接壓入高地址的值,畢竟如果abs需要註冊,那麼這就是它儲存值的方式。推播r4而不是我們知道需要的值有一個小的效能問題,但最有力的論點可能是,在函數的開始和結束時只推播/彈出所需的任何暫存器,就可以減少錯誤發生的可能性,提高程式碼的可讀性。此外,「main」函數還壓入和彈出lr的內容,因為雖然主程式碼可能是我的程式碼中要執行的第一件事,但它不是載入程式時要執行的第二件事。編譯器將在呼叫main之前插入對一些基本設定函數的呼叫,並在退出時進行一些最終清理呼叫。

現在讓我們嘗試將每條指令編碼為32位元值。假設有0、1、2和3地址格式的指令,其次,有些指令採用即時值,因此需要將32位元劃分為多個欄位。假設有21條指令,則需要5位來編碼指令型別,常規指令中的每個指令的程式碼如下表所示。我們可以使用32位元欄位中最重要的位來指定指令型別,指令的程式碼也稱為操作碼(opcode)。

| 指令 | 二進位制碼 |

|---|---|

| add | 00000 |

| sub | 00001 |

| mul | 00010 |

| div | 00011 |

| mod | 00100 |

| cmp | 00101 |

| and | 00110 |

| or | 00111 |

| not | 01000 |

| mov | 01001 |

| lsl | 01010 |

| lsr | 01011 |

| asr | 01100 |

| nop | 01101 |

| ld | 01110 |

| st | 01111 |

| beq | 10000 |

| bgt | 10001 |

| b | 10010 |

| call | 10011 |

| ret | 10100 |

現在,讓我們嘗試從0地址指令開始對每種型別的指令進行編碼。

我們擁有的兩條0地址指令是ret和nop。操作碼由五個最重要的位指定,在這種情況下,ret等於10100,b等於10010(參見上表)。它們的編碼如下圖所示,我們只需要在MSB位置指定5位元運算碼,其餘27位不需要。

編碼ret指令。

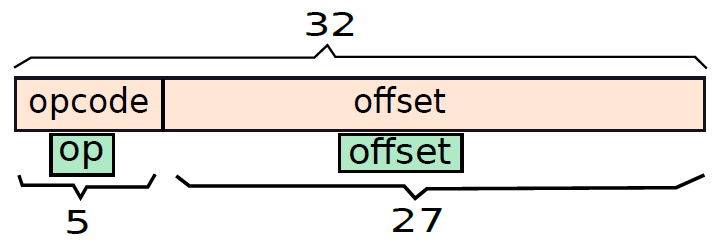

我們擁有的1地址指令是call、b、beq和bgt,它們將標籤作為引數。在編碼指令時,我們需要指定標籤的地址作為引數,標籤的地址與它所指向的指令的地址相同。如果標籤後的行為空,那麼我們需要考慮下一條包含指令的組合語句。

這四條指令的操作碼需要5位,剩餘的27位可用於地址。請注意,記憶體地址是32位元長,不能用27位覆蓋地址空間,但可以進行兩個關鍵的優化。首先,可以假設PC相對定址,可以假設27位指定了相對於當前PC的偏移量(正負)。現代程式中的分支語句是因為for/while迴圈或if語句而生成的,對於這些構造,分支目標通常在幾百條指令的範圍內。如果有27位來指定偏移量,並且假設它是2的二補數,那麼任何方向(正或負)的最大偏移量都是226,對於幾乎所有的程式來說已足夠。

還有另一個重要的觀察。一條指令需要4個位元組。如果假設所有指令都與4位元組邊界對齊,那麼指令的所有起始記憶體地址都將是4的倍數,因此地址的至少兩個有符號二進位制數位將是00,沒有理由在試圖指定它們時浪費位元,可以假設27位指定包含指令的記憶體字(以4位元組記憶體字為單位)地址的偏移量。通過這種優化,從PC的位元組偏移量變為29位,即使是最大的程式,這個數位也應該足夠。以防萬一有極端的例子,其中分支目標距離超過228個位元組,那麼組合程式需要將分支連結起來,這樣一個分支將呼叫另一個分支,以此類推。這些指令的編碼如下圖所示。

1地址指令的編碼(分支格式)。

請注意,1地址指令格式禁止使用0地址格式中未使用的位,可以將ret指令的0地址格式視為1地址格式的特例,1地址格式稱為分支格式。以這種格式命名欄位,將格式的操作碼部分稱為op,將偏移量稱為offset。操作欄位包含位置28-32的位,偏移欄位包含位置1-27的位。

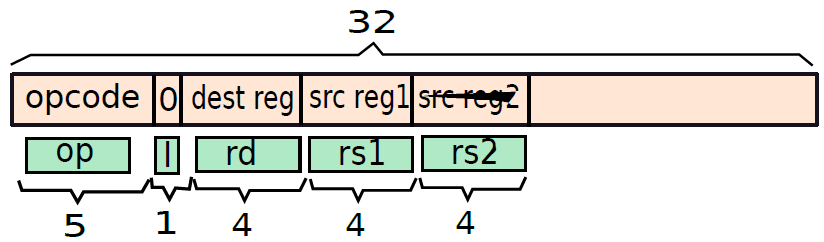

接下來考慮3地址指令:add、sub、mul、div、mod和或、lsl、lsr和asr。

考慮一個通用的3地址指令,它有一個目標暫存器、一個輸入源暫存器和一個可以是暫存器或立即數的第二個源運算元。如果第二個源運算元是暫存器或立即數,需要將一位輸入和輸出。將其稱為I位,並在指令中的操作碼之後指定它。如果I=1,則第二個源運算元是立即數,如果I=0,則第二個源運算元是暫存器。

現在考慮將第二個源運算元作為暫存器(I=0)的3地址暫存器的情況。因為有16個暫存器,所以需要4位元來唯一地指定每個暫存器。暫存器ri可以編碼為i的無符號4位元二進位制等價物。因此,要指定目標暫存器和兩個輸入源暫存器,需要12位元。結構如下圖所示,此指令格式稱為暫存器格式。像分支格式一樣,不妨命名不同的欄位:op(操作碼,位:28-32)、I(立即數,位:27)、rd(目的暫存器,位:23-26)、rs1(源暫存器1,位:19-22)和rs2(源暫存器2,位:15-18)。

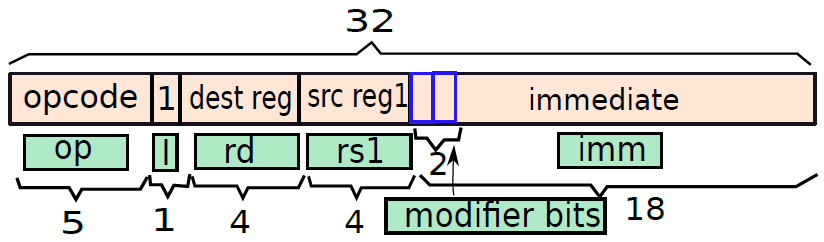

假設第二個源運算元是立即數,那麼需要將I設定為1,接下來計算指定立即數所剩的位數。現在已經為操作碼投入了5位,為I位投入了1位,為目標暫存器投入了4位元,為第一個源暫存器投入了四位,總共花費了14位元。因此,在32位元中,剩下18位元,可以使用它們來指定立即數。

建議將18位元分為兩部分:2位(修改器)+16位元(立即數的常數部分),兩個修改位可以取三個值:00(預設值)、01(「u」)和10(「h」)。當使用預設修改器時,剩餘的16位元用於指定16位元2的二補數數。對於u和h修改器,假設立即欄位中的16位元常數是無符號數。假設立即欄位為18位元長,具有修改部分和常數部分,處理器根據修改器將立即數內部擴充套件為32位元值。

此編碼如下圖所示,可將此指令格式稱為立即數格式。像分支格式一樣,不妨命名不同的欄位:op(操作碼,位:28-32)、I(立即數,位:27)、rd(目標暫存器,位:23-26)、rs1(源暫存器1,位:19-22)和imm(立即數:1-18)。

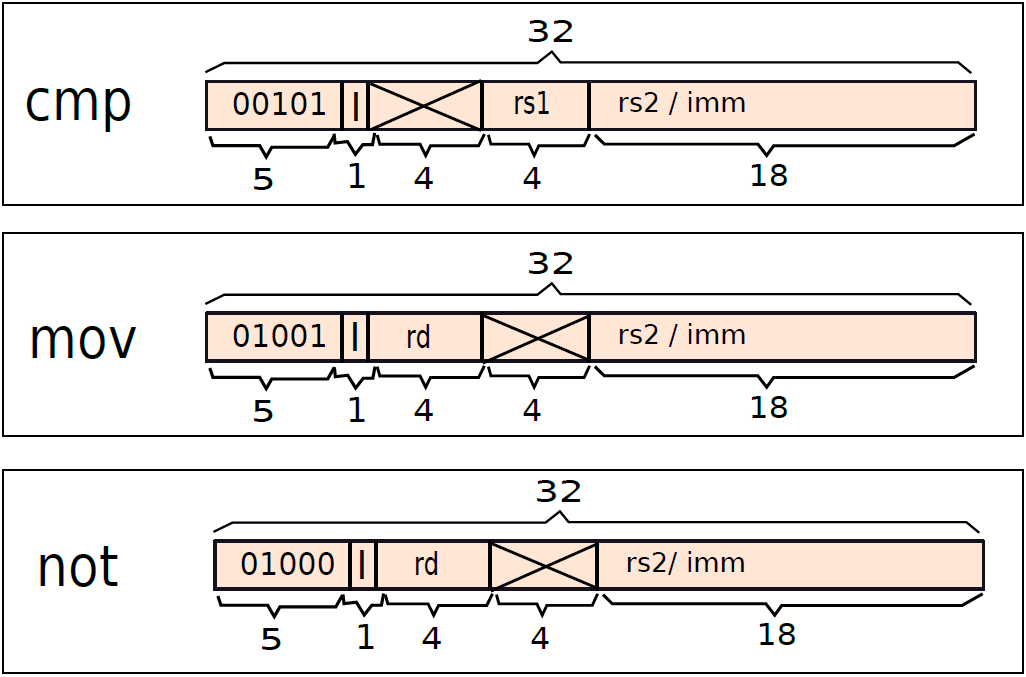

用類似的方式,可以用下圖所示的方式編碼cmp、not和mov指令:

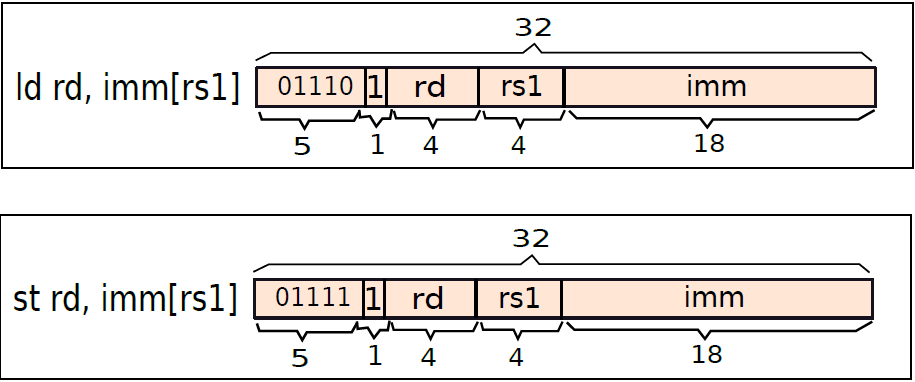

而載入指令的實現如下圖:

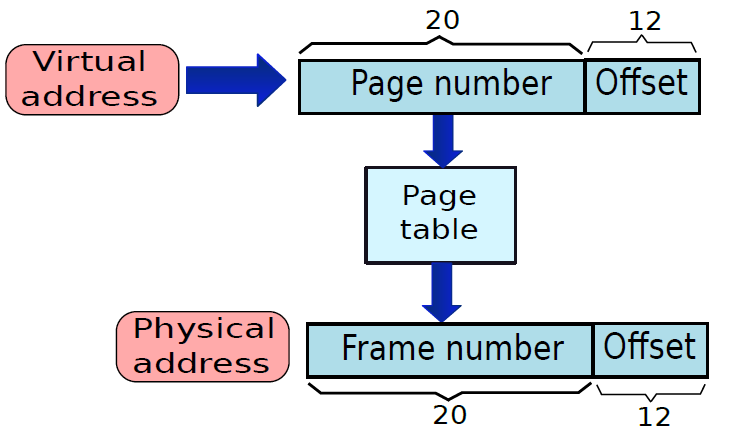

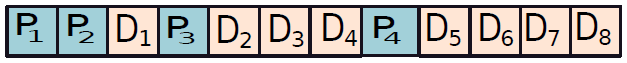

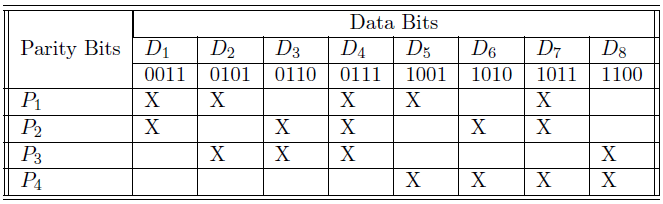

19.4.7 ARM指令編碼

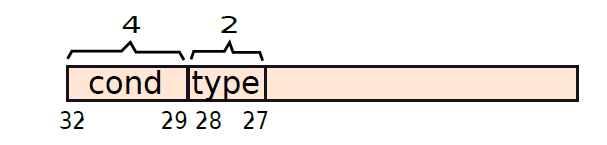

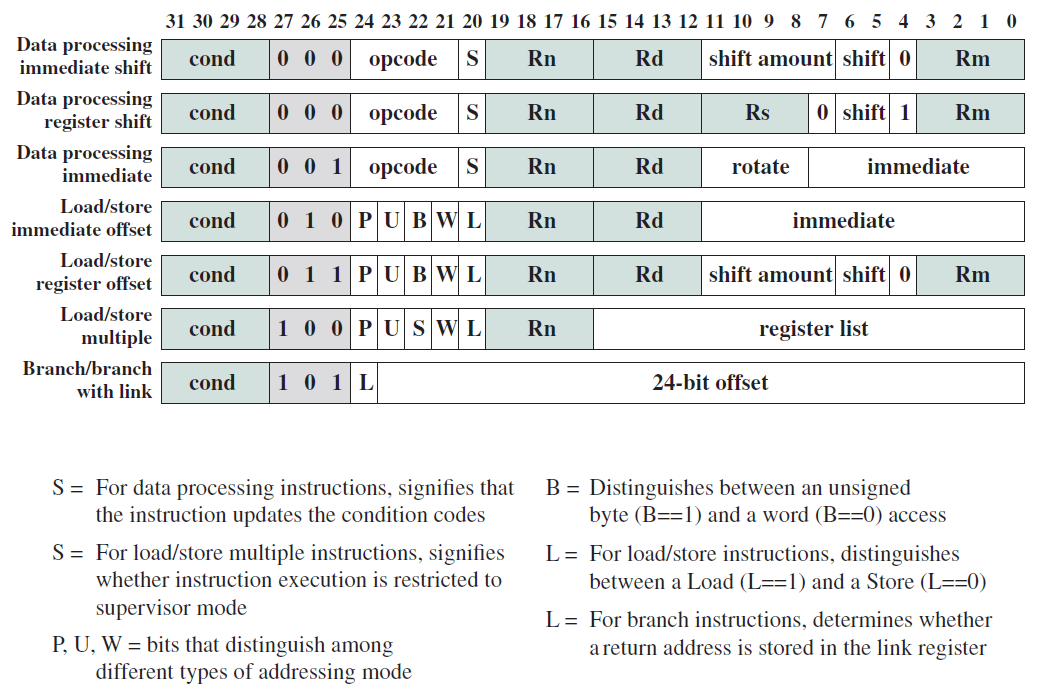

ARM有四種型別的指令:資料處理(加/減/乘/比較)、載入/儲存、分支和其他,需要2位來表示這些資訊,這些位決定了指令的型別。下圖顯示了ARM中指令的通用格式。

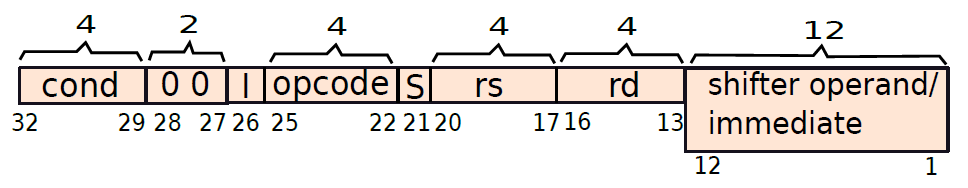

對於資料處理指令,型別欄位等於00,其餘26位需要包含指令型別、特殊條件和暫存器。下圖顯示了資料處理指令的格式。

第26位稱為I(立即數)位,類似於前面所述的I位。如果將其設定為1,則第二個運算元是立即數,否則是暫存器。由於ARM有16條資料處理指令,需要4位元來表示它們,該資訊儲存在第22-25位。第21位儲存S位,如果開啟,則指令將設定CPSR。

其餘20位儲存輸入和輸出運算元。由於ARM有16個暫存器,需要4位元來編碼一個暫存器。第17-20位儲存第一個輸入運算元(rs)的識別符號,要求是一個暫存器。第13-16位元儲存目標暫存器(rd)的識別符號。

位1-12用於儲存立即數或移位器運算元,下面看看如何最好地利用這12位元。

ARM支援32位元立即數,然而實際上只有12位元來編碼它們。不可能對所有\(2^{32}\)個可能的值進行編碼,需要從中選擇一個有意義的子集,想法是使用12位元對32位元值的子集進行編碼,硬體預計將解碼這12位元,並在處理指令時將其擴充套件到32位元。

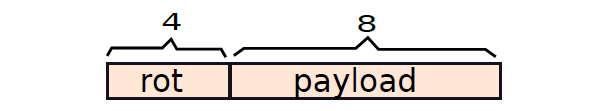

現在,12位元是一個相當不靈活的值,既不是1位元組,也不是2位元組。有必要想出一個非常巧妙的解決方案,想法是將12位元分為兩部分:4位元常數(rot)和8位元有效載荷(payload),參見下圖。

假設12位元中編碼的實際數位為n,有:

其中ror是右旋操作。通過將有效載荷右旋2倍於rot欄位中的值,獲得實際數位n。現在試著理解這樣做的邏輯。

數位n是32位元值。一個天真的解決方案是使用12位元來指定n的最小符號位,高階位可以是0。然而,程式設計師傾向於以位元組為單位存取資料和記憶體,因此1.5個位元組對我們毫無用處。更好的解決方案是使用1位元組的有效載荷,並將其放置在32位元欄位中的任何位置,其餘4位元用於此目的,它們可以對0到15之間的數位進行編碼。ARM處理器將該值加倍,以考慮0到30之間的所有偶數,將有效載荷向右旋轉該量。這樣做的好處是可以對更廣泛的數位集進行編碼,對於所有這些數位,有8位元對應於有效載荷,其餘24位元均為零。rot位僅確定32位元欄位中的哪8位元被有效載荷佔用。

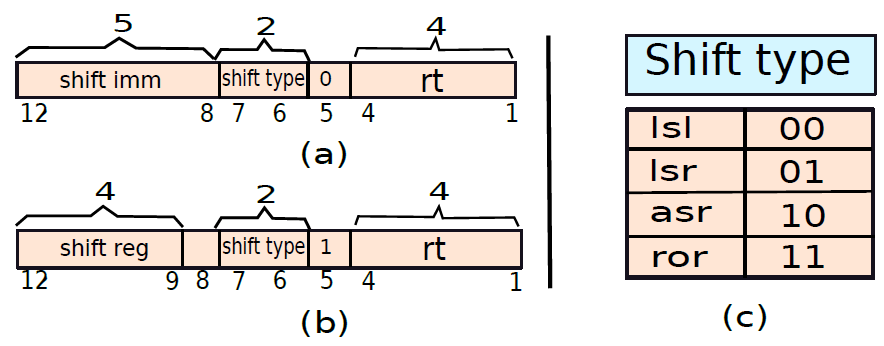

同樣地,通過合理地思考,可以得到以下的位移指令格式圖:

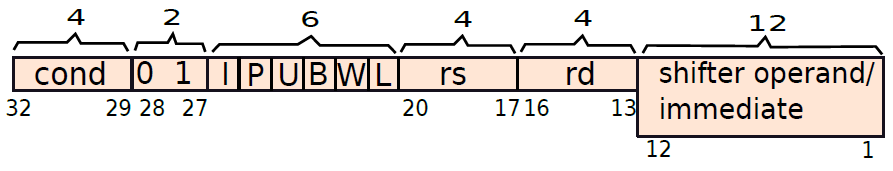

此外,載入、儲存指令格式如下:

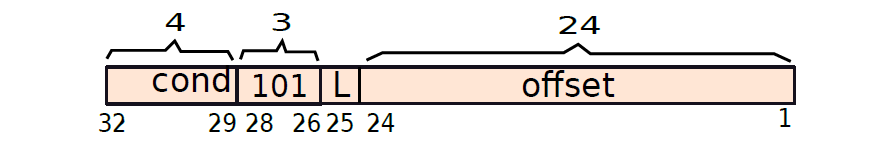

而分支指令如下:

ARM Endian支援使用E-Bit載入/儲存字:

19.4.8 x86指令編碼

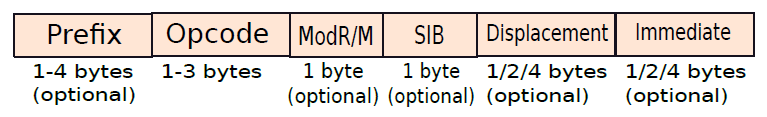

x86是真正的CISC指令集,其編碼過程更為規律,幾乎所有的指令都遵循標準格式。其次,x86中的操作碼通常有多種模式和字首。先看看編碼機器指令的廣泛結構,下圖顯示了二進位制編碼指令的結構。

x86二進位制指令格式。

x86指令格式細節。

第一組1-4位元組用於編碼指令的字首,rep字首就是其中一個例子,還有許多其他型別的字首可以在第一組1-4位元組中編碼。

接下來的1-3個位元組用於對操作碼進行編碼,整個x86 ISA有數百條指令,操作碼還編碼運算元的格式。例如,加法指令可以將其第一個運算元作為記憶體運算元,也可以將其第二個運算元用作記憶體運算元。此資訊也是操作碼的一部分。

接下來的兩個位元組是可選的。第一個位元組被稱為ModR/M位元組,用於指定源暫存器和目標暫存器的地址,第二個位元組被稱作SIB(標度索引基)位元組,該位元組記錄基本縮放索引和基本縮放索引偏移定址模式的引數,記憶體地址可以可選地具有32位元的位移(在本書中也稱為偏移量)。因此,我們可以選擇在一條指令中多4個位元組來記錄位移值。最後,一些x86指令接受立即數作為運算元,立即數也可以大到32位元,因此,最後一個欄位(也是可選的)用於指定立即數運算元。

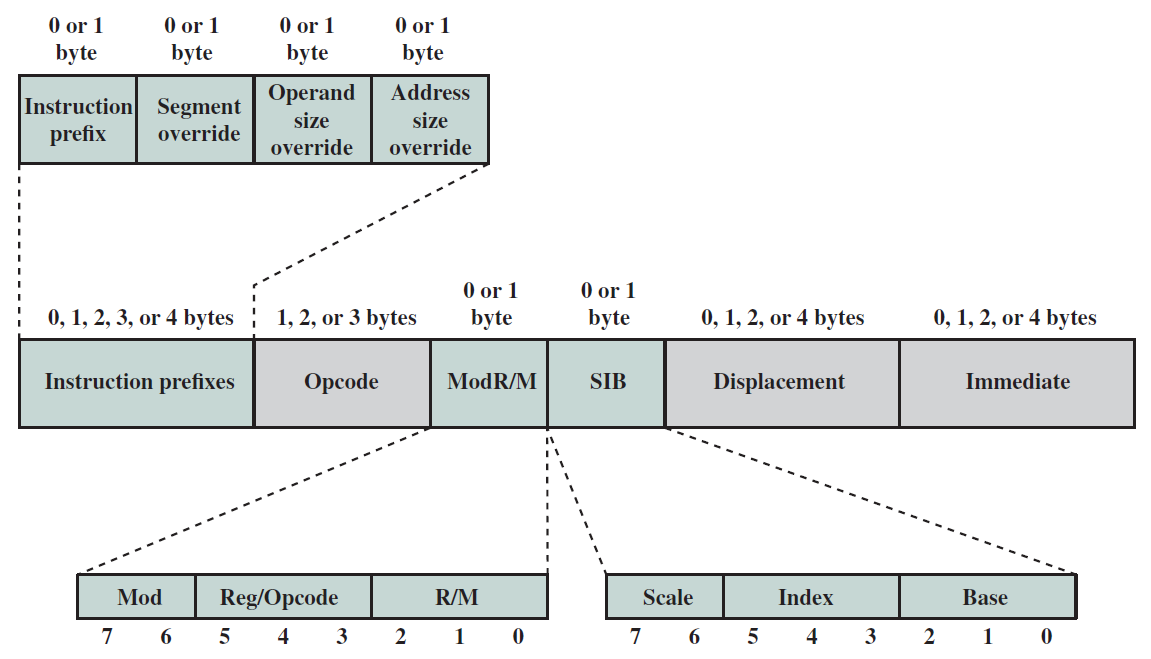

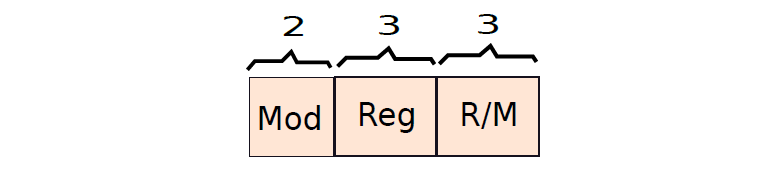

ModR/M位元組有三個欄位,如下圖所示:

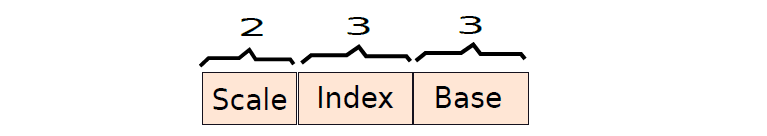

SIB位元組的結構如下圖所示:

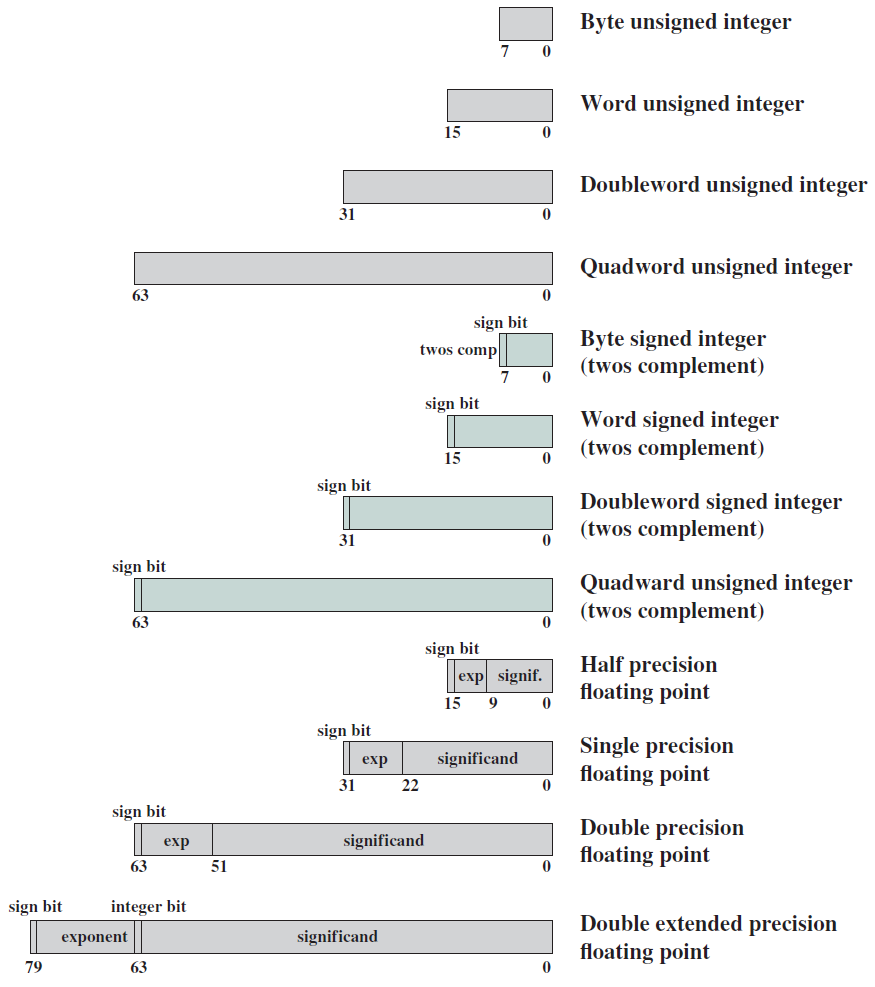

x86數位資料格式如下:

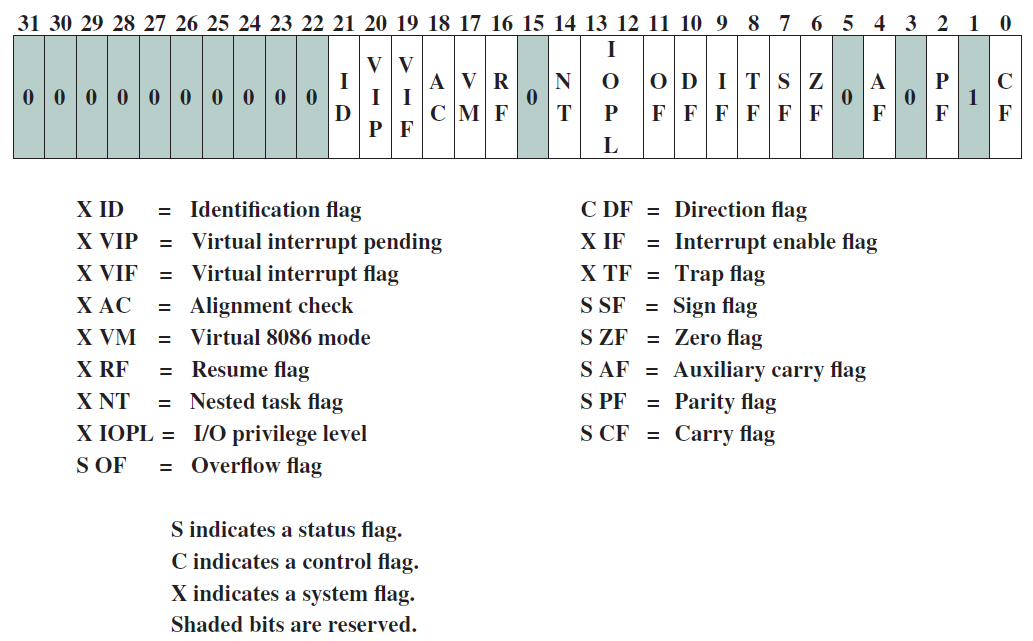

x86 EFLAGS暫存器:

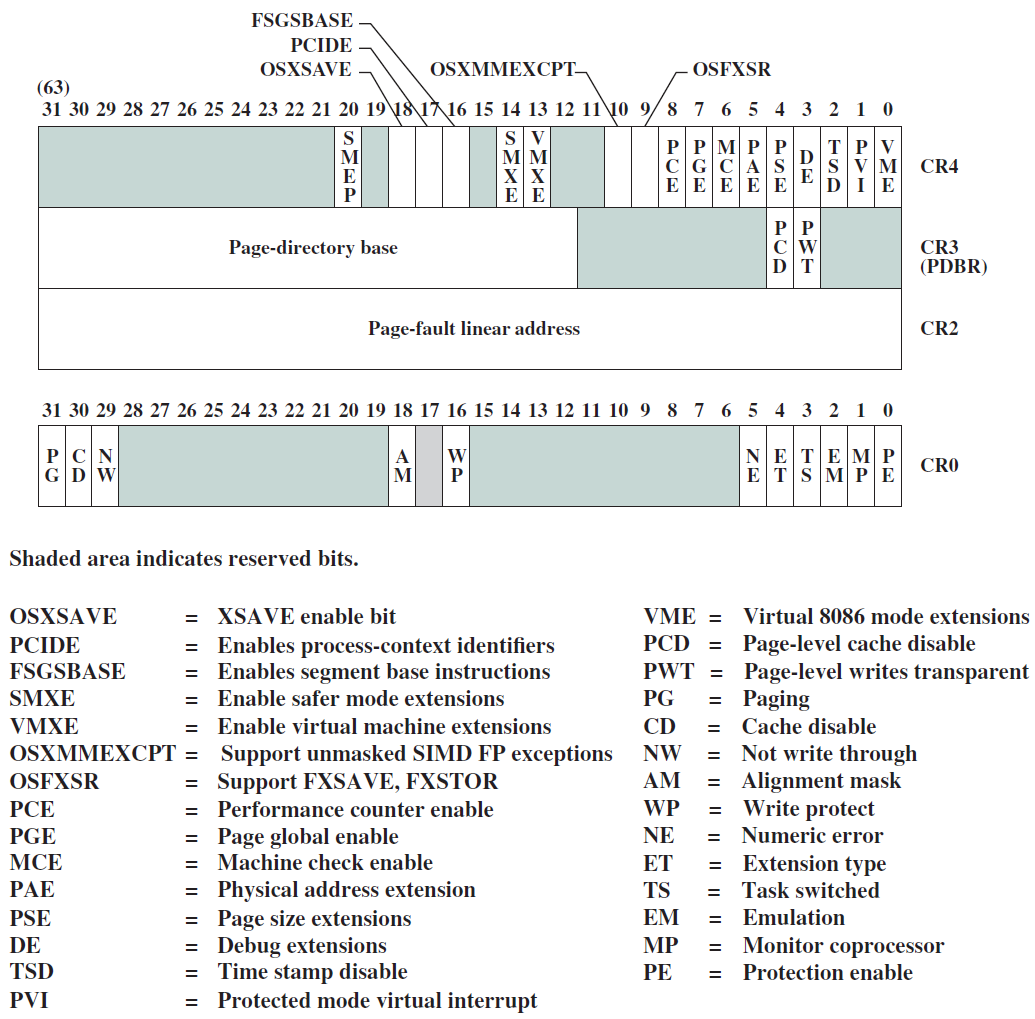

x86控制暫存器:

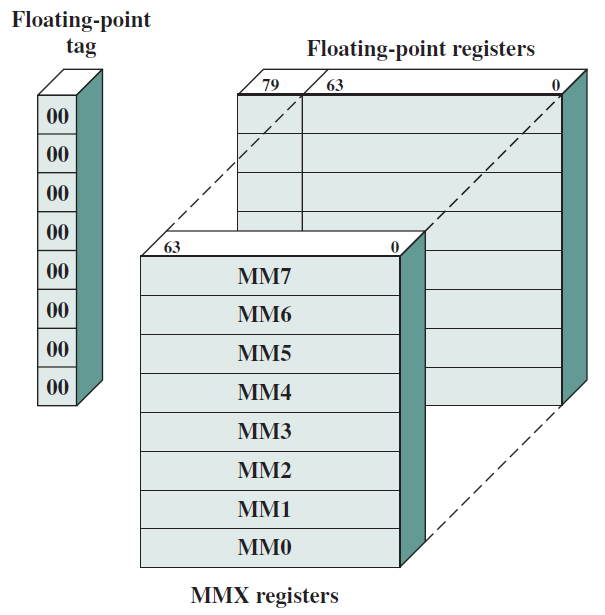

MMX暫存器到浮點暫存器的對映:

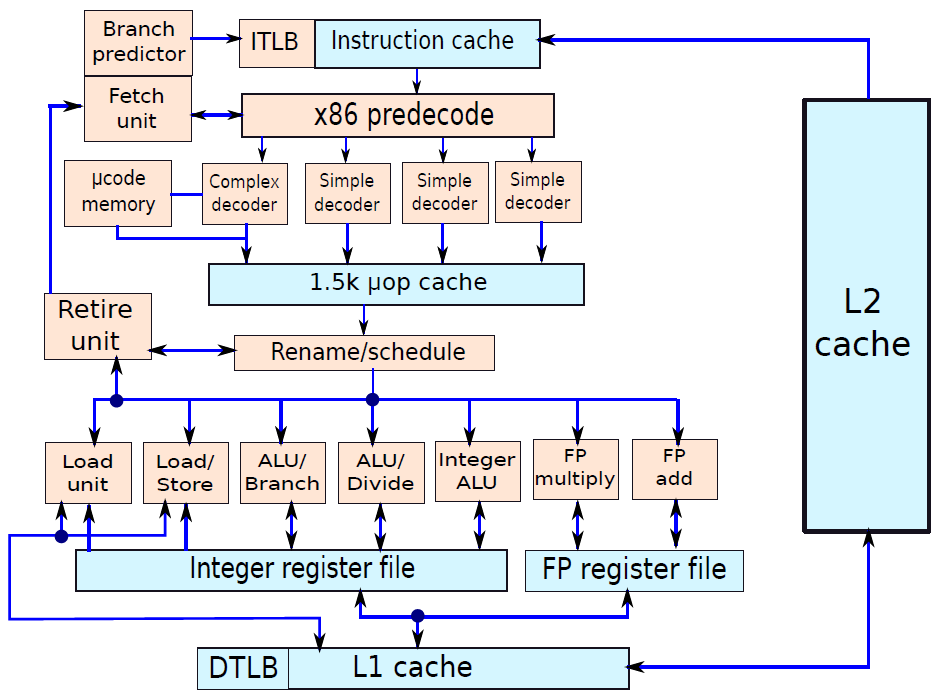

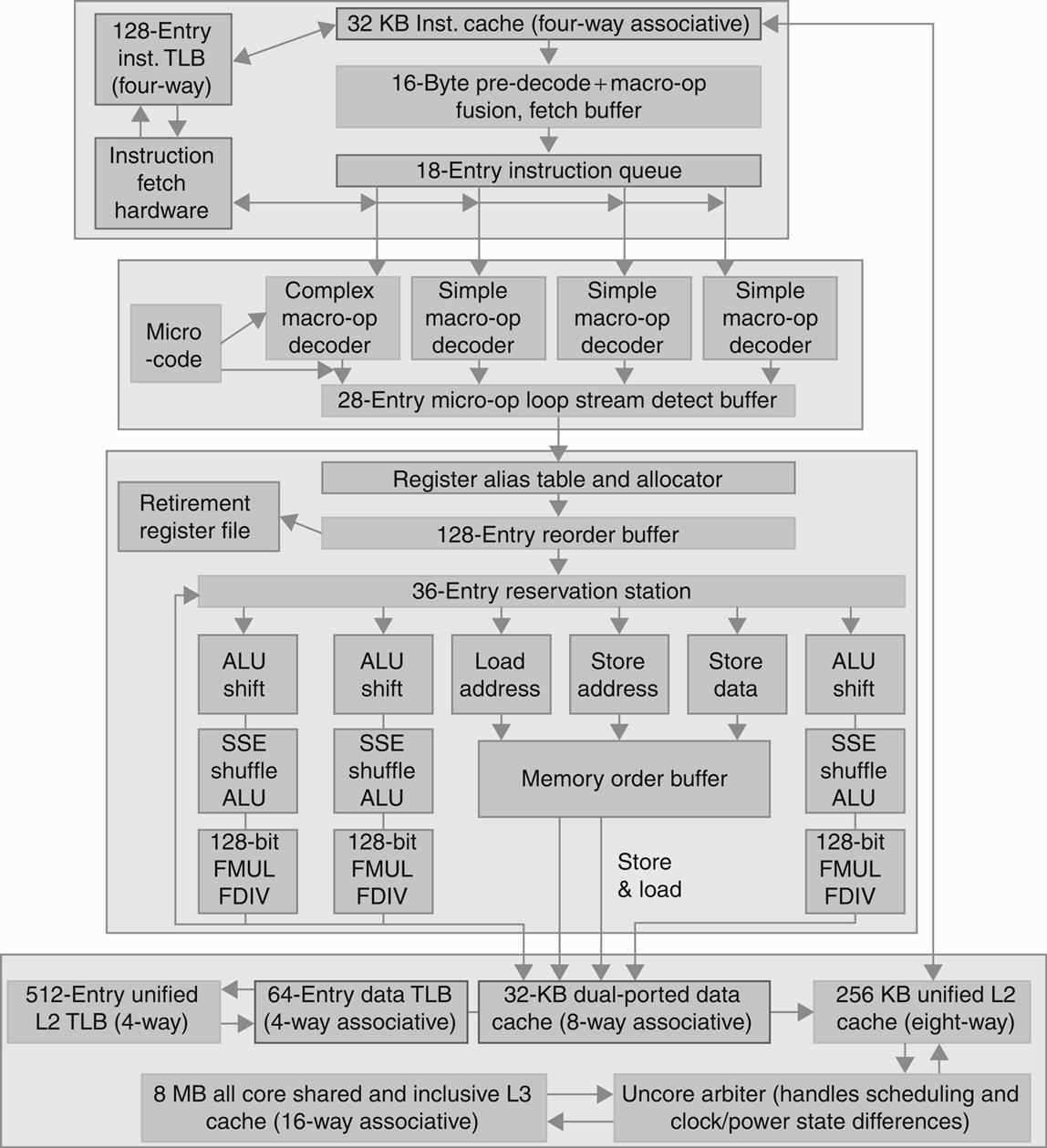

19.5 處理器

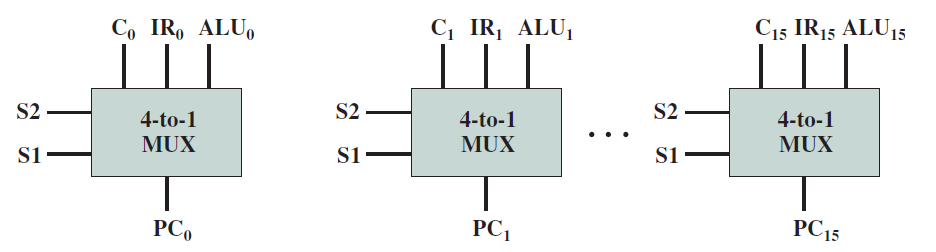

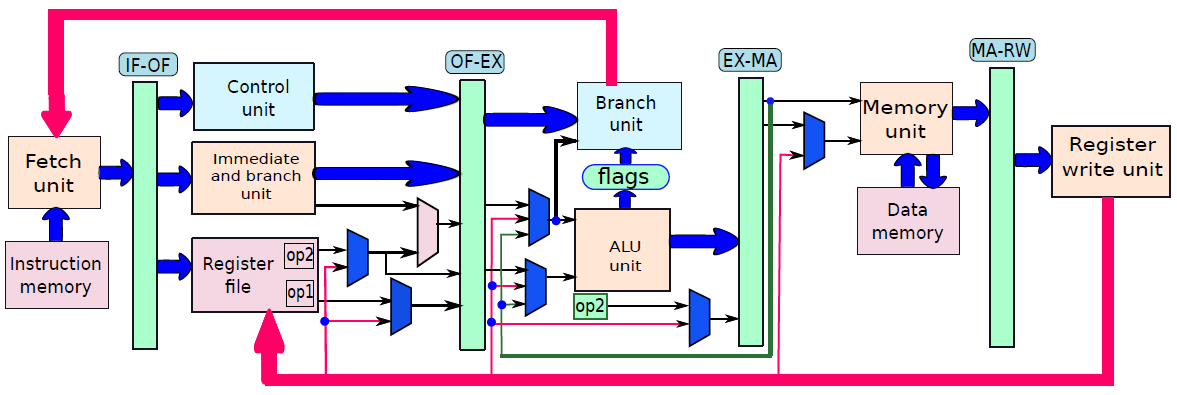

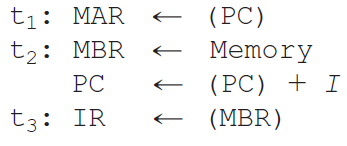

19.5.1 指令處理概覽

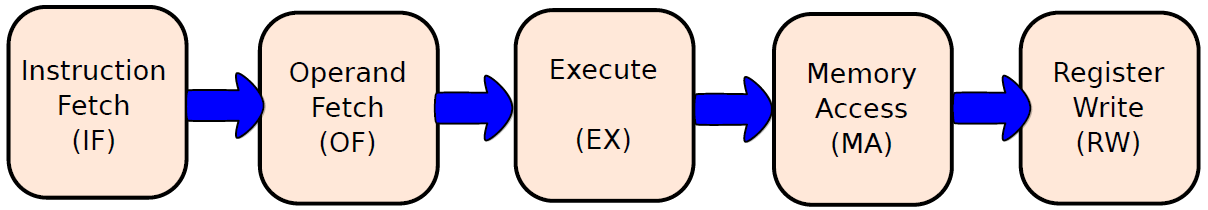

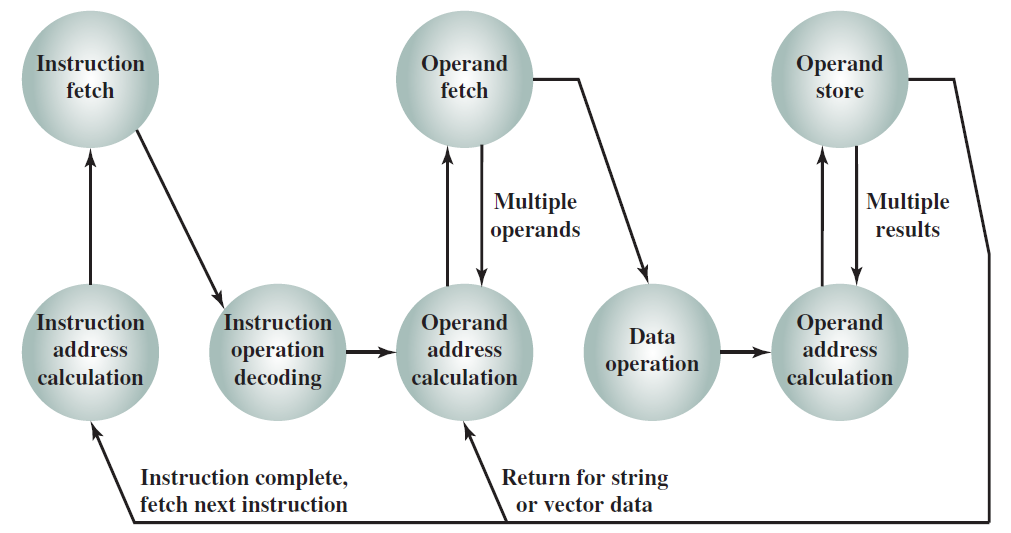

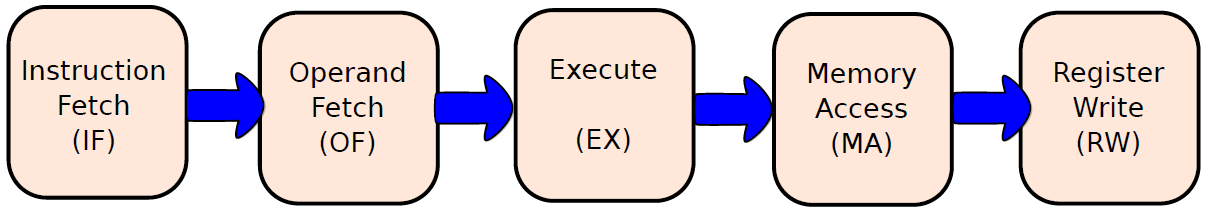

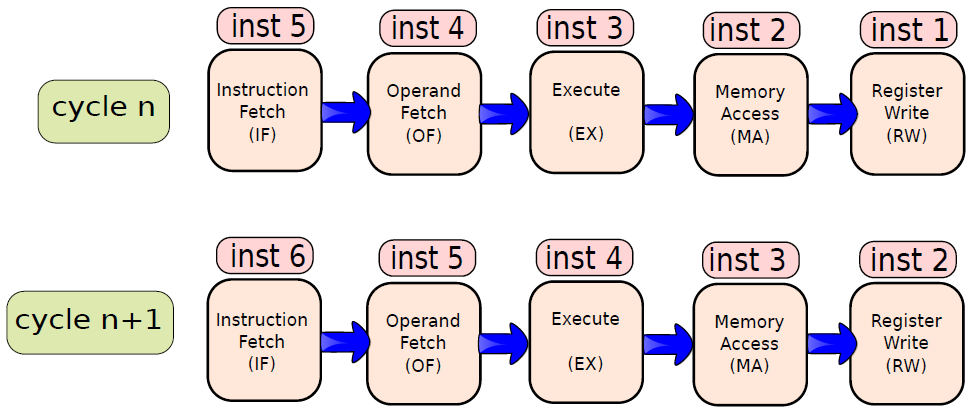

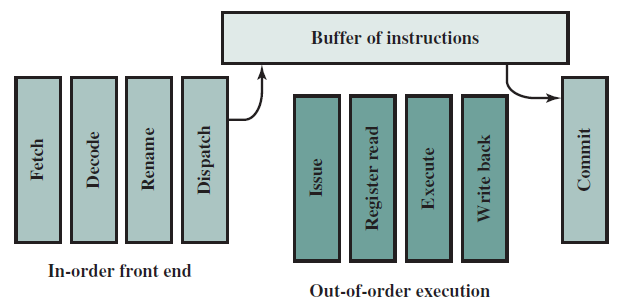

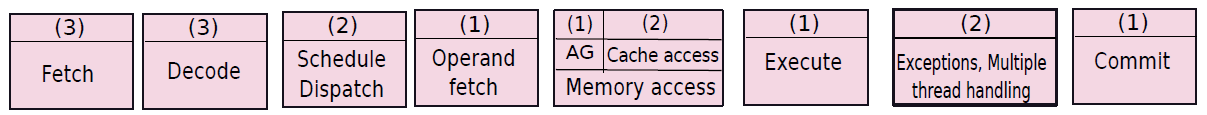

我們可以將處理器的操作大致分為五個階段,如下圖所示。

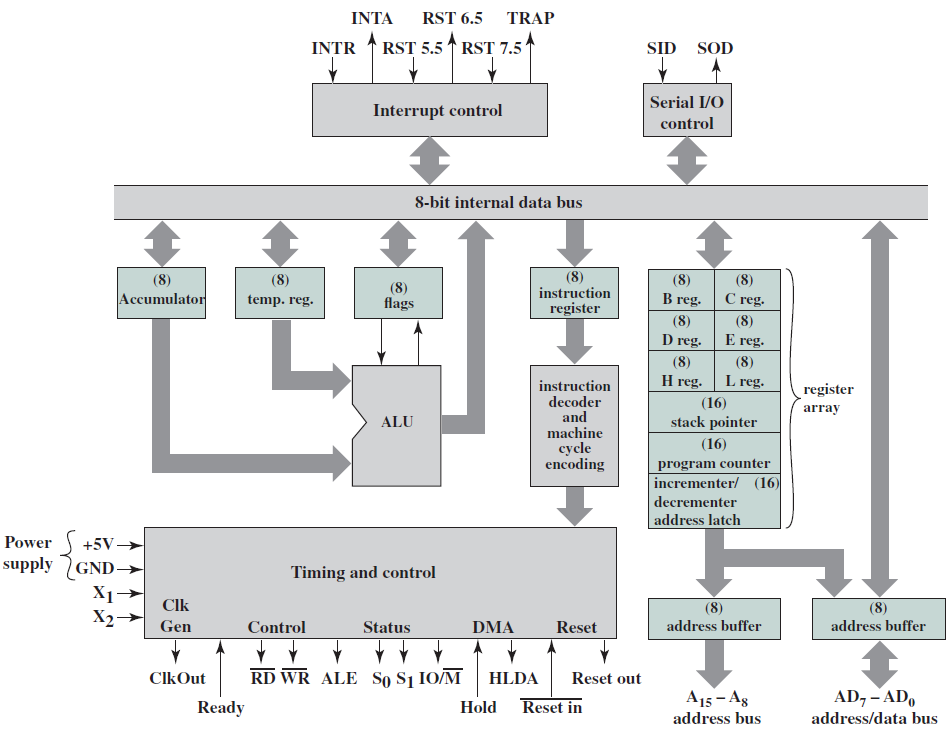

指令處理的五個階段:指令獲取、運算元獲取、執行、記憶體存取、暫存器寫入。

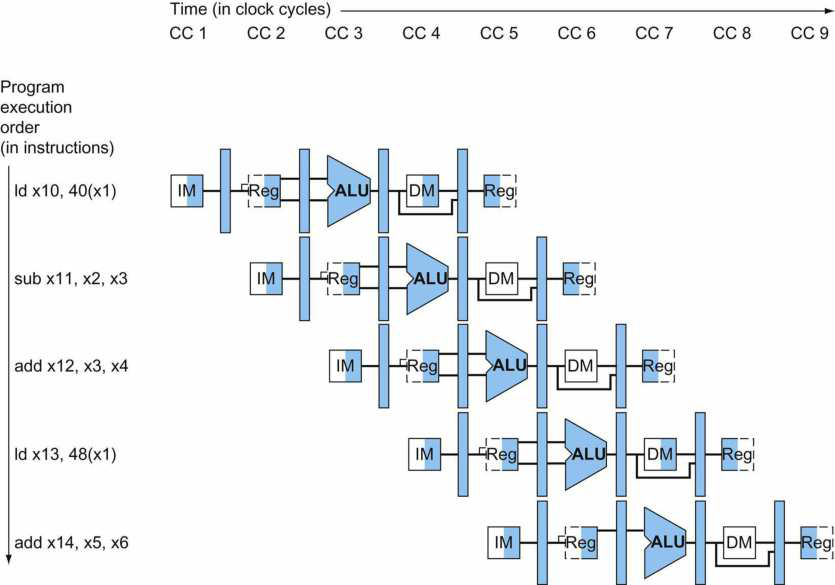

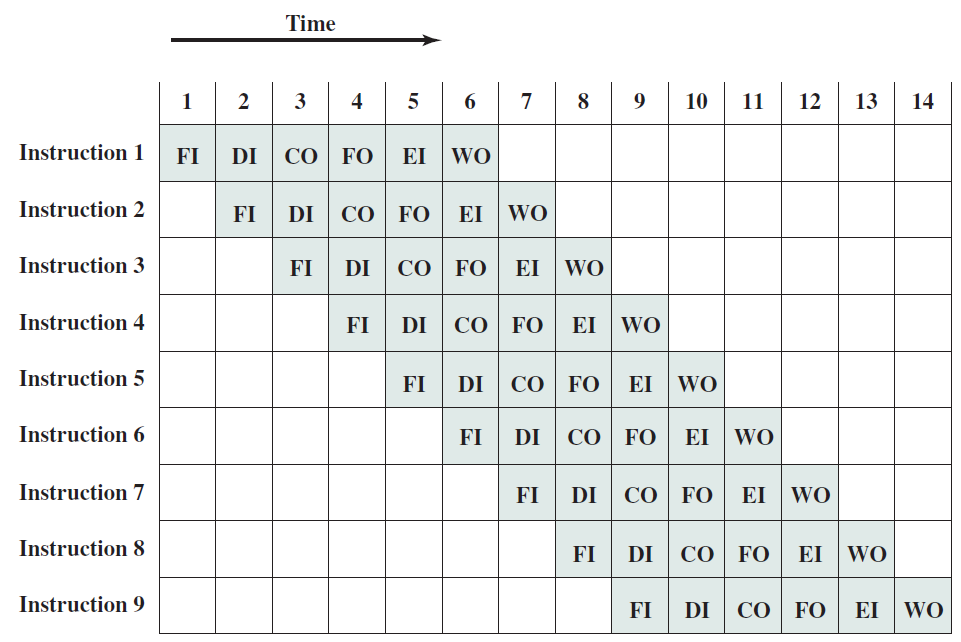

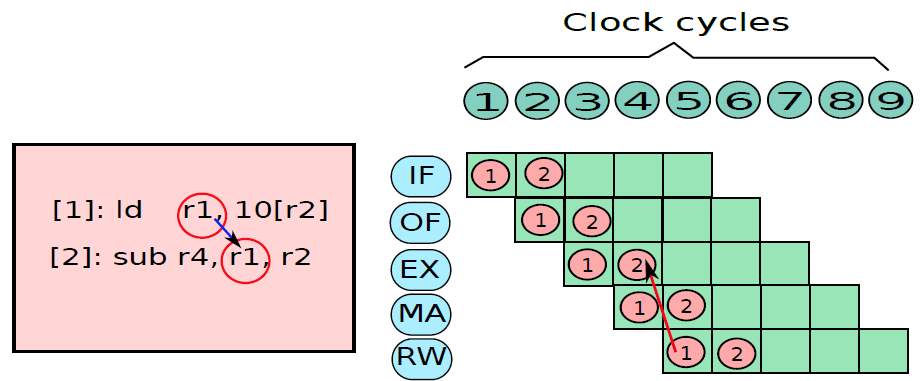

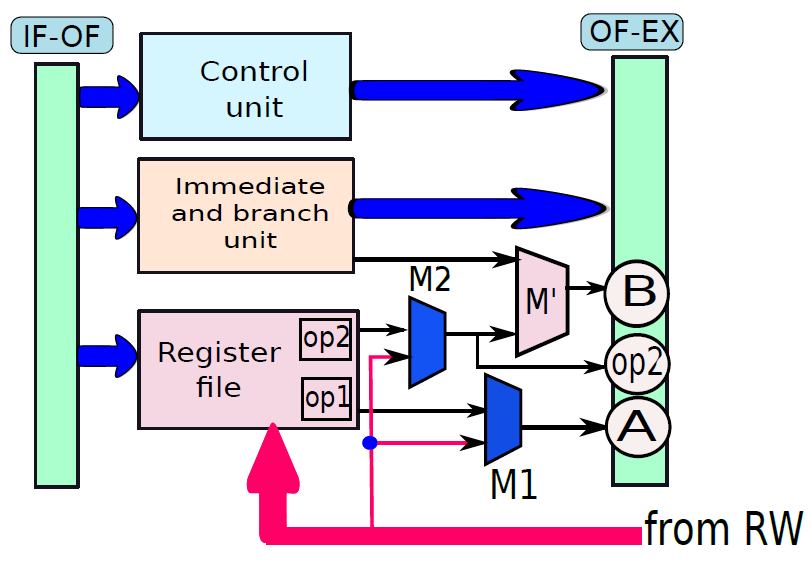

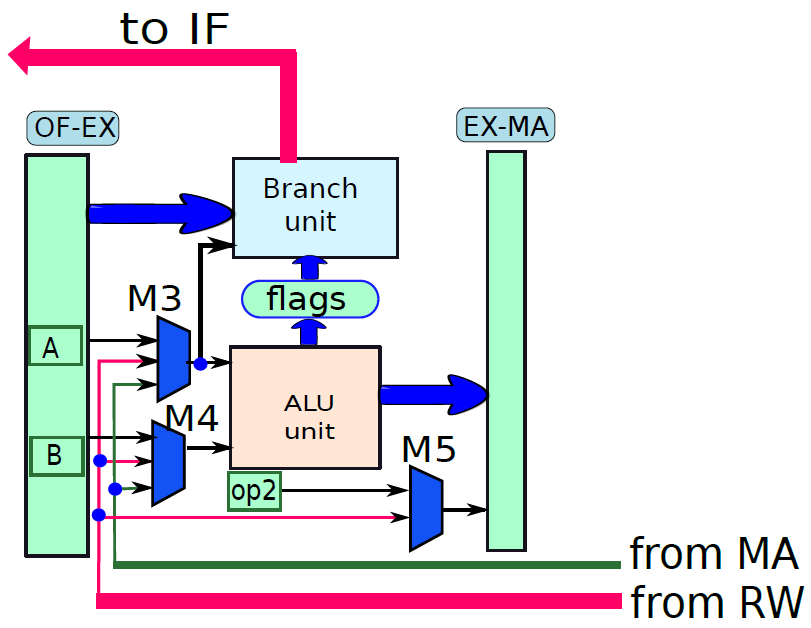

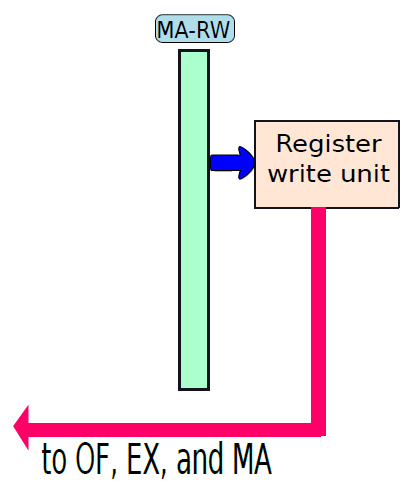

指令的多時鐘週期管線圖。圖中時間從左到右在頁面上前進,指令從頁面的頂部到底部前進。管線階段的表示沿指令軸放置在每個部分,佔據適當的時鐘週期。圖中顯示了每個階段之間的管線暫存器,資料路徑以圖形方式表示管線的五個階段,但命名每個管線階段的矩形也同樣有效。

第1步是從記憶體中獲取指令。機器的底層組織並不重要,該機器可以是馮·諾依曼機器(共用指令和資料記憶體),也可以是哈佛機器(專用指令記憶體)。提取階段有邏輯元件來計算下一條指令的地址,如果當前指令不是分支,那麼需要將當前指令的大小(4位元組)新增到儲存在PC中的地址。但如果當前指令是分支,那麼下一條指令的地址取決於分支的結果和目標。此資訊從處理器中的其他單元獲得。

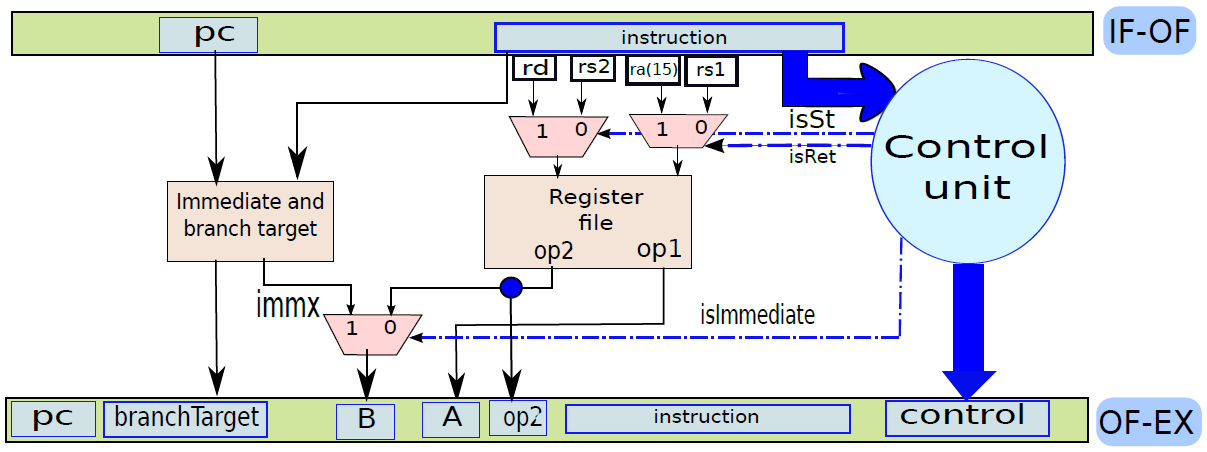

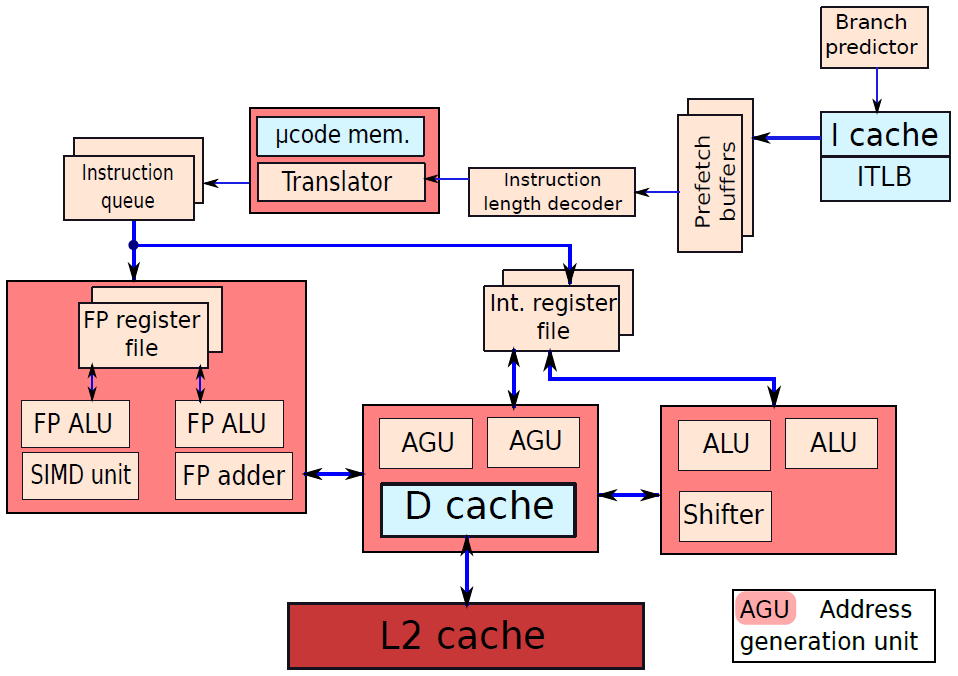

第2步是解碼「指令並從暫存器中取出運算元。不同指令型別所需的處理非常不同,例如載入儲存指令使用專用的儲存單元,而算術指令則不使用。為了解碼指令,處理器有專用的邏輯電路,根據指令中的欄位生成訊號,這些訊號隨後被其他模組用來正確處理指令。像Intel處理器這樣的商用處理器有非常複雜的解碼單元,解碼x86指令集非常複雜。不管解碼的複雜程度如何,解碼過程通常包括以下步驟:

- 提取運算元的值,計算嵌入的立即數並將其擴充套件到32或64位元,以及生成關於指令處理的附加資訊。

- 生成關於指令的更多資訊的過程包括生成處理器專用訊號。例如,可以為載入/儲存指令生成「啟用記憶體單元」形式的訊號,對於儲存指令,可以生成一個禁用暫存器寫入功能的訊號。

第3步是執行算術和邏輯運算。它包含一個能夠執行所有算術和邏輯運算的算術和邏輯單元(ALU),ALU還需要計算載入儲存操作的有效地址,通常情況下處理器的這一部分也計算分支的結果。

ALU(算術邏輯單元)包含用於對資料值執行算術和邏輯計算的元素,通常包含加法器、乘法器、除法器,並具有計算邏輯位運算的單元。

第4步包含用於處理載入儲存指令的儲存單元。該單元與記憶體系統介面,並協調從記憶體載入和儲存值的過程。典型處理器中的記憶體系統相當複雜,其中一些複雜性是在處理器的這一部分中實現的。

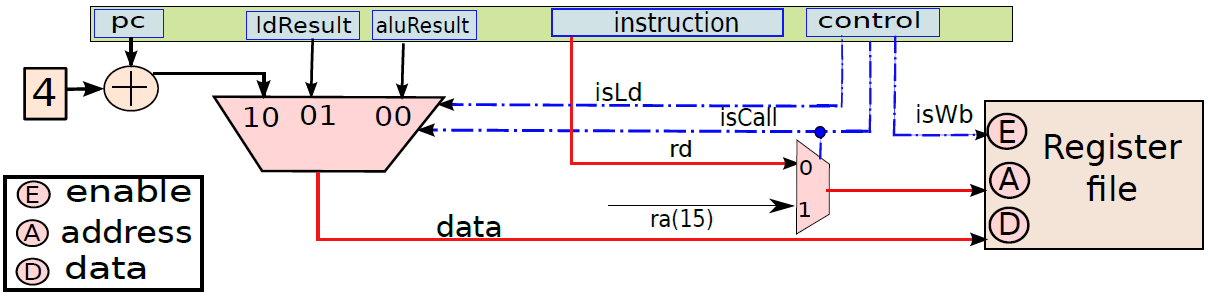

第5步是將ALU計算的值或從記憶體單元獲得的載入值寫入暫存器檔案。

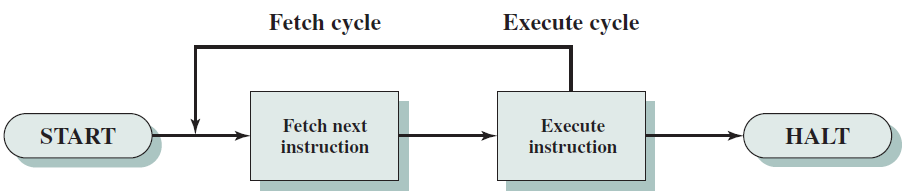

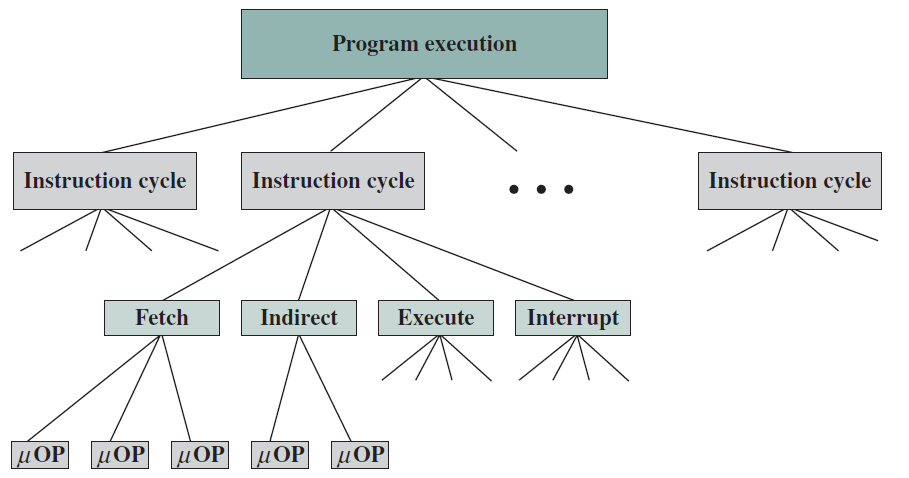

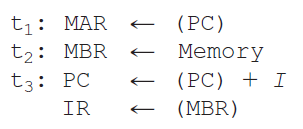

單個指令所需的處理稱為指令週期。使用前面給出的簡化的兩步描述,指令週期如下圖所示,這兩個步驟被稱為獲取週期和執行週期。只有在機器關閉、發生某種不可恢復的錯誤或遇到使計算機停止的程式指令時,程式執行才會停止。

基本指令週期。

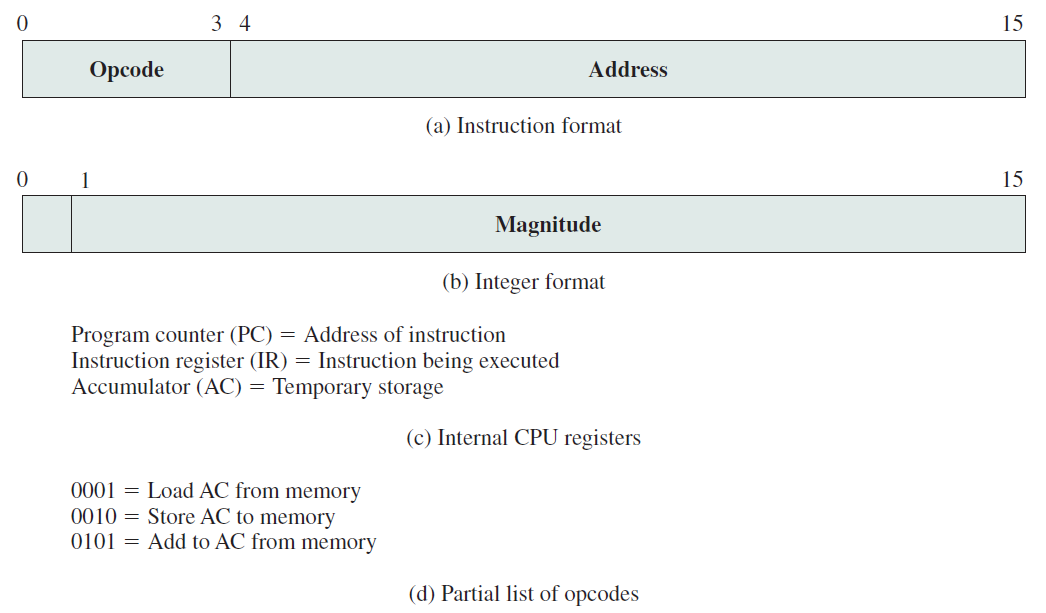

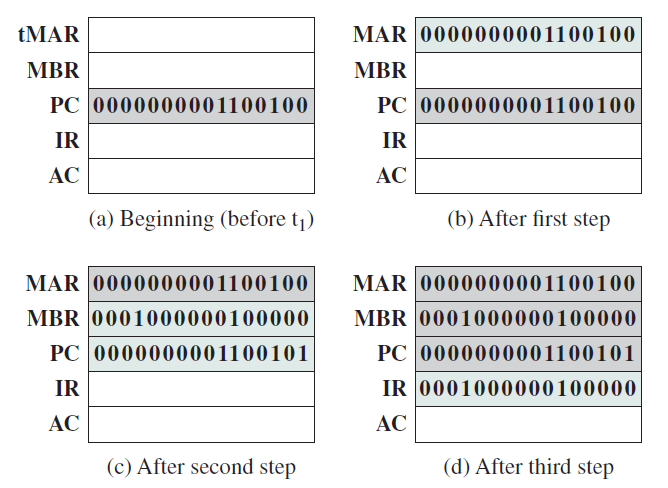

考慮一個使用假設機器的簡單範例,該機器包括下圖中列出的特性。處理器包含一個稱為累加器(AC)的資料暫存器,指令和資料都是16位元長,因此使用16位元字組織記憶體是方便的。指令格式為操作碼提供4位元,因此可以有多達\(2^4=16\)個不同的操作碼,並且可以直接定址多達\(2^{12}=4096\)(4K)個字的記憶體。

假想機器的特性。

下圖說明了部分程式執行,顯示了記憶體和處理器暫存器的相關部分。所示的程式片段將地址940處的儲存字的內容新增到地址941處的記憶體字的內容,並將結果儲存在後一位置。需要三條指令,可以描述為三個獲取和三個執行週期:

1、PC包含300,即第一條指令的地址。該指令(十六進位制值1940)被載入到指令暫存器IR中,PC遞增。注意,此過程涉及使用記憶體地址暫存器和記憶體緩衝暫存器。為了簡單起見,這些中間暫存器被忽略。

2、IR中的前4位元(第一個十六進位制數位)表示要載入AC,剩餘的12位元(三個十六進位制數位)指定要載入資料的地址(940)。

3、從位置301獲取下一條指令(5941),並且PC遞增。

4、新增AC的舊內容和位置941的內容,並將結果儲存在AC中。

5、從位置302取出下一條指令(2941),並且PC遞增。

6、AC的內容儲存在位置941中。

程式執行範例(記憶體和暫存器的內容為十六進位制)。

特定指令的執行週期可能涉及對記憶體的不止一次參照。此外,指令可以指定I/O操作,而不是記憶體參照。考慮到這些額外的考慮因素,圖下圖提供了基本指令週期的更詳細的檢視,該圖採用狀態圖的形式。對於任何給定的指令週期,某些狀態可能為空,而其他狀態可能被存取多次。

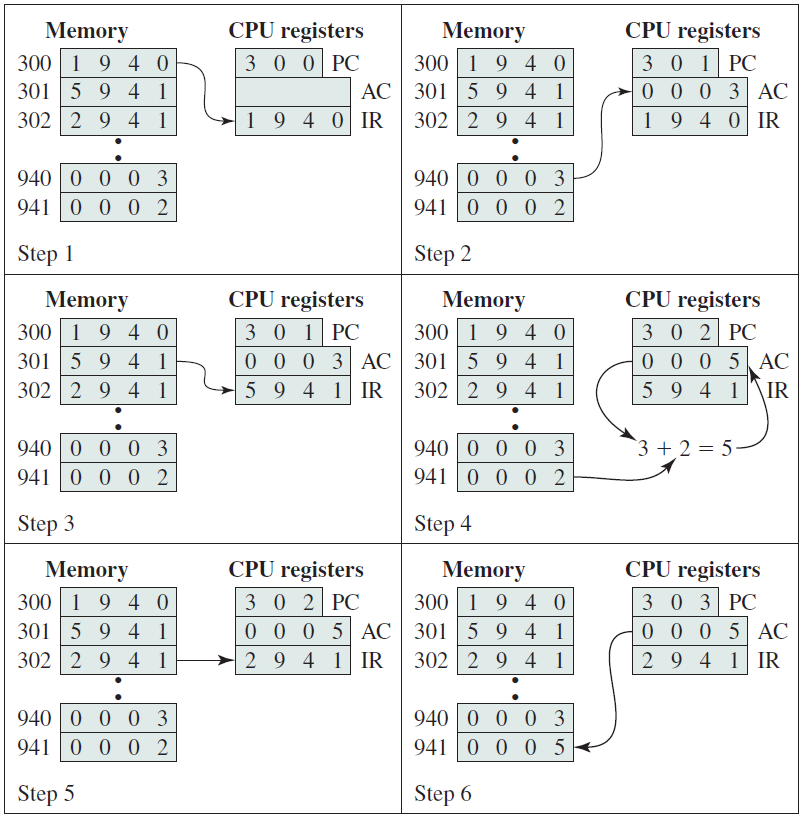

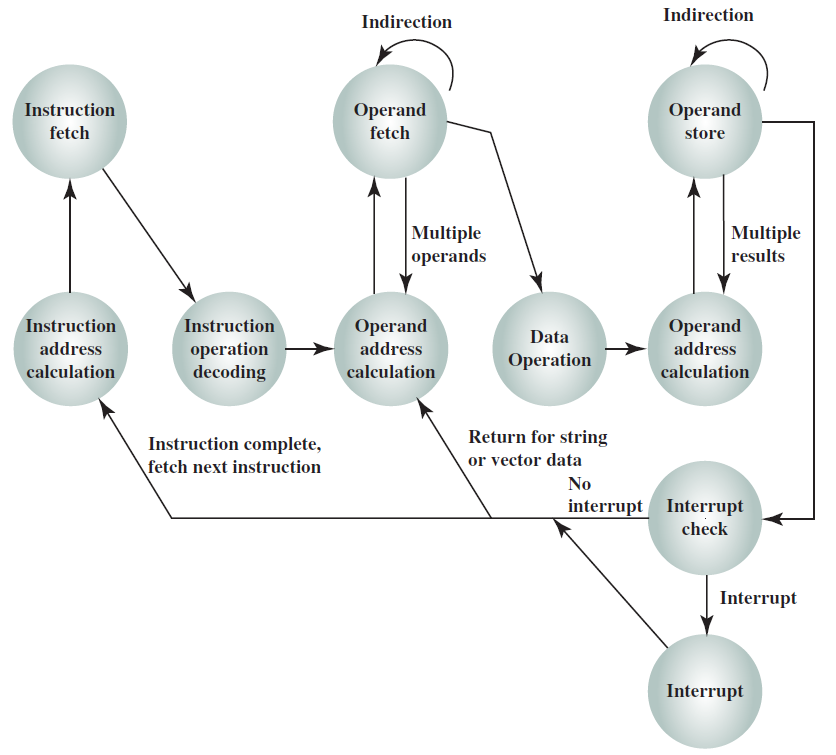

指令週期狀態圖。

狀態描述如下:

- 指令地址計算(iac):確定要執行的下一條指令的地址,通常需要在前一條指令的地址上新增一個固定的數位,例如如果每條指令的長度為16位元,並且記憶體被組織為16位元字,則在前一個地址上加1。相反,如果記憶體被組織為可單獨定址的8位元位元組,則在前一個地址上加2。

- 指令獲取(if):將指令從其記憶體位置讀入處理器。

- 指令操作解碼(iod):分析指令以確定要執行的操作型別和要使用的運算元。

- 運算元地址計算(oac):如果操作涉及對記憶體中的運算元的參照或通過I/O可用的運算元,則確定運算元的地址。

- 運算元獲取(of):從記憶體中獲取運算元或從I/O中讀取運算元。

- 資料操作(do):執行指令中指示的操作。

- 運算元儲存(os):將結果寫入記憶體或輸出到I/O。

下圖顯示了包括中斷週期處理的修訂指令週期狀態圖:

下圖左是非直接時鐘週期,右是中斷時鐘週期:

下圖通過指出每種模組型別的主要輸入和輸出形式,說明了所需的交換型別:

微處理器暫存器組織範例:

19.5.2 處理器結構

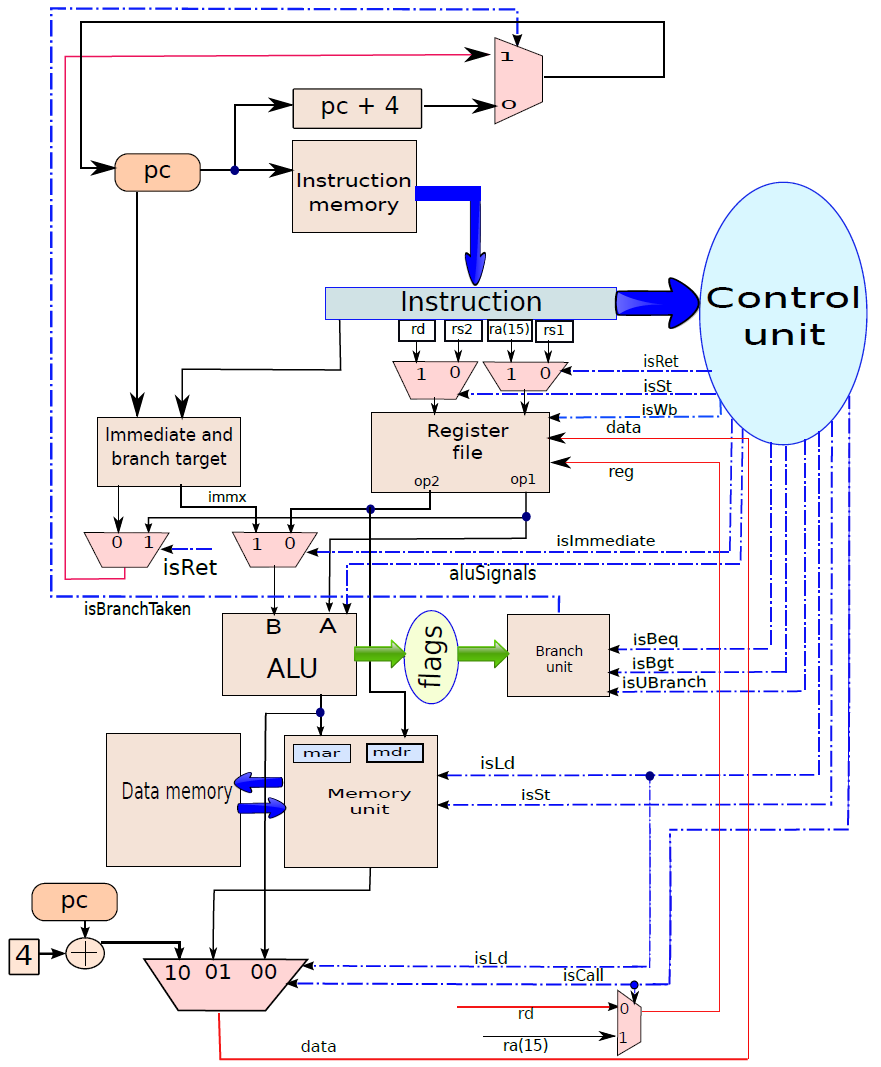

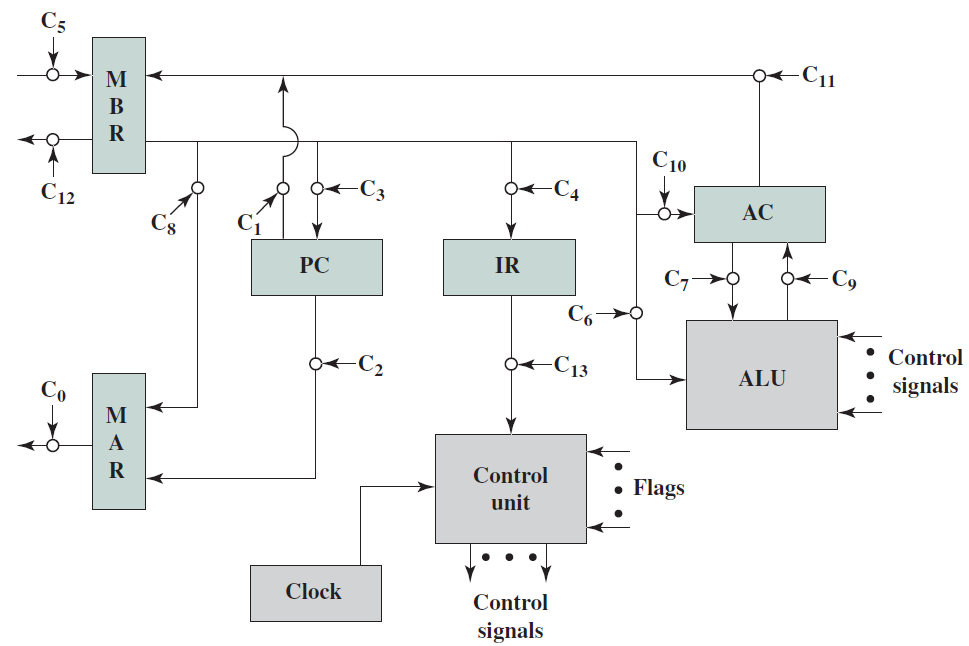

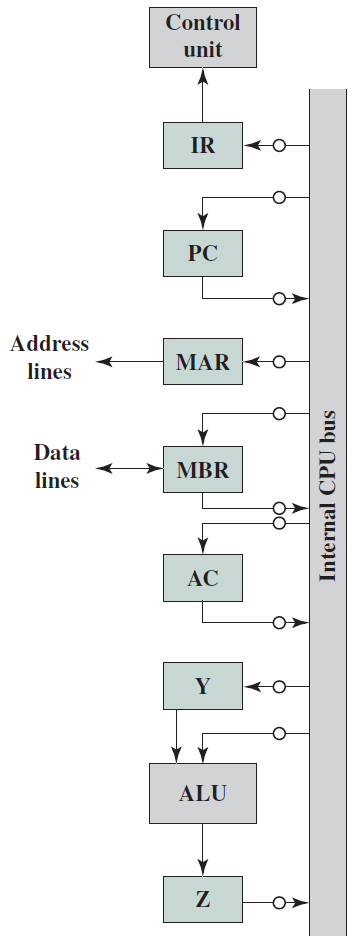

19.5.2.1 處理器單元

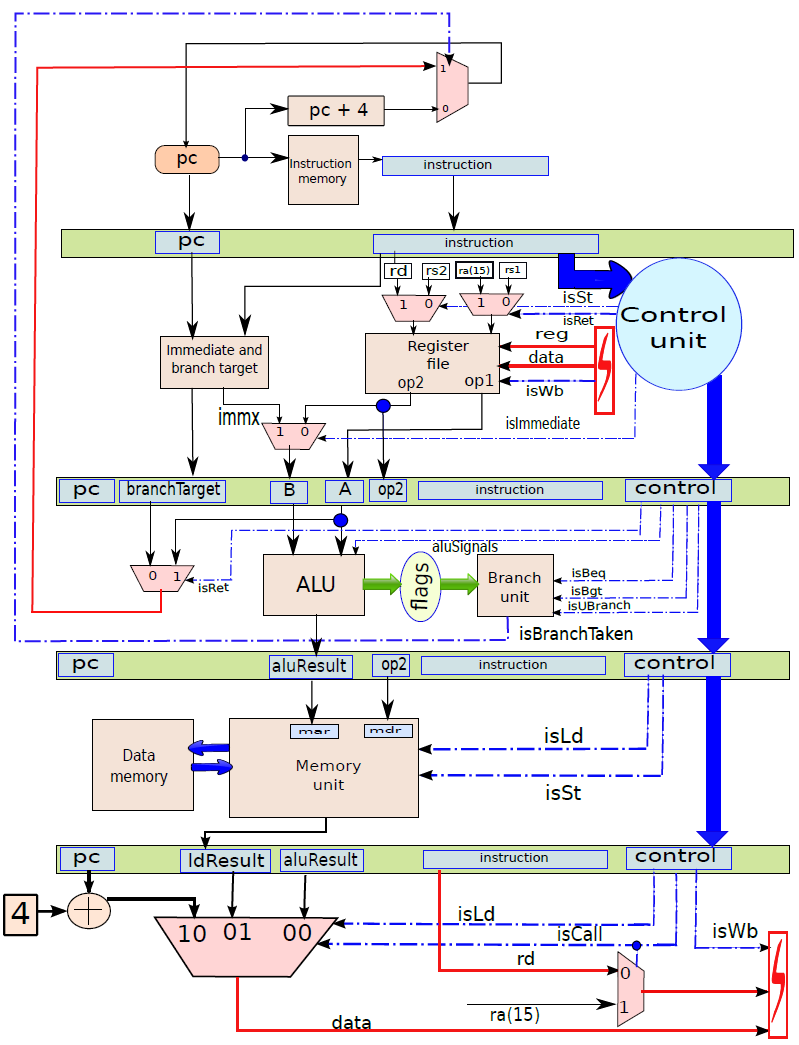

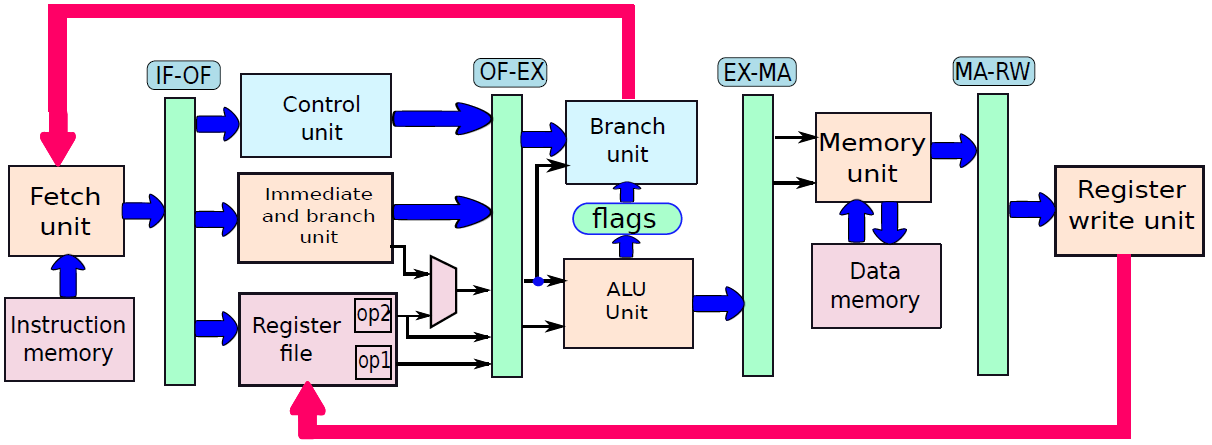

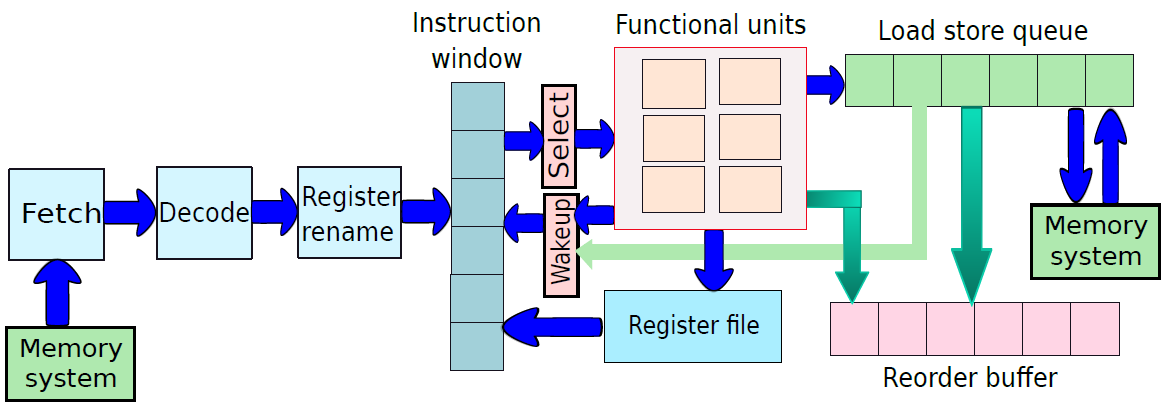

處理器內部包含了諸多單元,諸如獲取單元、資料路徑和控制單元、運算元獲取單元、執行單元(分支單元、ALU)、記憶體存取單元、暫存器回寫單元等等。

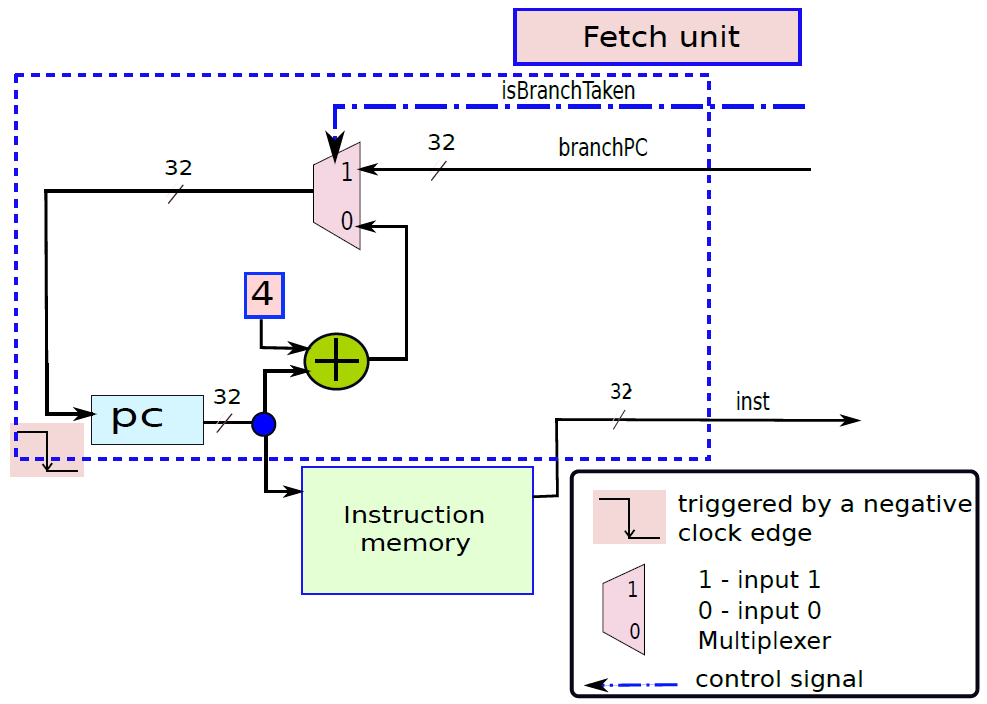

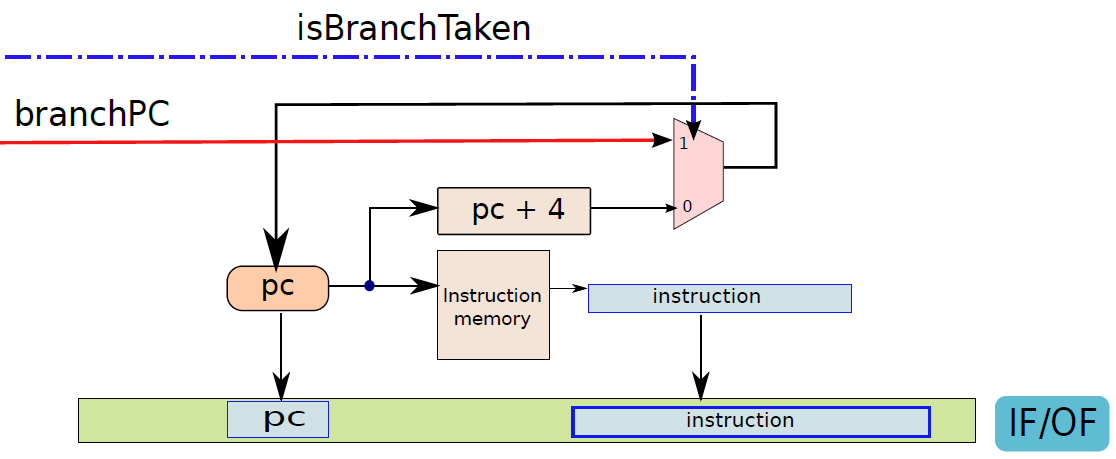

下圖顯示了獲取單元電路的實現。在一個週期中需要執行兩個基本操作:1、下一個PC(程式計數器)的計算;2、獲取指令。

電路中有兩種元件:

- 第一類元件是暫存器、記憶體、算術和邏輯電路,用於處理資料值。

- 第二類元素是決定資料流方向的控制單元。處理器中的控制單元通常生成訊號以控制所有多路複用器(multiplexer),被稱為控制訊號(control signal),因為其作用是控制資訊流。

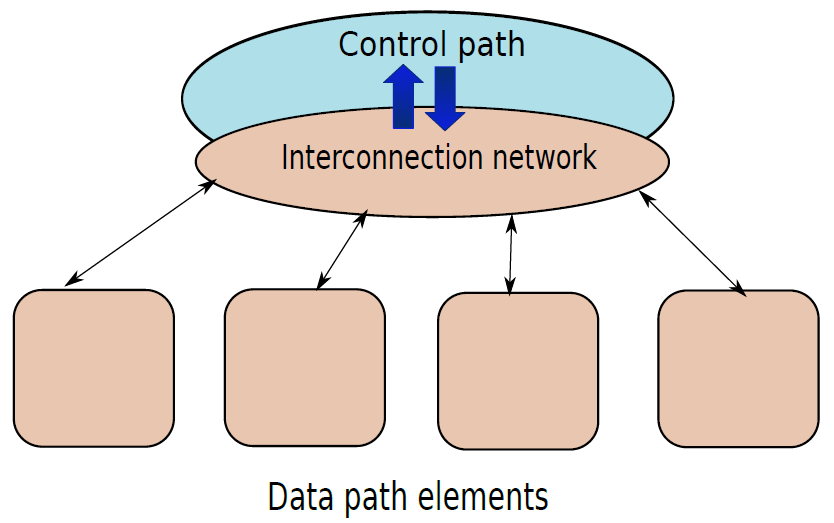

因此,我們可以從概念上認為處理器由兩個不同的子系統組成:

- 資料路徑(data path)。它包含儲存和處理資訊的所有元素。例如,資料記憶體、指令記憶體、暫存器檔案和ALU(算術邏輯單元)是資料路徑的一部分。記憶體和暫存器儲存資訊,而ALU處理資訊,例如,它將兩個數位相加,併產生和作為結果,或者它可以計算兩個數位的邏輯函數。

- 控制路徑(control path)。它通過生成訊號來引導資訊的正確流動,生成一個訊號,指示多路複用器在分支目標和預設下一個PC之間進行選擇。在這種情況下,多路複用器由訊號

isBranchTaken控制。

我們可以將控制路徑和資料路徑視為電路的兩個不同元件,就像城市的交通網路一樣。道路和紅綠燈類似於資料路徑,控制交通燈的電路構成了控制路徑,控制路徑決定燈光轉換的時間。在現代智慧城市中,控制城市中所有交通燈的過程通常是整合的。如果有可能智慧控制交通,使汽車繞過交通堵塞和事故現場。類似地,處理器的控制單元相當智慧,它的工作是儘可能快地執行指令。現代處理器的控制單元已經非常複雜。

資料路徑(data path):資料路徑由處理器中專用於儲存、檢索和處理資料的所有元素組成,如暫存器、記憶體和ALU。

控制路徑(control path):控制路徑主要包含控制單元,其作用是生成適當的訊號來控制資料路徑中指令和資料的移動。

資料路徑和控制路徑之間的關係。

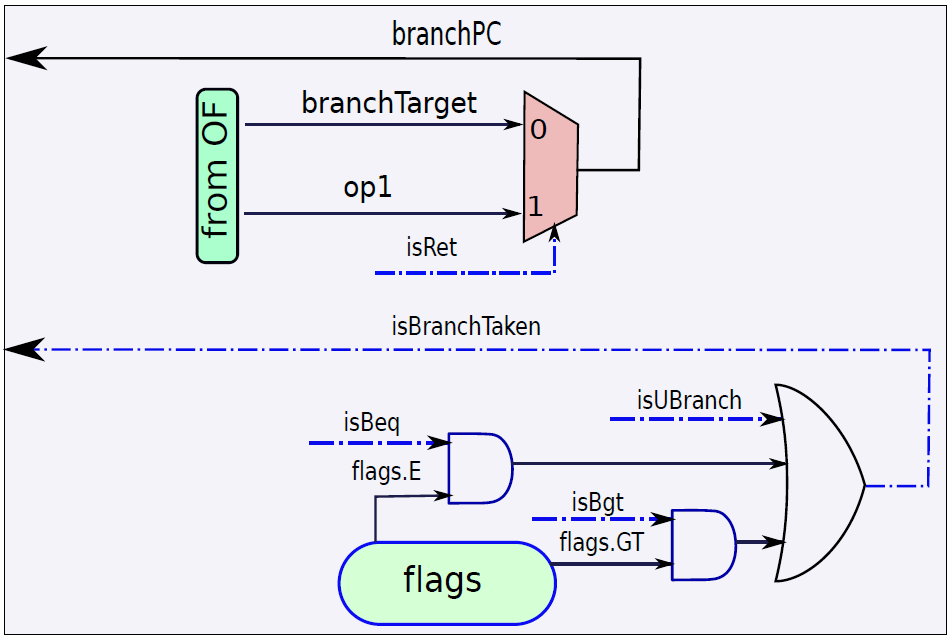

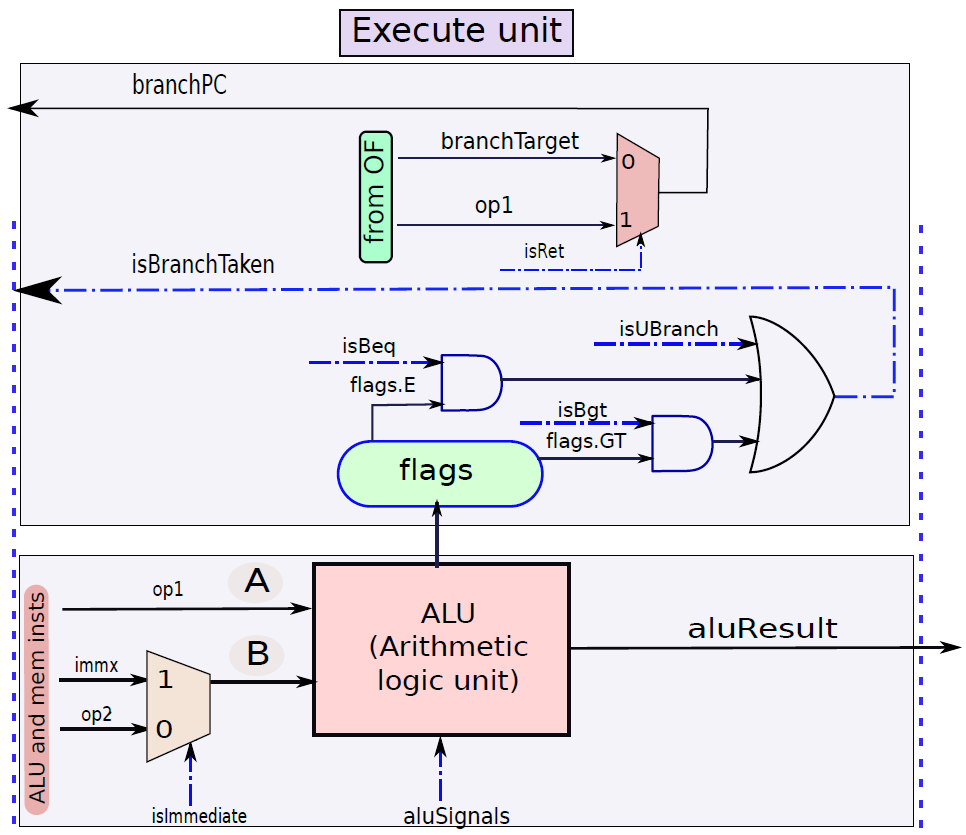

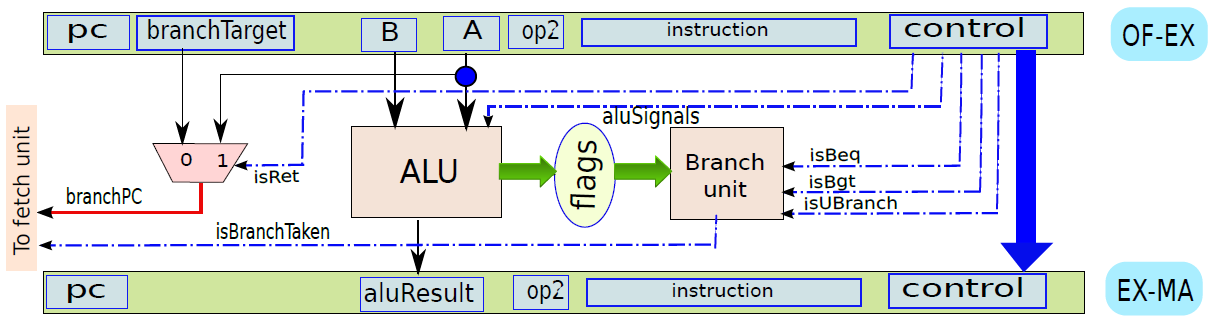

現在看看執行指令。首先將指令分為兩種型別:分支和非分支。分支指令由計算分支結果和最終目標的專用分支單元處理,非分支指令由ALU(算術邏輯單元)處理。分支單元的電路如下圖所示:

使用多路複用器在返回地址(op1)的值和指令中嵌入的branchT目標之間進行選擇。isRet訊號控制多路複用器,如果它等於1就選擇op1,否則選擇分支目標。多路複用器branchPC的輸出被傳送到提取單元。

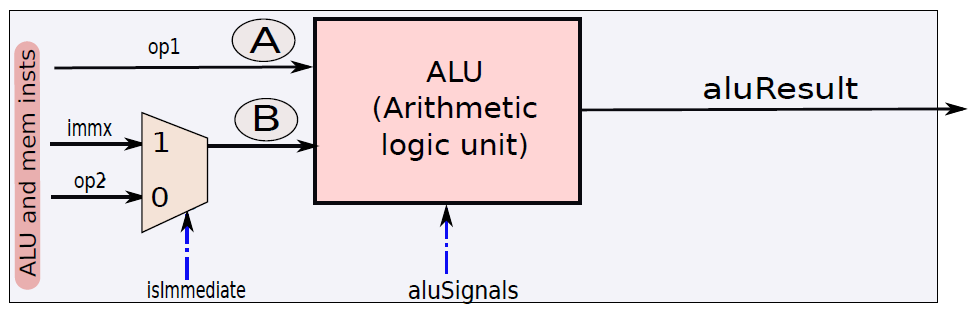

下圖顯示了包含ALU的執行單元部分。ALU的第一個運算元(A)始終為op1(從運算元獲取單元獲得),但第二個運算元(B)可以是暫存器或符號擴充套件立即數,由控制單元生成的isImmediate訊號決定,isImmediate訊號等於指令中立即數位的值,如果是1,則圖中的多路複用器選擇immx作為運算元,如果為0,則選擇op2作為運算元。ALU將一組訊號作為輸入,統稱為aluSignals,aluSignals由控制單元生成,並指定ALU操作的型別。ALU的結果稱為aluResult。

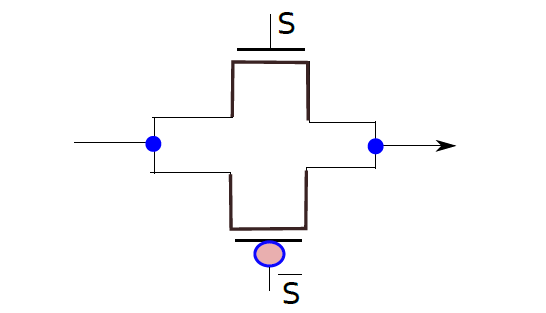

下圖顯示了ALU的一種設計。ALU包含一組模組,每個模組計算單獨的算術或邏輯函數,如加法或除法。其次,每個模組都有一個啟用或禁用它的專用訊號,例如,當我們想執行簡單的加法時,沒有理由啟用除法器。有幾種方法可以啟用或禁用單元,最簡單的方法是為每個輸入位使用一個傳輸門(transmission gate,見下下圖),如果訊號(S)開啟,則輸出反映輸入值。否則,它將保持其以前的值。因此,如果啟用訊號關閉,則模組不會看到新的輸入。因此,它不會耗散功率,並被有效禁用。

ALU。

傳輸門。

總之,下圖展示了執行單元(分支單元和ALU)的完整設計。要設定輸出(aluResult),需要一個多路複用器,可以從ALU中的所有模組中選擇正確的輸出,沒有在圖中顯示此多路複用器。

執行單元(分支和ALU單元)。

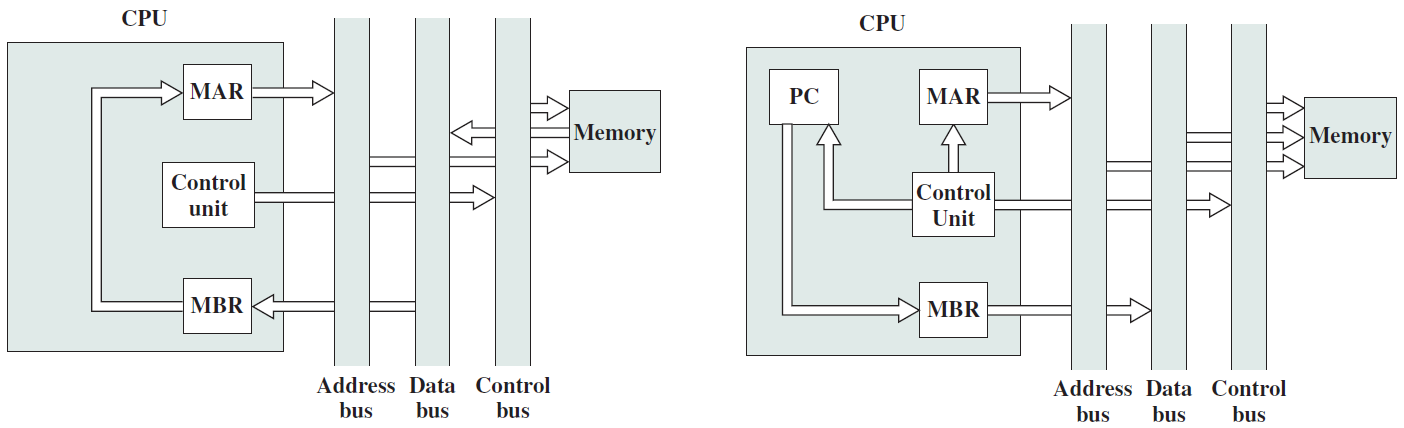

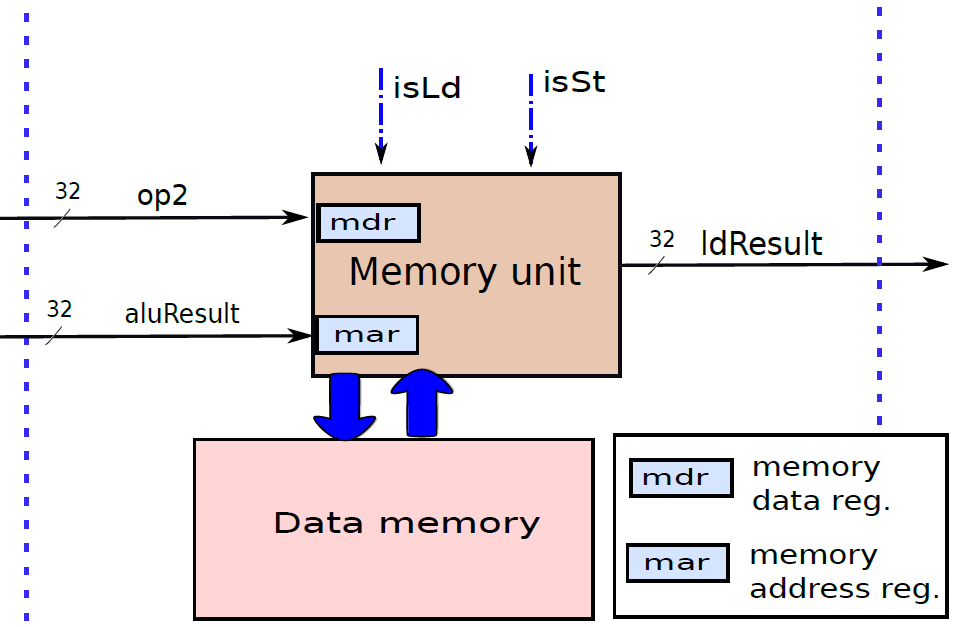

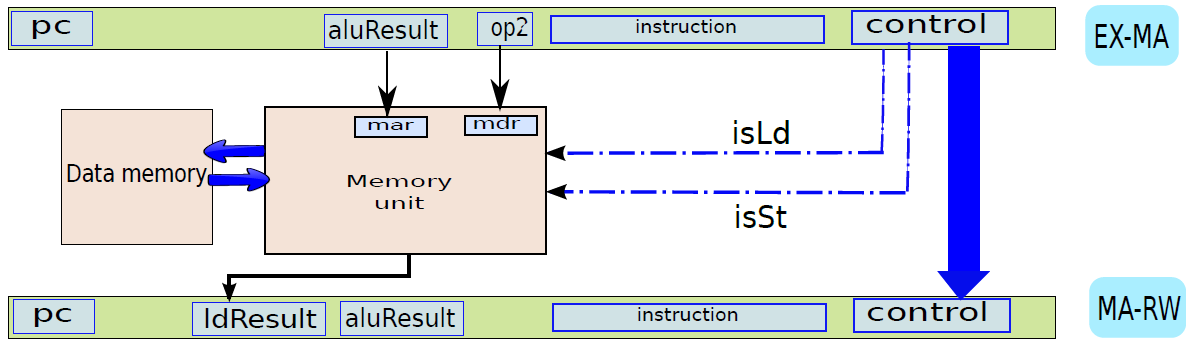

下圖顯示了記憶體存取單元。它有兩個輸入{資料和地址,地址由ALU計算,它等於ALU的結果(aluResult),載入和儲存指令都使用這個地址,地址儲存在傳統上稱為MAR(記憶體地址暫存器)的暫存器中。

記憶體單元。

通過連線所有部分來形成整體。到目前為止,已經將處理器分為五個基本單元:指令獲取單元(IF)、運算元獲取單元(OF)、執行單元(EX)、記憶體存取單元(MA)和暫存器寫回單元(RW)。是時候把所有的部分結合起來,看看統一的圖片了(下圖,省略了詳細的電路,只關注資料和控制訊號的流動)。

一個基礎處理器。

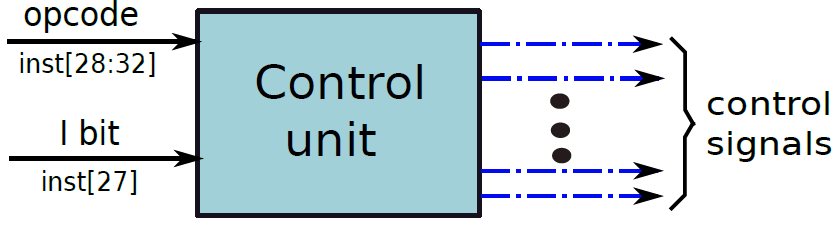

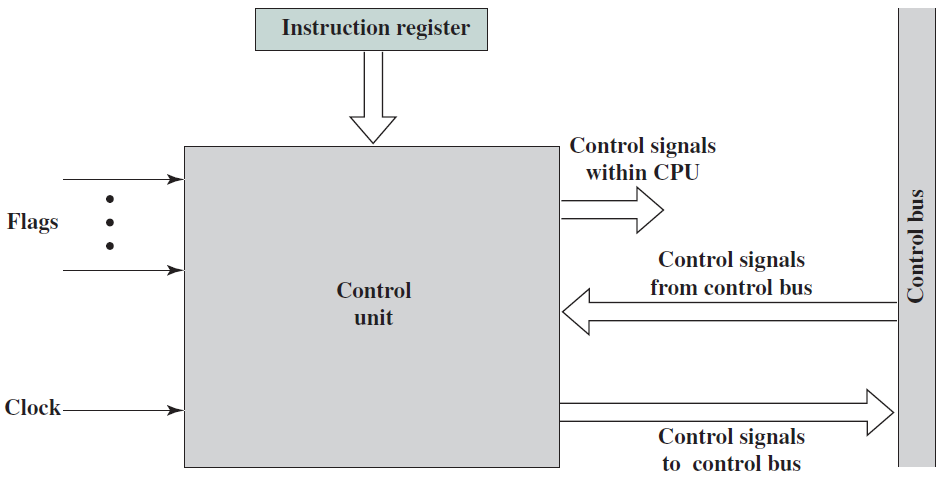

19.5.2.2 控制單元

一個簡單處理器的硬接線控制單元可以被認為是一個黑盒子,它以6位作為輸入(5個操作碼位和1個立即數位),併產生22個控制訊號作為輸出。如下圖所示。

硬接線控制單元的抽象。

控制單元的結構圖。

硬接線控制單元快速高效,這就是今天大多數商用處理器使用硬接線控制單元的原因,但硬接線控制單元並不十分靈活,例如在處理器出廠後,不可能更改指令的行為,甚至不可能引入新指令。有時如果功能單元中存在錯誤,需要更改指令的執行方式,例如如果乘法器存在設計缺陷,那麼理論上可以使用加法器和移位單元執行布斯乘法演演算法。然而,我們需要一個非常複雜的控制單元來動態地重新設定指令的執行方式。

支援靈活的控制單元還有其他更實際的原因。某些指令集(如x86)具有重複指令給定次數的rep指令,它們還具有複雜的字串指令,可以處理大量資料,支援此類指令需要非常複雜的資料路徑。原則上,我們可以通過精心設計的控制單元來執行這些指令,而這些控制單元又有簡單的處理器來處理這些指令,這些子處理器可以生成用於實現複雜CISC指令的控制訊號。

資料路徑和控制訊號。

帶內部匯流排的CPU。

19.5.2.3 基於微程式的處理器

前面已經研究了帶有硬接線控制單元的處理器,設計了一個包含處理和執行指令所需的所有元素的資料路徑。在輸入運算元之間有選擇的地方,新增了一個多路複用器,它由來自控制單元的訊號控制。控制單元將指令的內容作為輸入,並生成所有控制訊號。現代高效能處理器通常採用這種設計風格。請注意,效率是有代價的,成本是靈活性。我們可能需要新增更多的多路複用器,併為每個新指令生成更多的控制訊號。其次,在處理器交付給客戶後,不可能向處理器新增新指令。有時候,我們渴望這樣的靈活性。

通過引入將ISA中的指令轉換為一組簡單微指令的轉換表,可以引入這種額外的靈活性。每個微指令都可以存取處理器的所有鎖存器和內部狀態元素。通過執行一組與指令關聯的微指令,我們可以實現該指令的功能,這些微指令或微程式碼儲存在微程式碼錶中。通常可以通過軟體修改該表的內容,從而改變硬體執行指令的方式。有幾個原因需要這種靈活性,允許我們新增新指令或修改現有指令的行為。其中一些原因如下:

- 處理器在執行某些指令時有時會出現錯誤。因為設計師在設計過程中犯下的錯誤,或者是由於製造缺陷,其中一個著名的例子是英特爾奔騰處理器中的除法錯誤,英特爾不得不召回它賣給客戶的所有奔騰處理器。如果可以動態地更改除法指令的實現,那麼就不必呼叫所有處理器。因此可以得出結論,處理器的某種程度的可重構性有助於解決在設計和製造過程的各個階段可能引入的缺陷。

- 英特爾奔騰4等處理器,以及英特爾酷睿i3和英特爾酷睿i7等更高版本的處理器,通過執行儲存在記憶體中的一組微指令來實現一些複雜的指令。通常使用微碼來實現資料串或指令的複雜操作,這些操作會導致一系列重複計算,意味著英特爾處理器在內部將複雜指令替換為包含簡單指令的程式碼段,使得處理器更容易實現複雜的指令。我們不需要對資料路徑進行不必要的更改,新增額外的狀態、多路複用器和控制訊號來實現複雜的指令。

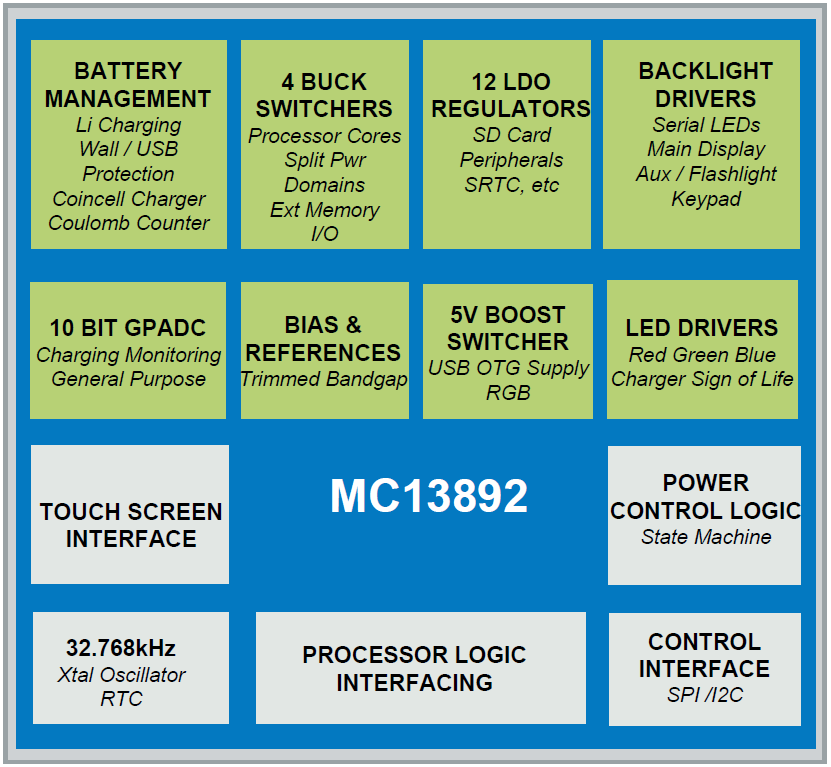

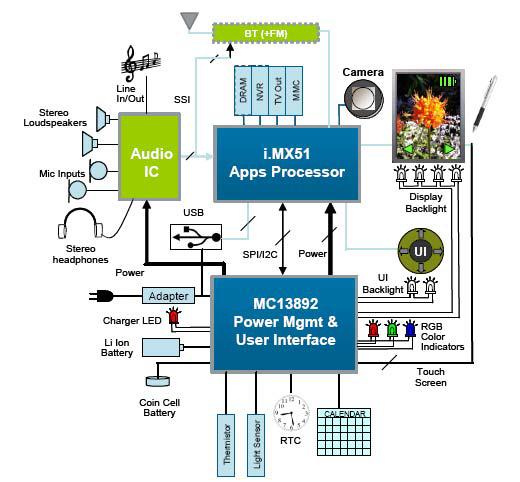

- 當今的處理器只是晶片的一部分,有許多其他元件,被稱為片上系統(system-on-chip,SOC)。例如,手機中的晶片可能包含處理器、視訊控制器、相機介面、聲音和網路控制器。處理器供應商通常會硬連線一組簡單的指令,而與視訊和音訊控制器等外圍裝置介面的許多其他指令都是用微碼編寫的。根據應用程式域和外圍元件集,可以客製化微碼。

- 有時使用一組專用微指令編寫自定義診斷例程。這些例行程式在晶片執行期間測試晶片的不同部分,報告故障並採取糾正措施。這些內建自檢(BIST)例程通常是可客製化的,並以微碼編寫。例如,如果我們希望高可靠性,那麼我們可以修改在CPU上執行可靠性檢查的指令的行為,以檢查所有元件。但是,為了節省時間,可以壓縮這些例程以檢查更少的元件。

因此,我們觀察到,有一些令人信服的理由能夠以程式設計方式改變處理器中指令的行為,以實現可靠性、實現附加功能並提高可移植性。因此,現代計算系統,尤其是手機和平板電腦等小型裝置使用的晶片依賴於微碼。這種微碼序列通常被稱為韌體。

現代計算系統,尤其是手機、資料機、印表機和平板電腦等小型裝置,使用的晶片依賴於微碼。這種微碼序列通常被稱為韌體(firmware)。

因此,讓我們設計一個基於微程式的處理器,即使在處理器被製造並行送給客戶之後,它也能為我們提供更大的靈活性來客製化指令集。需要注意,常規硬接線處理器和微程式設計處理器之間存在著基本的權衡。權衡是效率與靈活性,不能指望有一個非常靈活的處理器,它既快速又省電。

19.5.2.4 微程式設計資料路徑

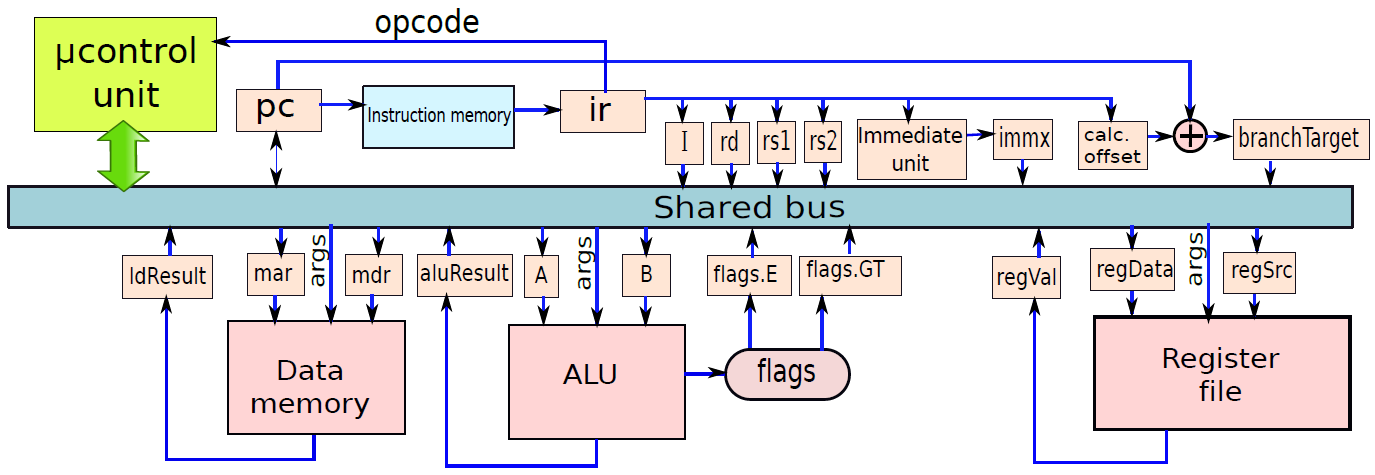

讓我們為微程式處理器設計資料路徑,修改處理器的資料路徑。處理器有一些主要單元,如提取單元、暫存器檔案、ALU、分支單元和記憶體單元。這些單元是用導線連線的,只要有可能有多個源運算元,我們就在資料路徑中新增一個多路複用器。控制單元的作用是為多路複用器生成所有控制訊號。

問題是多路複用器的連線是硬接線的,不能建立任意連線,例如,不能將儲存單元的輸出傳送到執行單元的輸入。因此我們希望有一個元件之間沒有固定互連的設計,理論上任何單位都可以向任何其他單位傳送資料。

最靈活的互連是基於匯流排的結構。匯流排是一組連線所有單元的普通銅線,支援一個寫入,在任何時間點支援多個讀者。例如,單元A可以在某個時間點寫入匯流排,所有其他單元都可以獲得單元A寫入的值。如果需要,可以將資料從一個單元傳送到另一個單元,或從一個裝置傳送到一組其他單元。控制單元需要確保在任何時間點,只有一個單元寫入匯流排,需要處理正在寫入的值的單元從匯流排讀取值。

現在讓我們繼續設計我們為硬連線處理器引入的所有單元的簡化版本,這些簡化版本可以適當地用於我們的微程式處理器的資料路徑。

讓我們從解釋微程式處理器的設計原理開始。我們為每個單元新增暫存器,這些暫存器儲存特定單元的輸入資料,專用輸出暫存器儲存單元生成的結果,這兩組暫存器都連線到公共匯流排。與硬連線處理器不同的是,在不同的單元之間存在大量的耦合,微程式處理器中的單元是相互獨立的。他們的工作是執行一組操作,並將結果返回匯流排。每個單元就像程式語言中的一個函數,它有一個由一組暫存器組成的介面,用於讀取資料,通常需要1個週期來計算其輸出,然後該單元將輸出值寫入輸出暫存器。

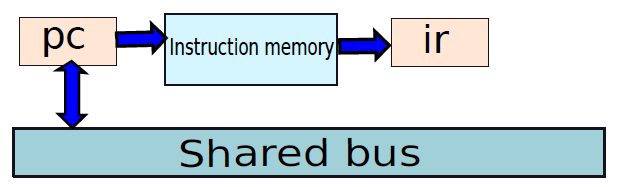

根據上述原理,下圖中展示了提取單元的設計,它有兩個暫存器:pc(程式計數器)和ir(指令暫存器)。pc暫存器可以從匯流排讀取其值,也可以將其值寫入匯流排,沒有將ir連線到匯流排,因為沒有其他單位對指令的確切內容感興趣,其他單位只對指令的不同欄位感興趣。因此,有必要解碼指令並將其分解為一組不同的欄位,由解碼單元完成。

微程式處理器中的提取單元。

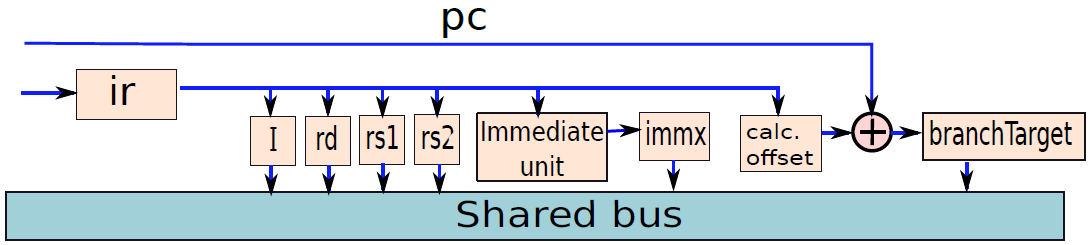

解碼單元在功能上類似於運算元獲取單元,但我們不在該單元中包含暫存器檔案,而將其視為微程式處理器中的一個獨立單元。下圖顯示了運算元獲取單元的設計。

微程式處理器中的解碼單元。

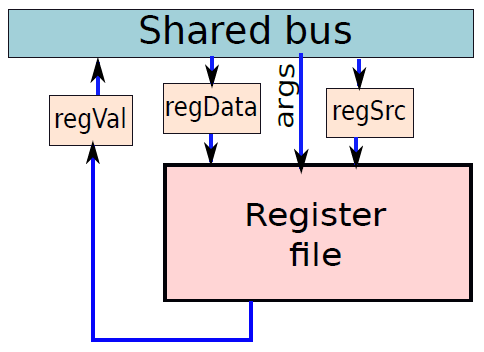

我們將解碼單元和暫存器檔案組合成一個單元,稱為硬連線處理器的運算元獲取單元,但更期望在微程式處理器中保持暫存器檔案獨立,因為在硬連線處理器中,它在解碼指令後立即被存取。然而,微程式處理器可能不是這樣——在指令執行期間,可能需要多次存取它。

微程式處理器中的暫存器檔案。

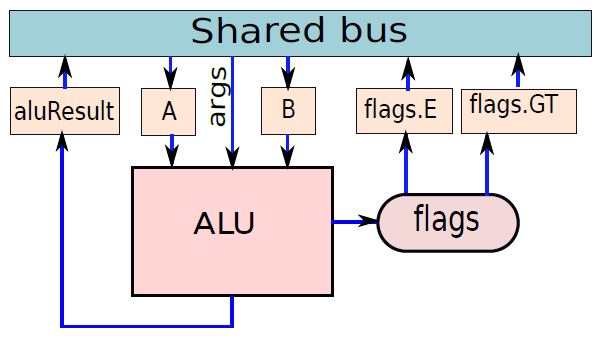

ALU的結構如下圖所示,有兩個輸入暫存器,A和B。ALU對暫存器A和B中包含的值執行操作,操作的性質由args值指定。例如,如果指定了加法運算,則ALU將暫存器A和B中包含的值相加。如果指定了減法運算,那麼將從A中包含的數值減去B中的值,對於cmp指令,ALU更新標誌。使用兩個標誌來指定相等和大於條件,分別儲存在暫存器標誌flags.E和標誌flags.GT中,然後ALU運算的結果儲存在暫存器aluResult中。此處還假設ALU在匯流排上指定args值後需要1個週期才能執行。

微程式處理器中的ALU。

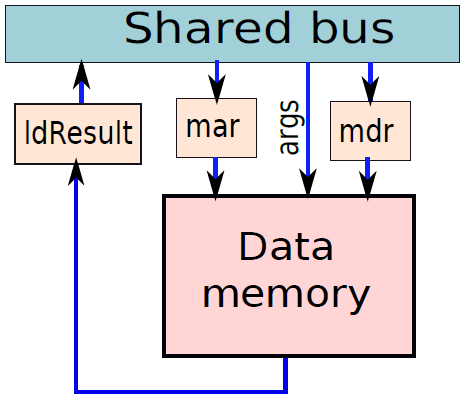

記憶體單元如下圖所示。與硬連線處理器一樣,它有兩個源暫存器:mar(記憶體地址暫存器)和mdr(記憶體資料暫存器),mar緩衝記憶體地址,mdr緩衝需要儲存的值。還需要一組引數來指定記憶體操作的性質:載入或儲存,載入操作完成後,ldResult暫存器中的資料可用。

微程式處理器中的儲存單元。

綜上,微程式處理器中的資料路徑總覽如下:

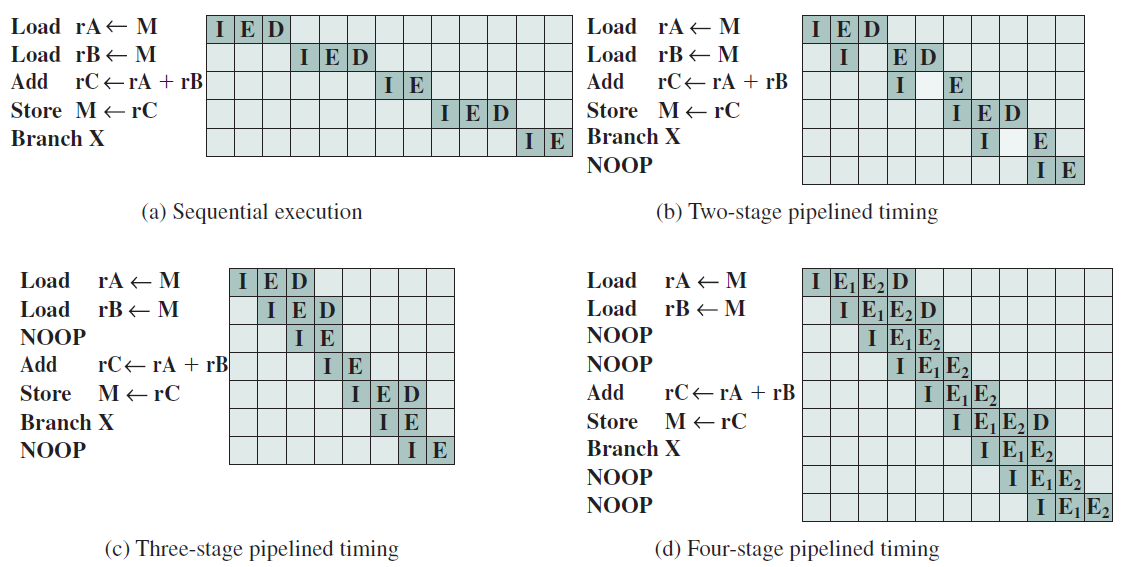

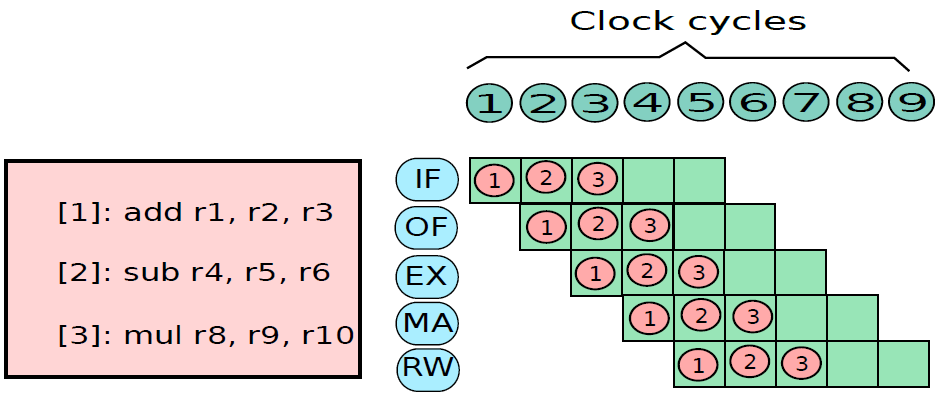

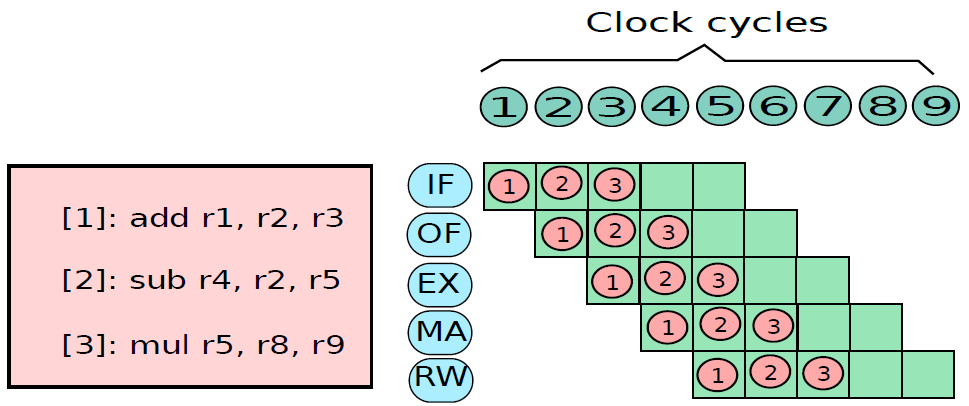

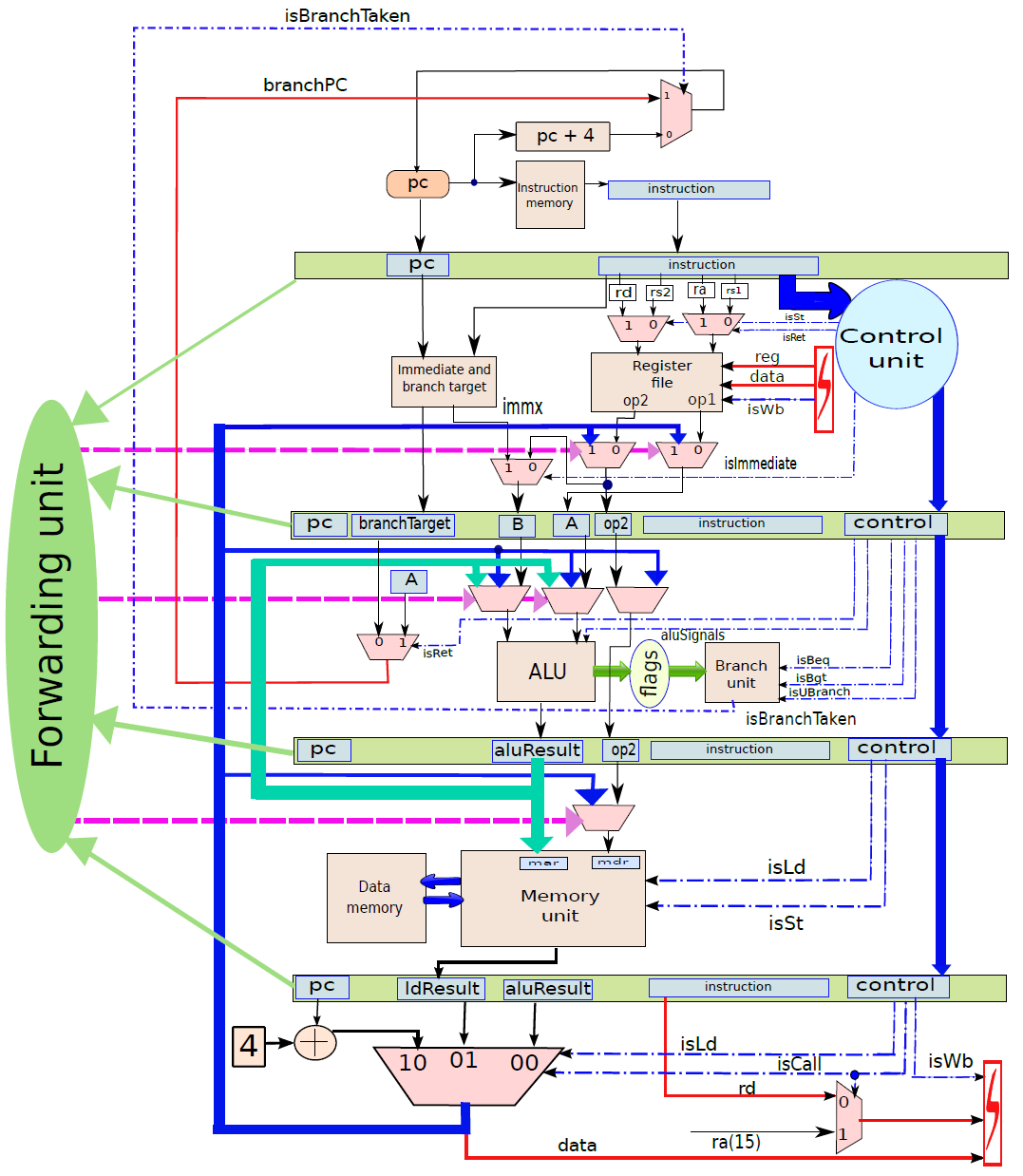

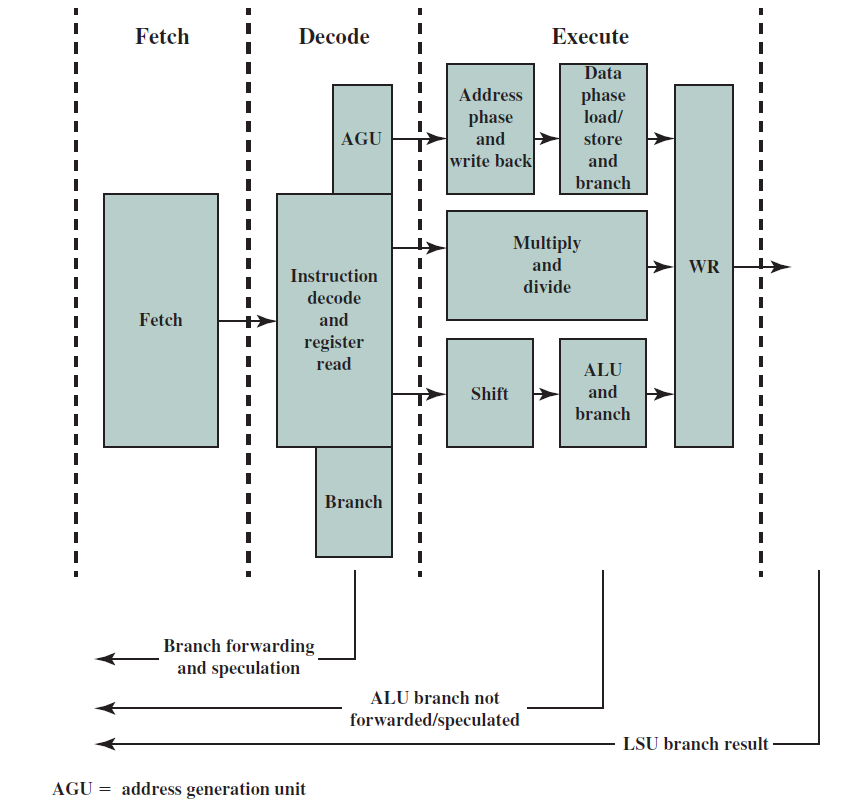

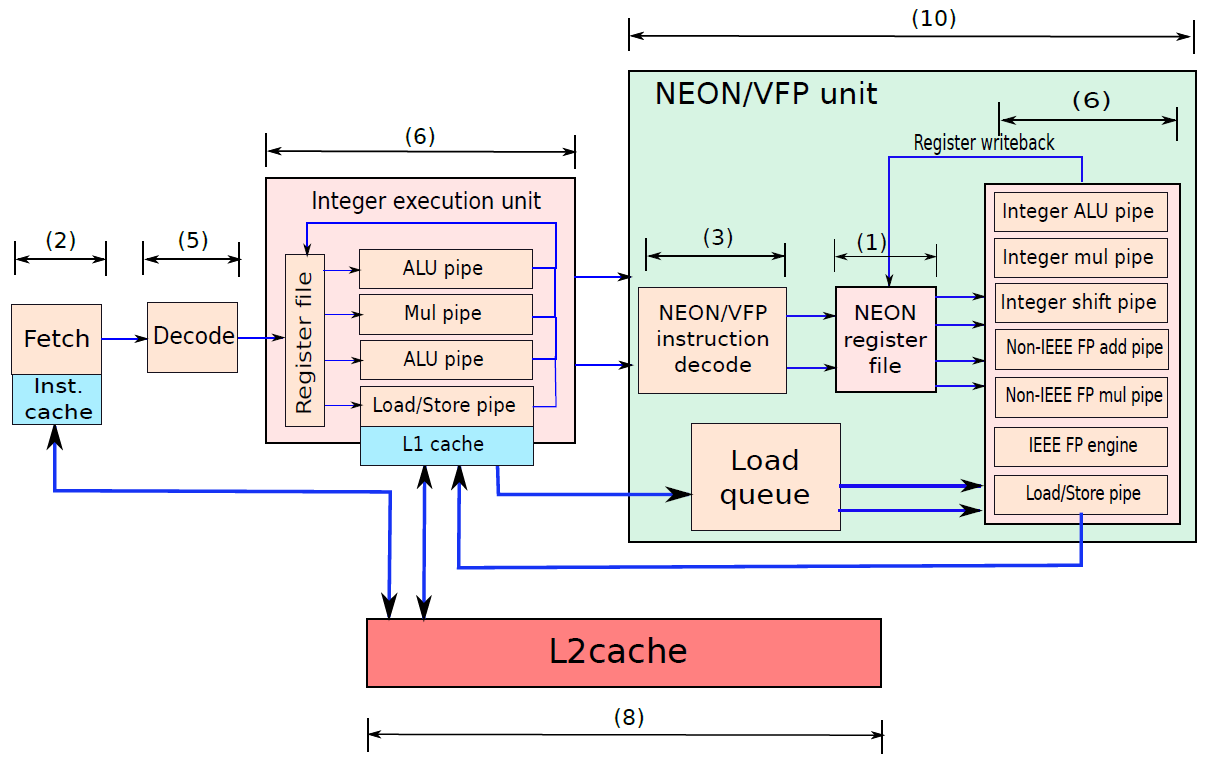

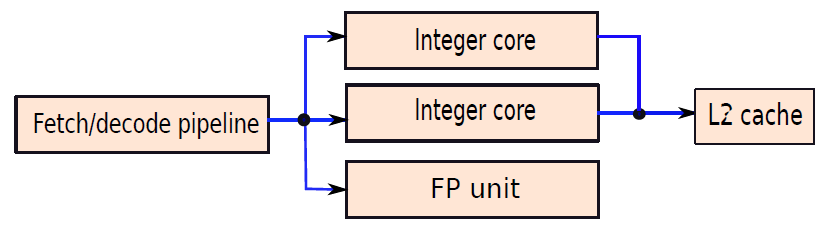

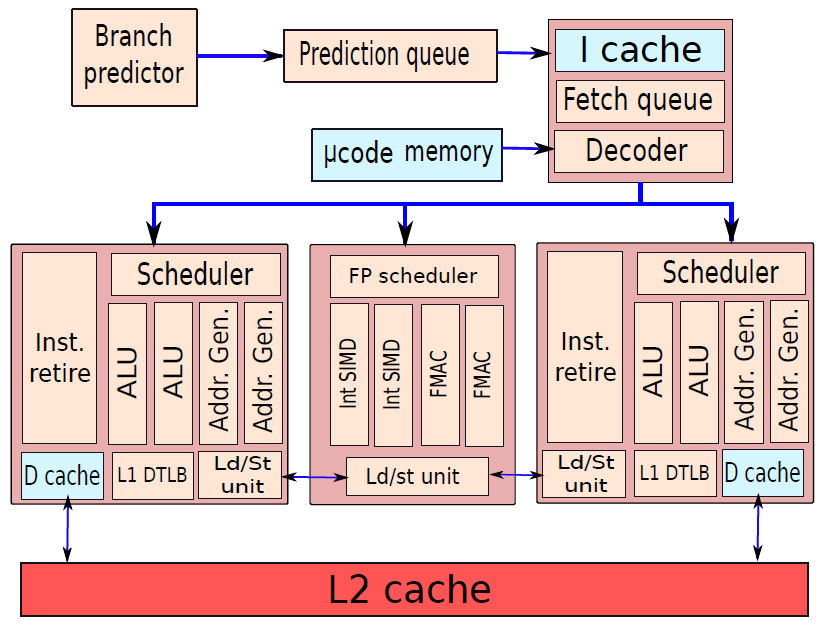

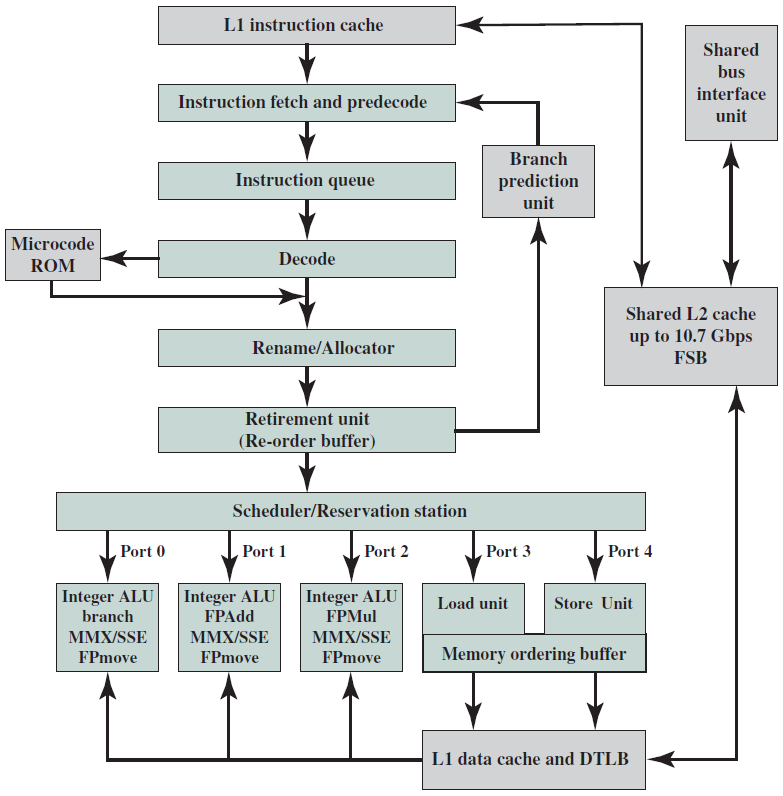

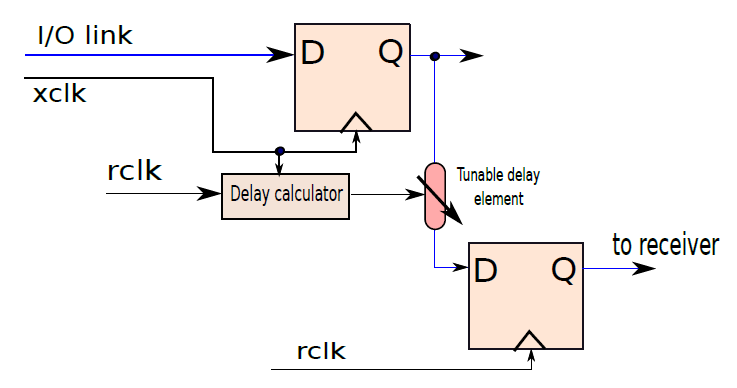

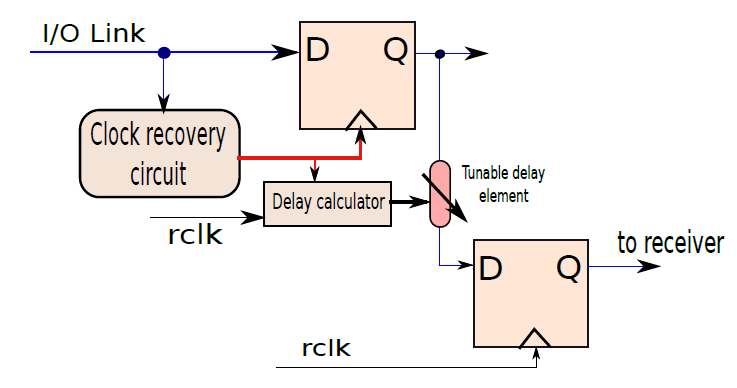

19.5.3 管線處理器

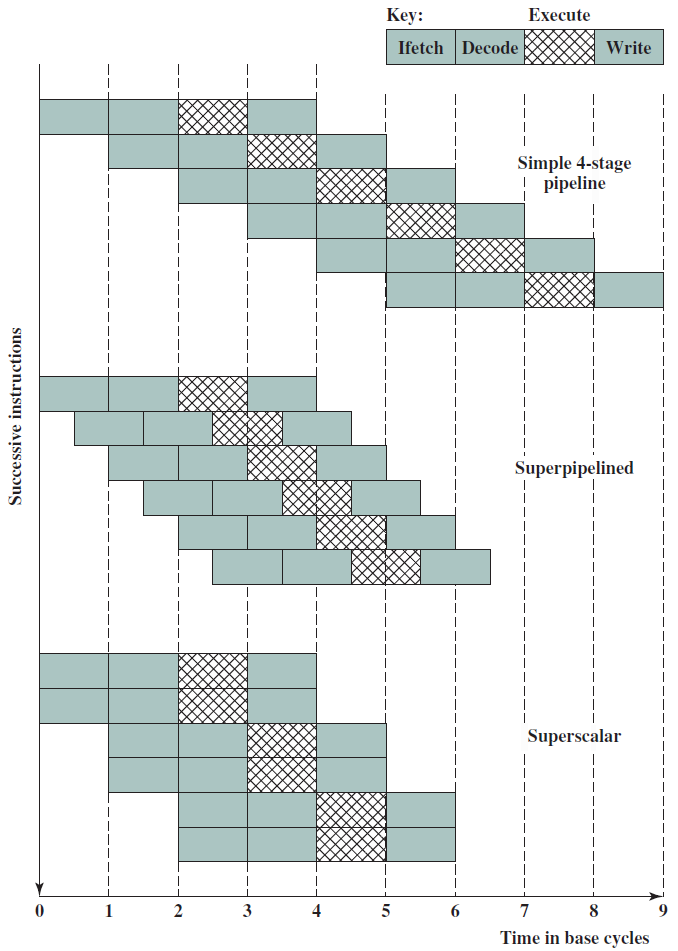

19.5.3.1 管線概述

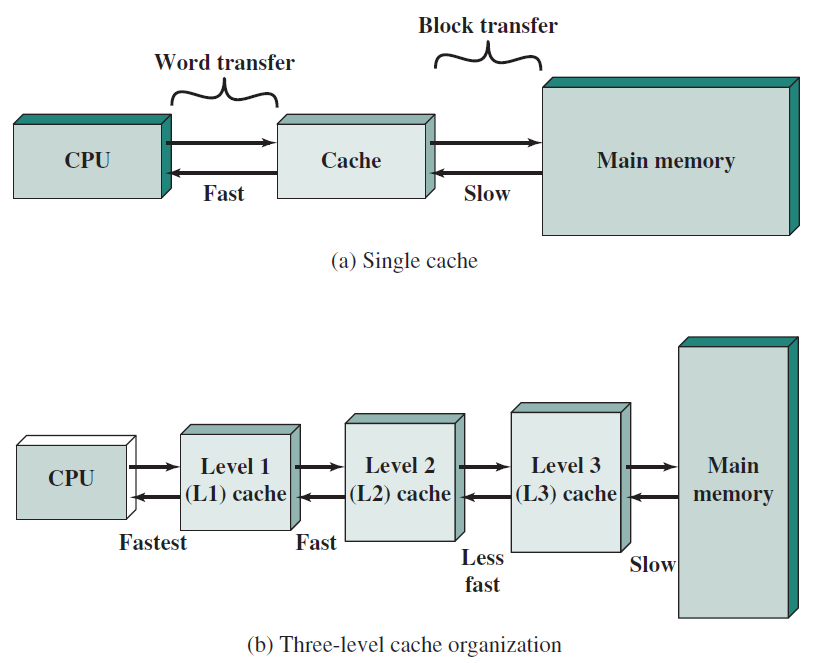

假設前面介紹的硬連線處理器需要一個週期來獲取、執行和將指令的結果寫入暫存器檔案或記憶體。在電氣層面上,是通過從提取單元經由其他單元流到暫存器寫回單元的訊號來實現的,而電訊號從一個單元傳播到另一個單元需要時間。

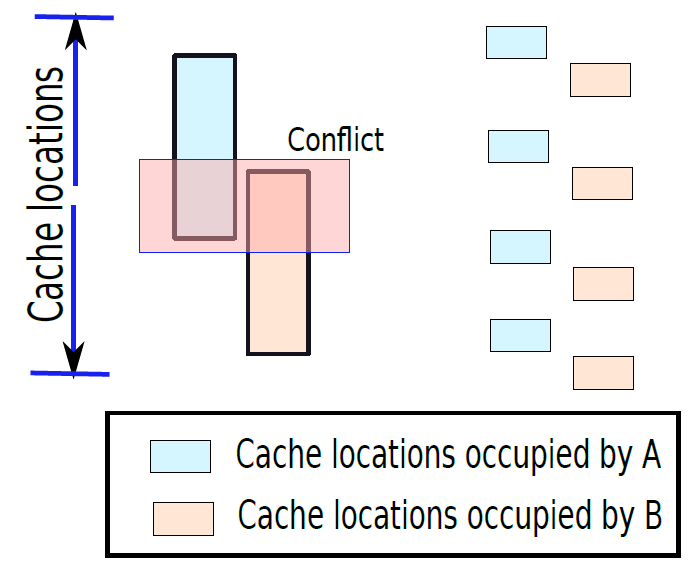

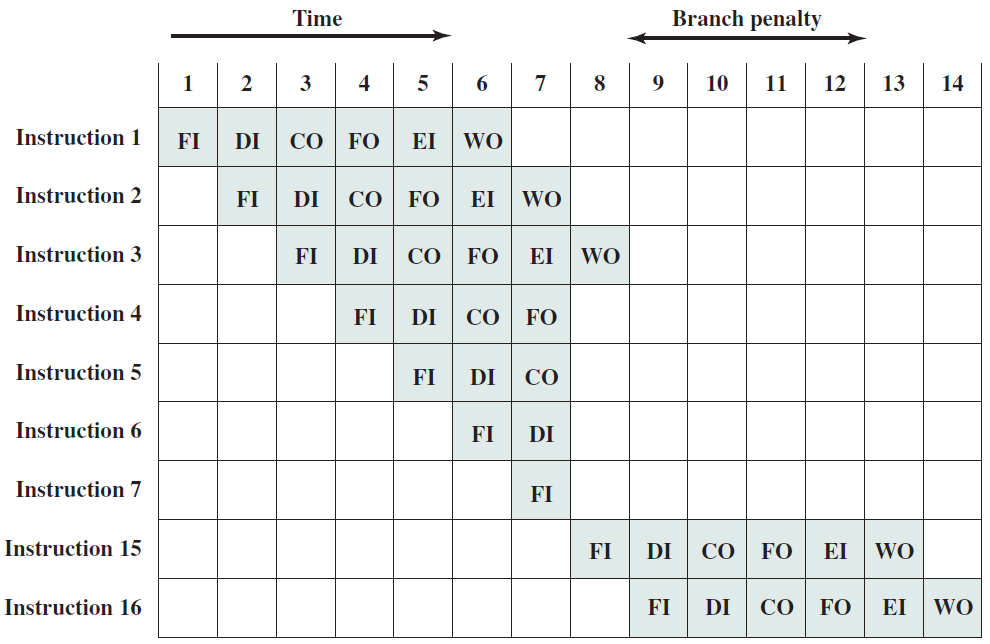

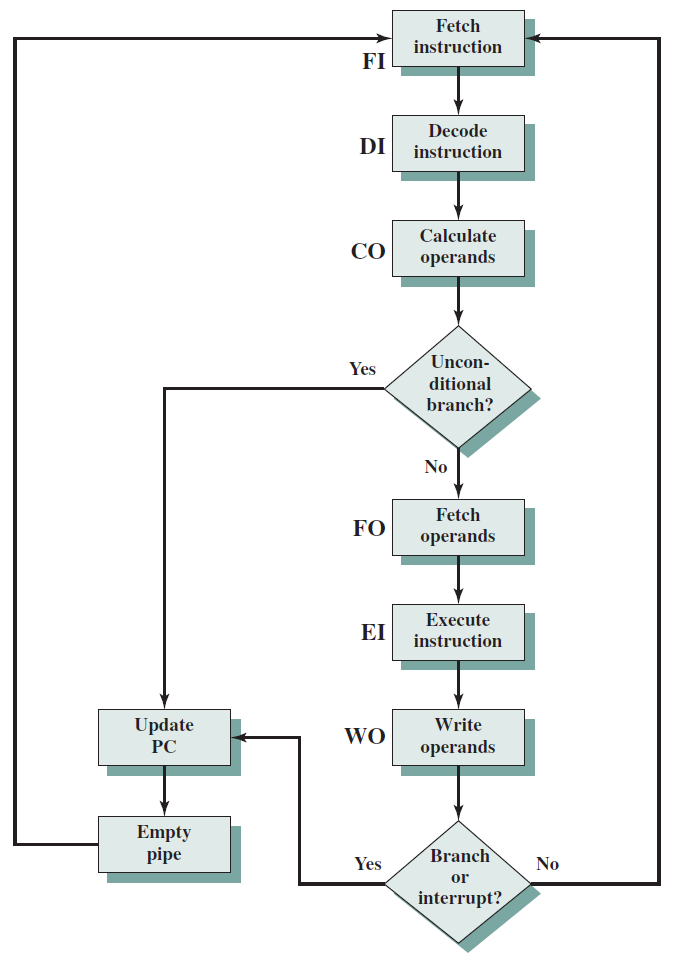

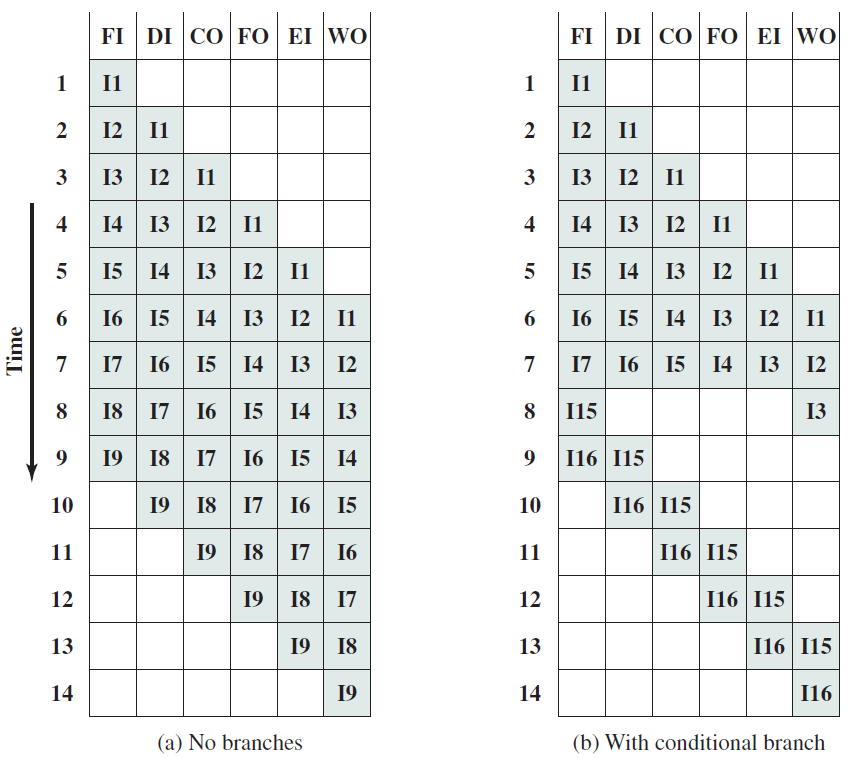

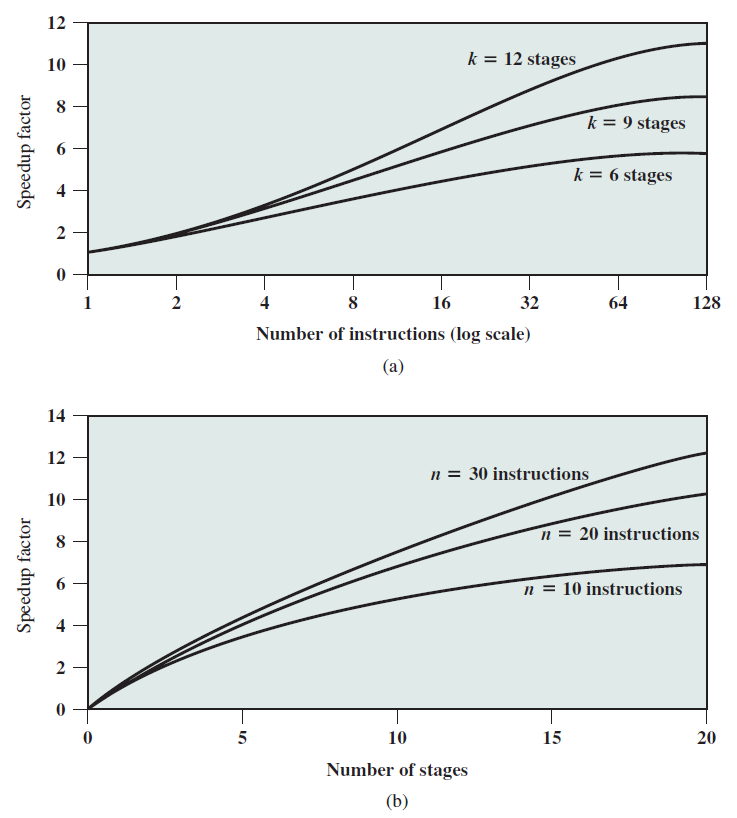

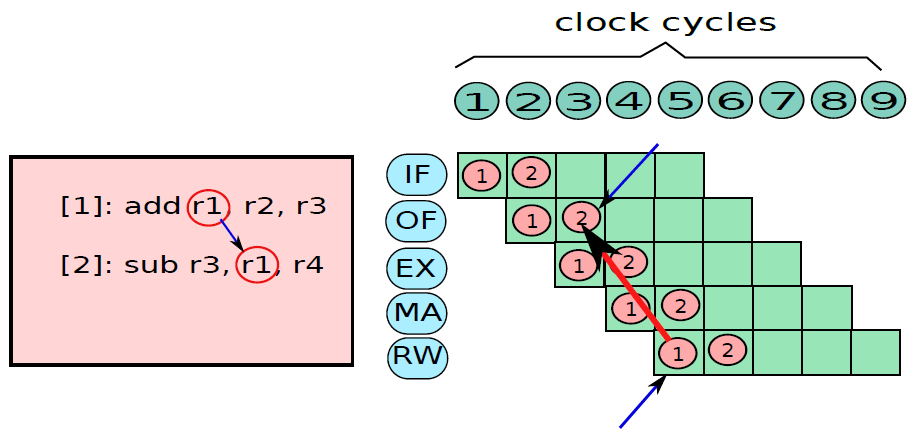

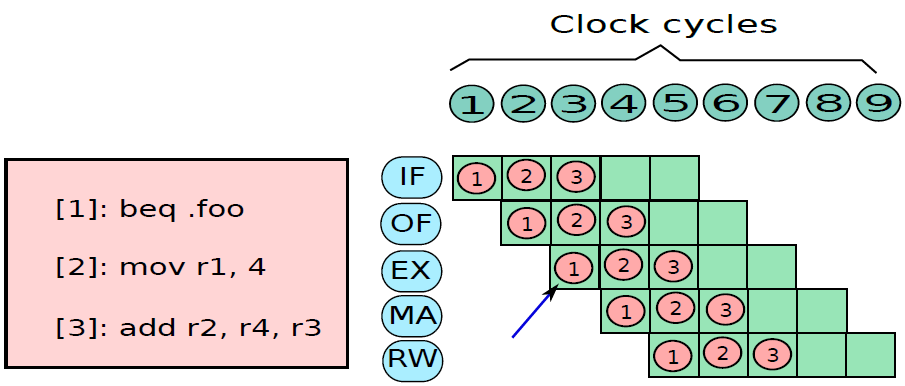

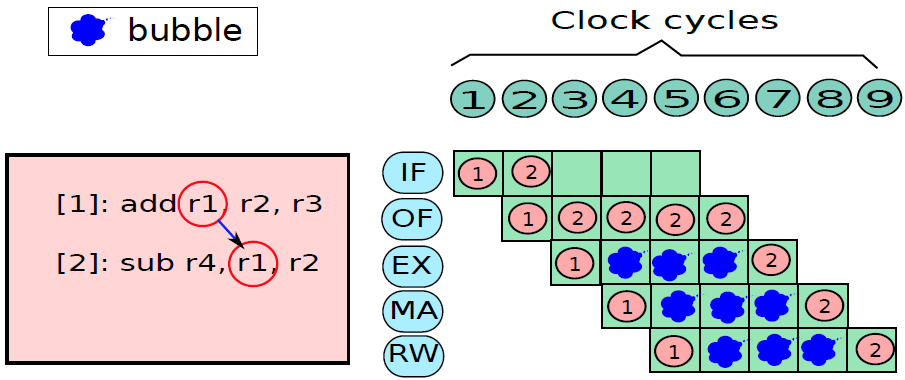

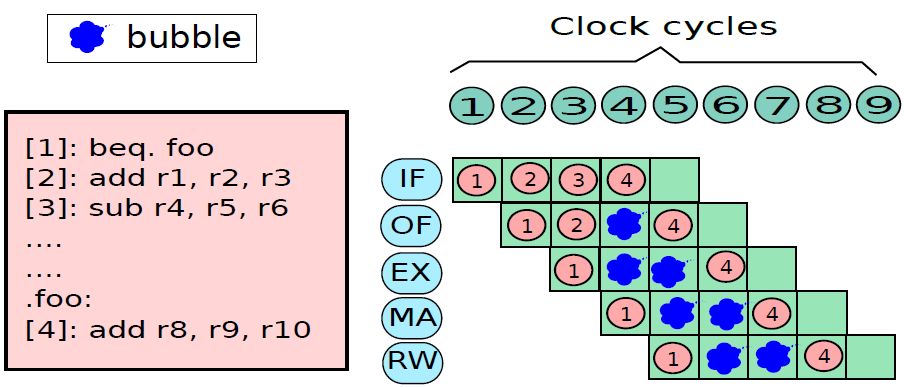

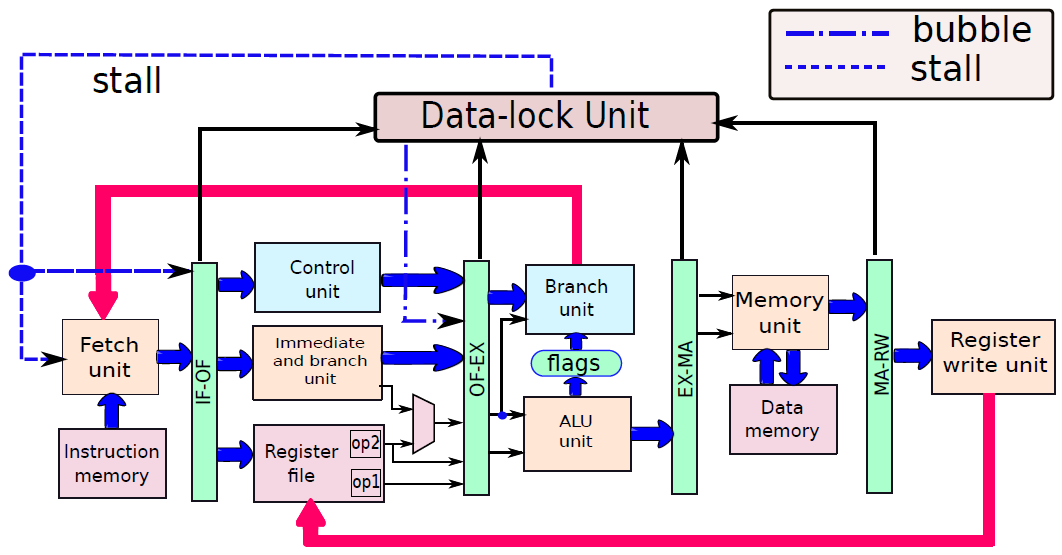

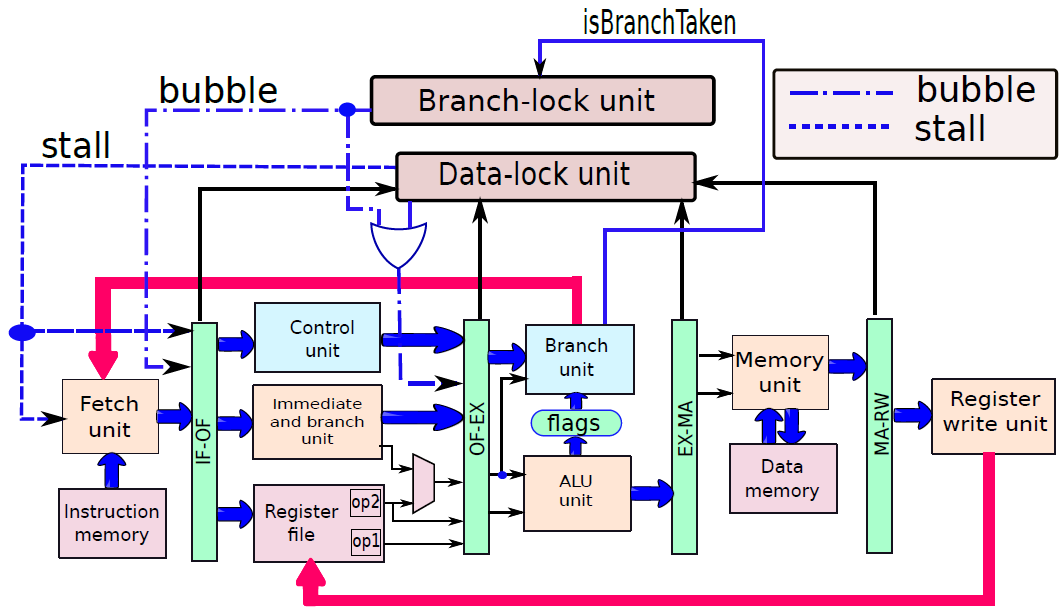

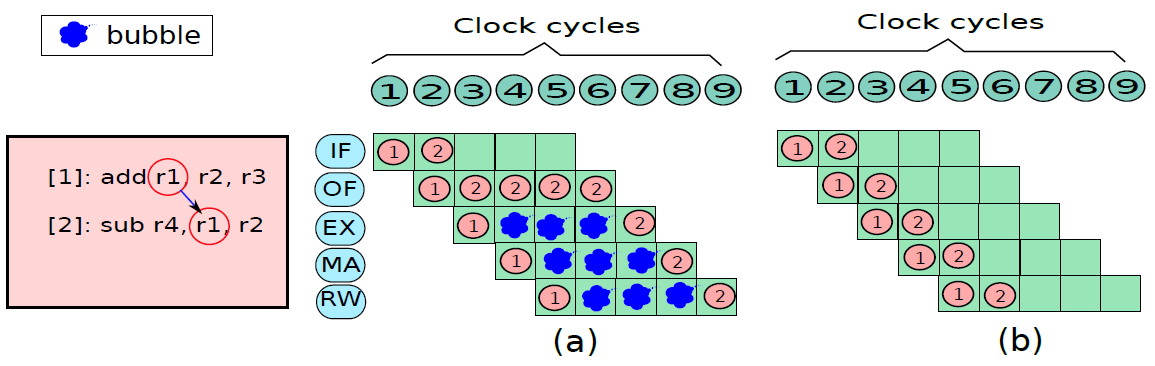

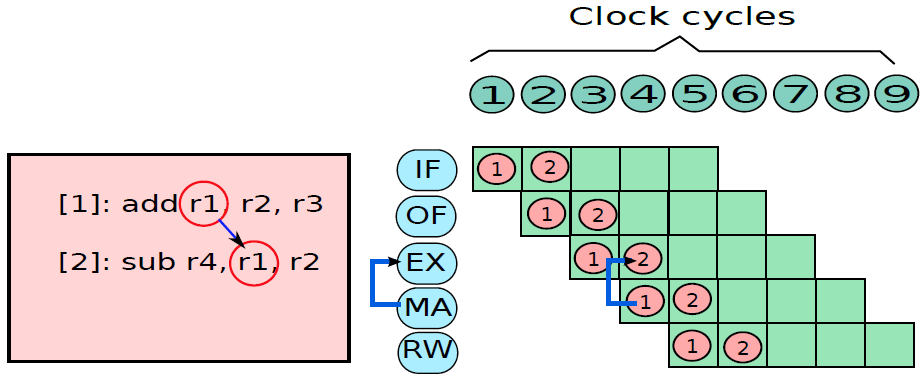

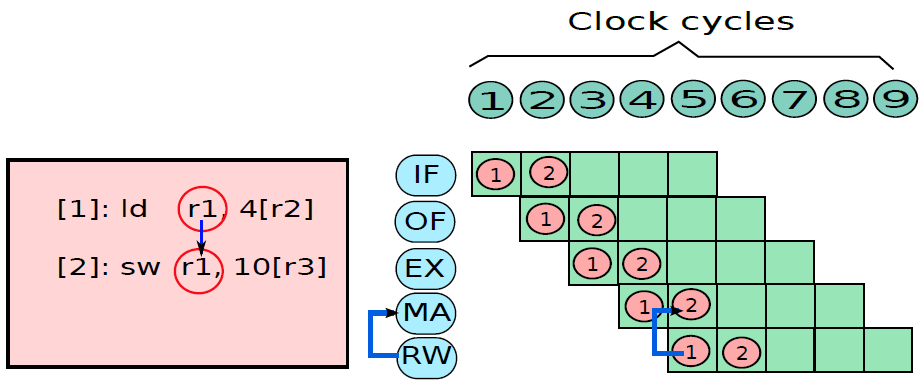

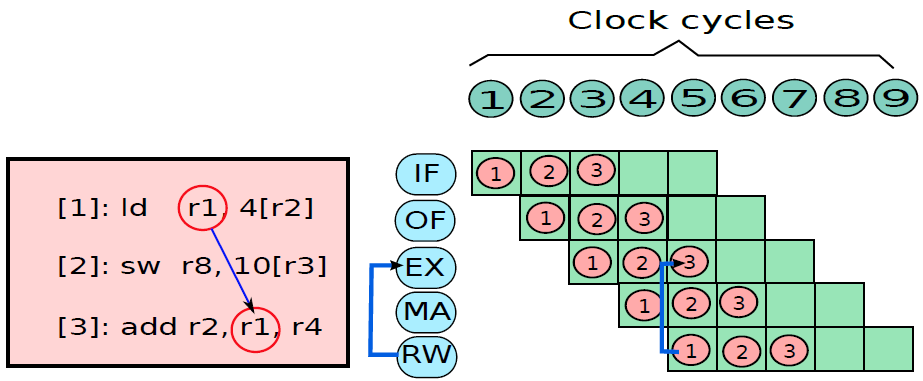

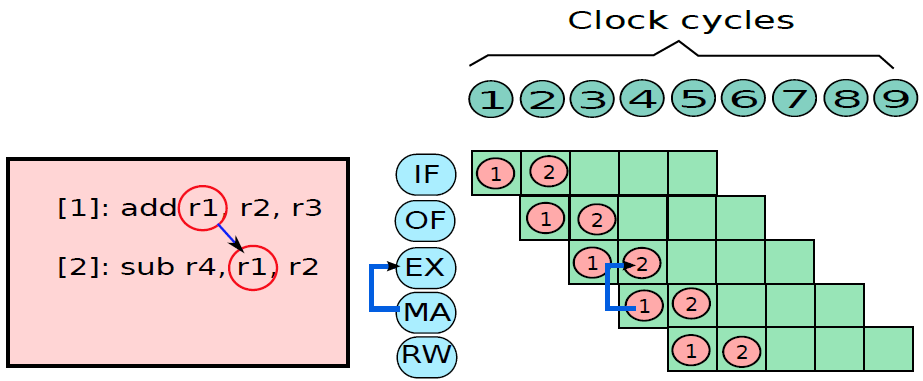

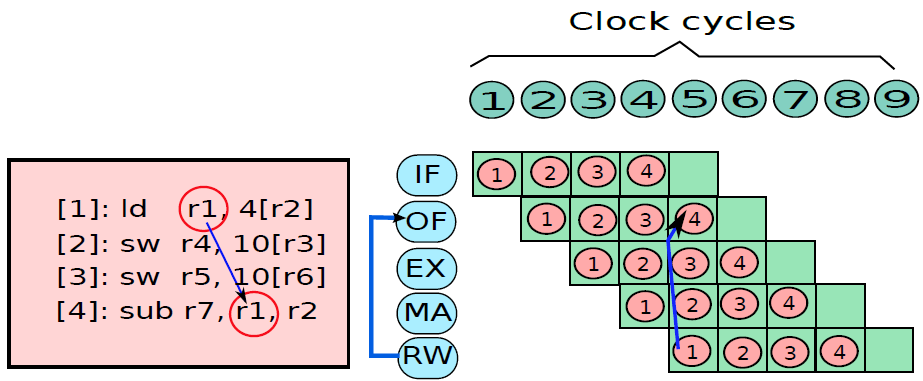

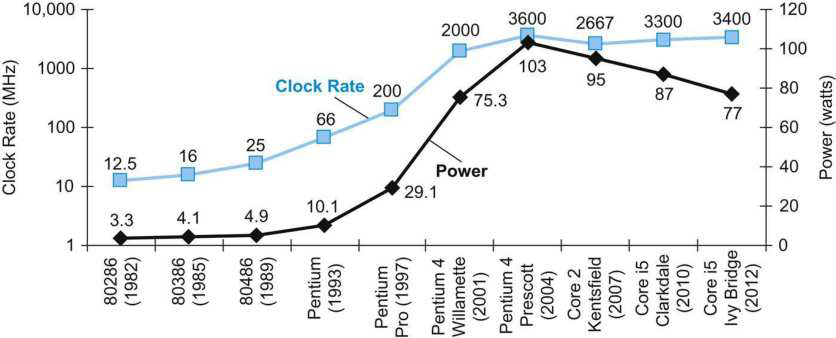

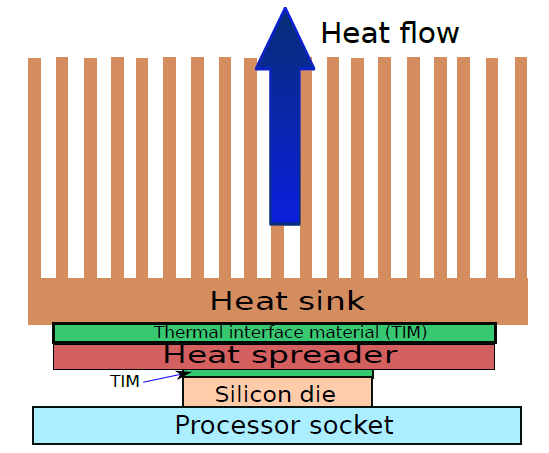

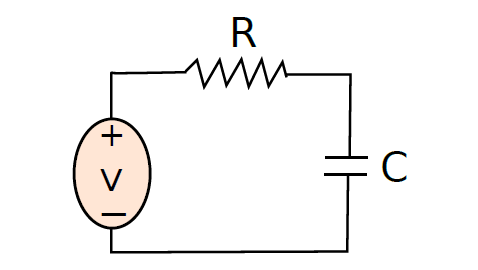

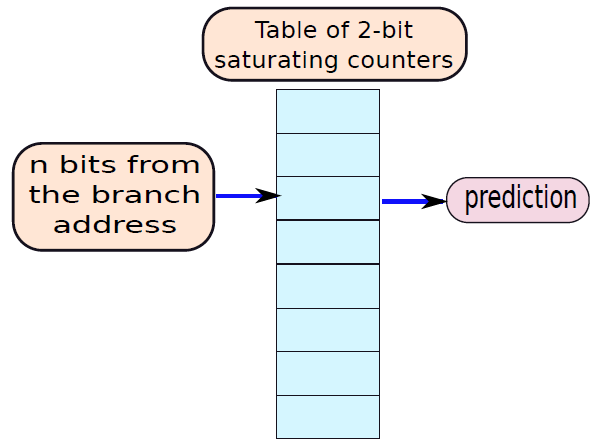

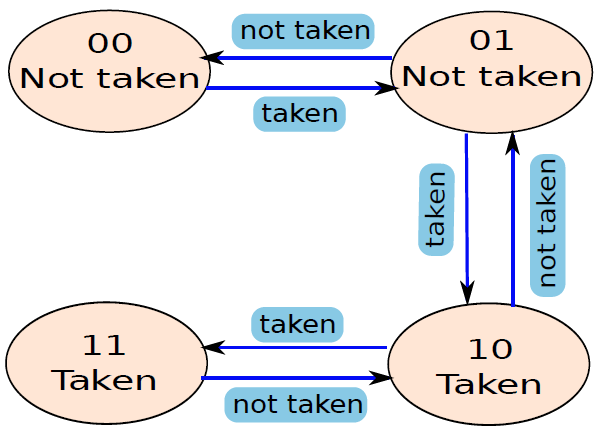

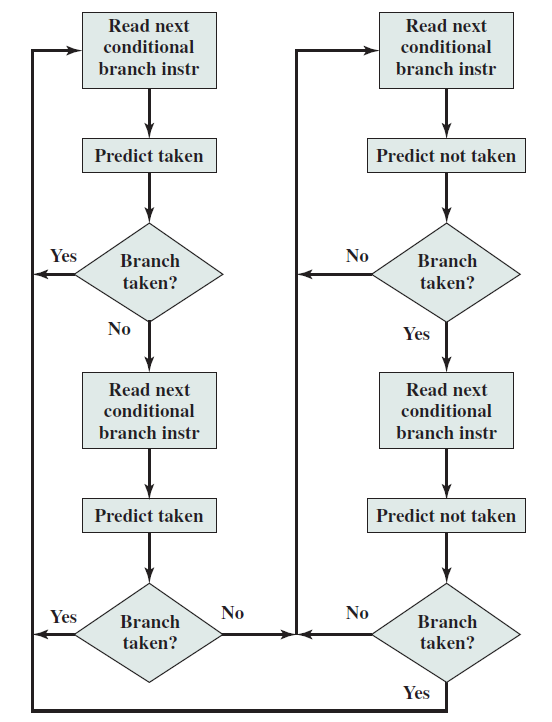

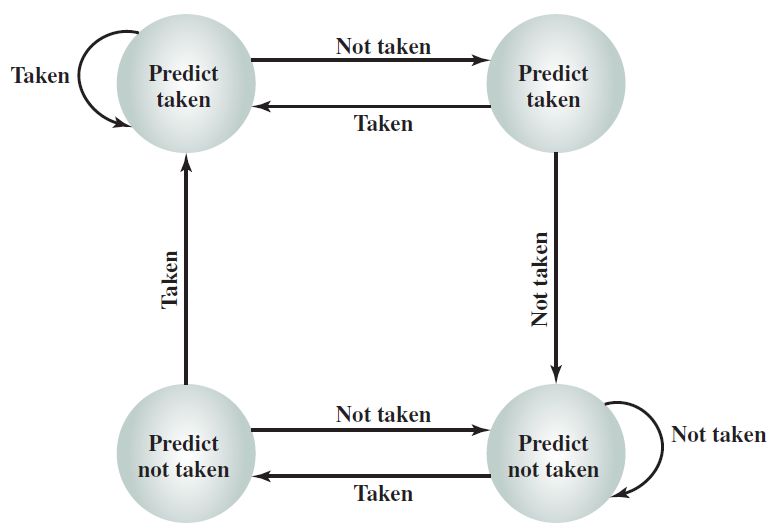

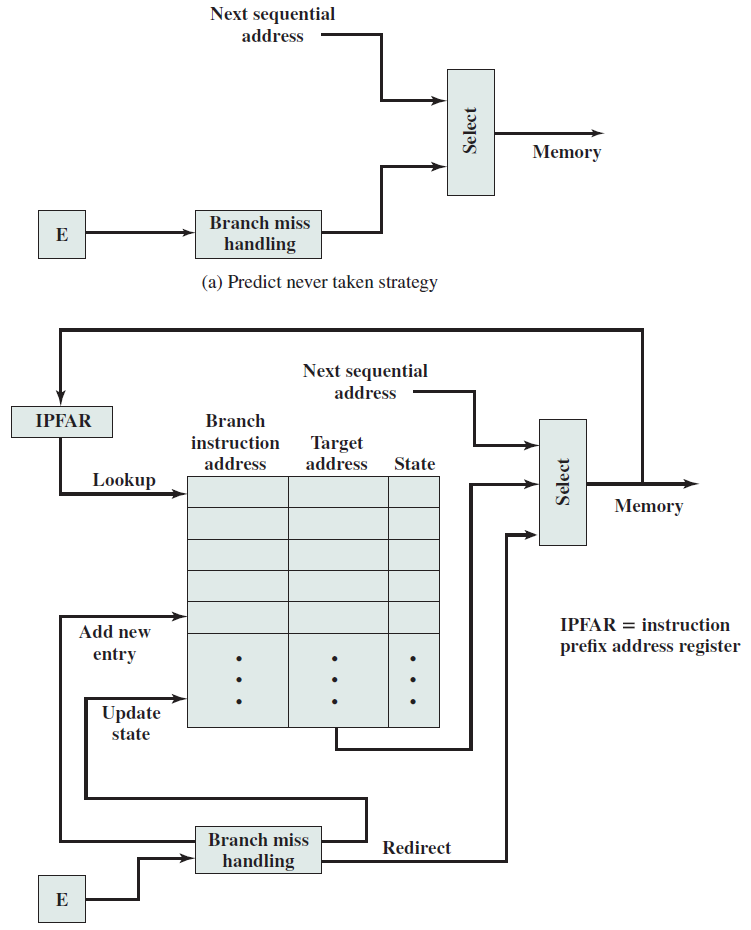

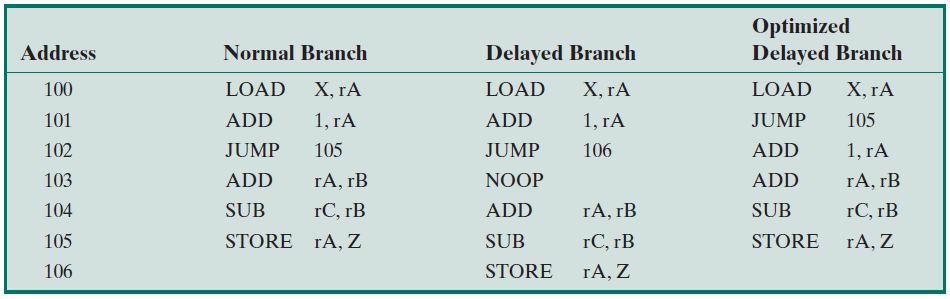

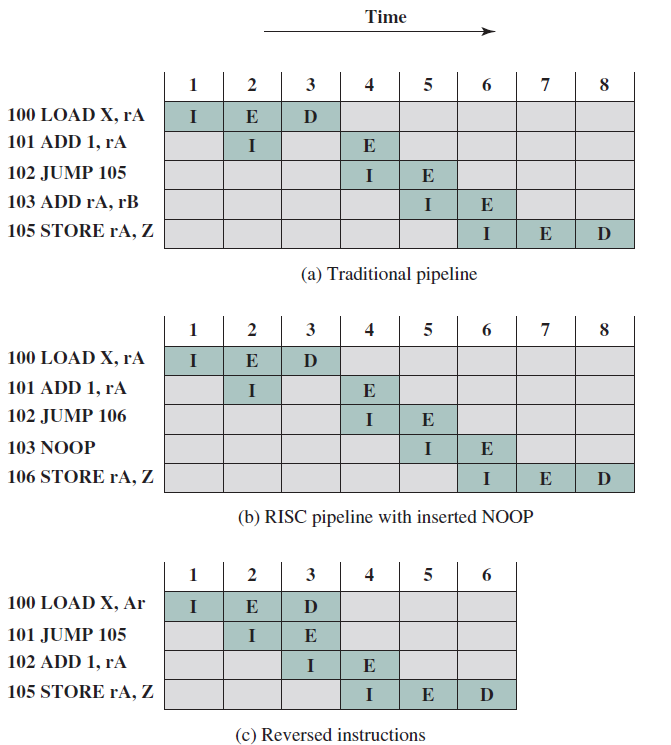

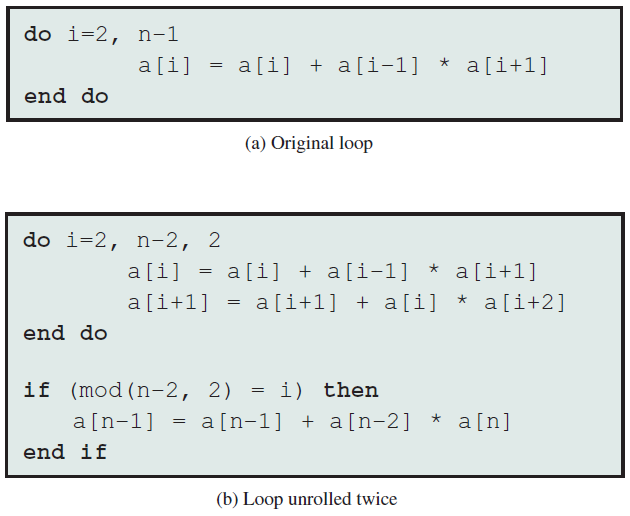

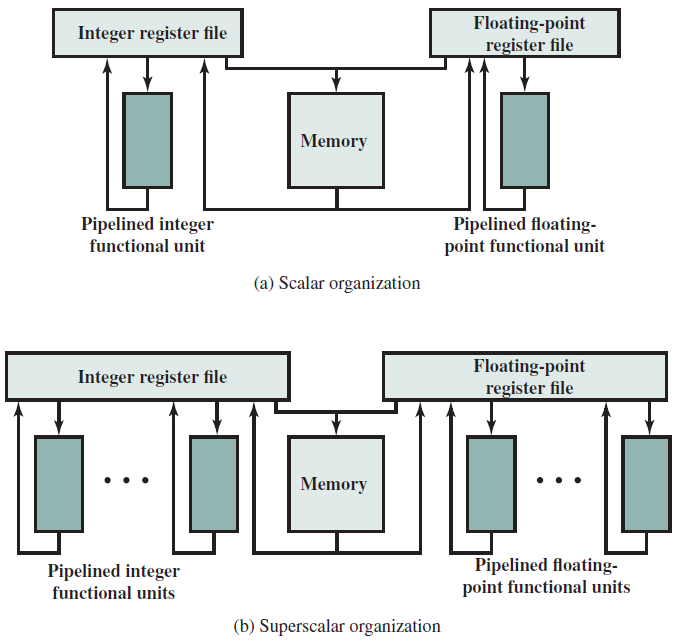

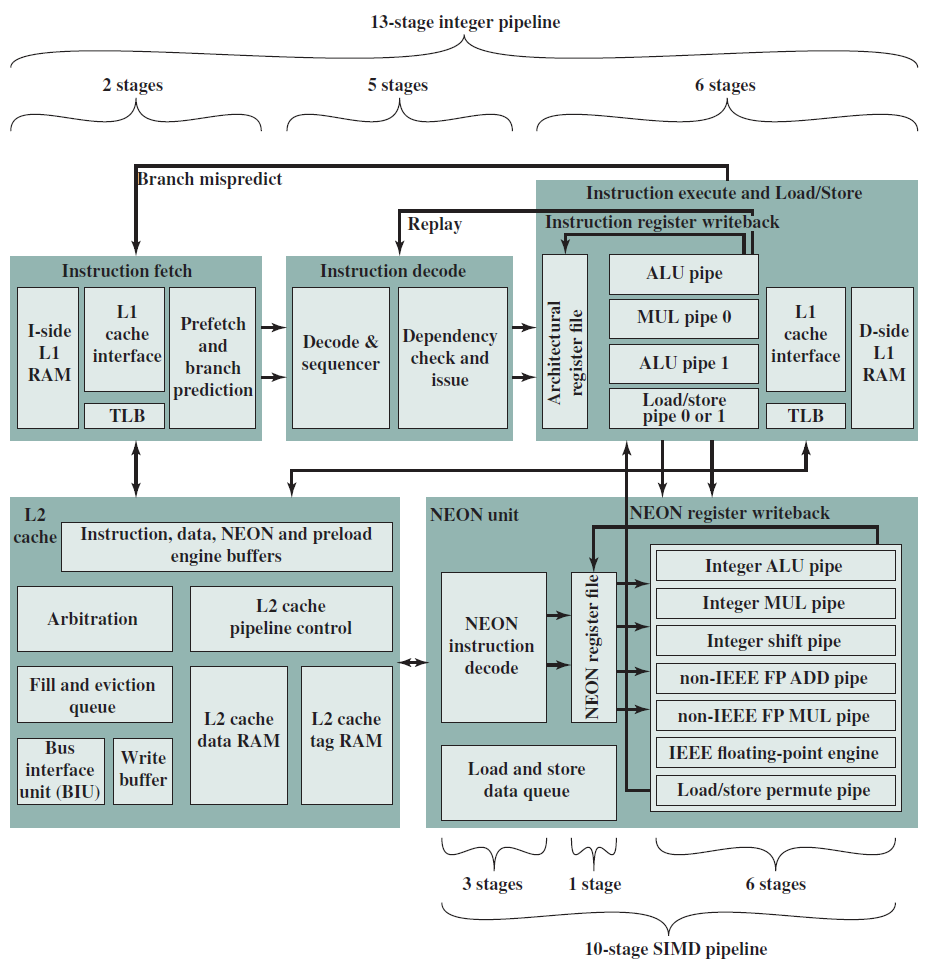

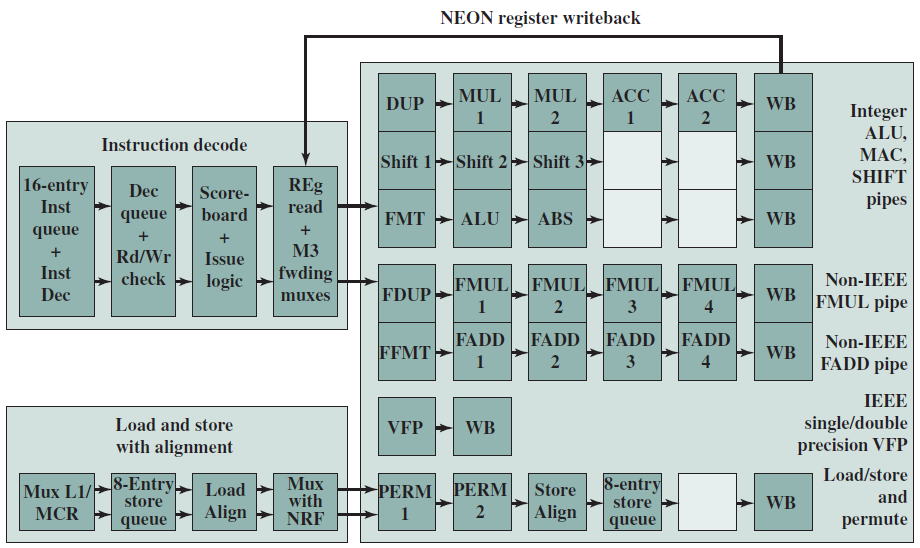

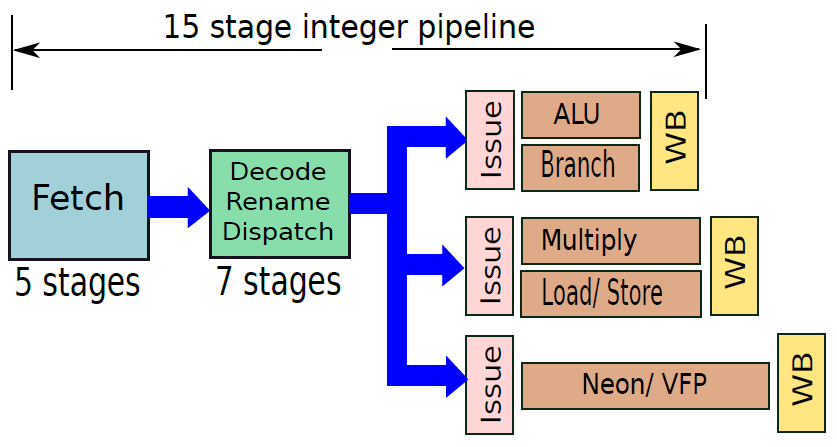

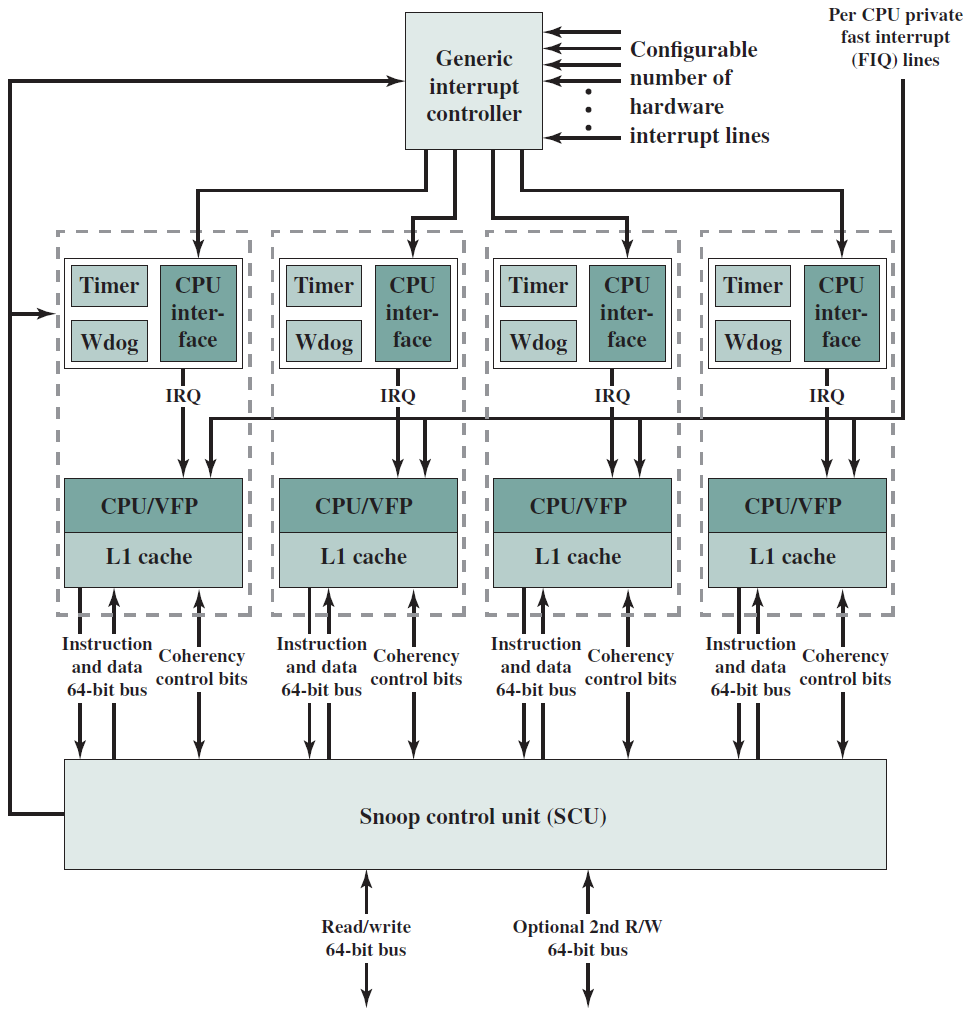

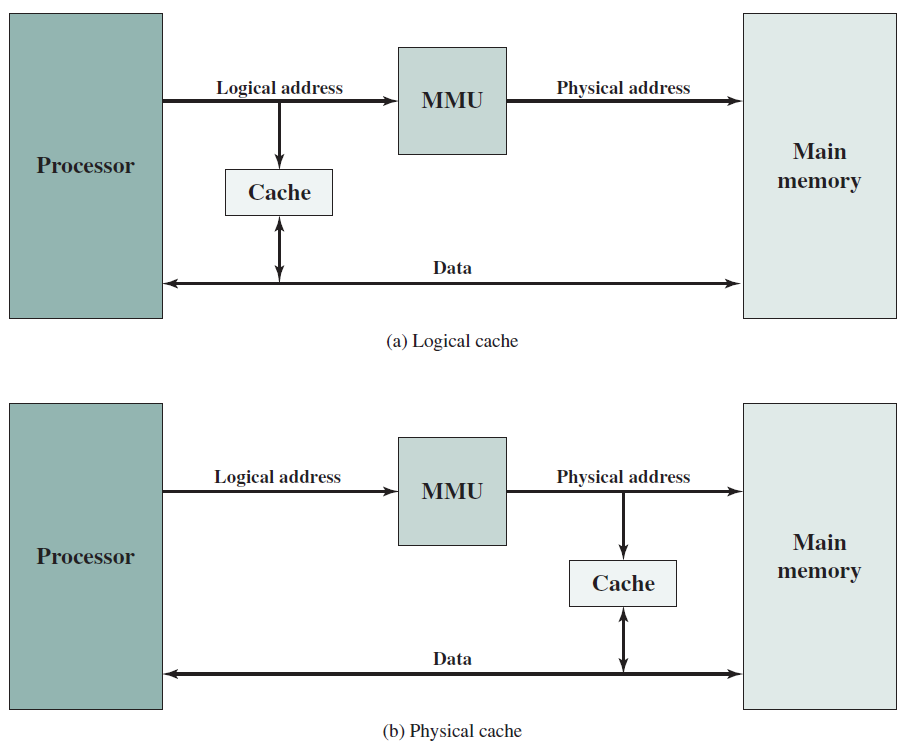

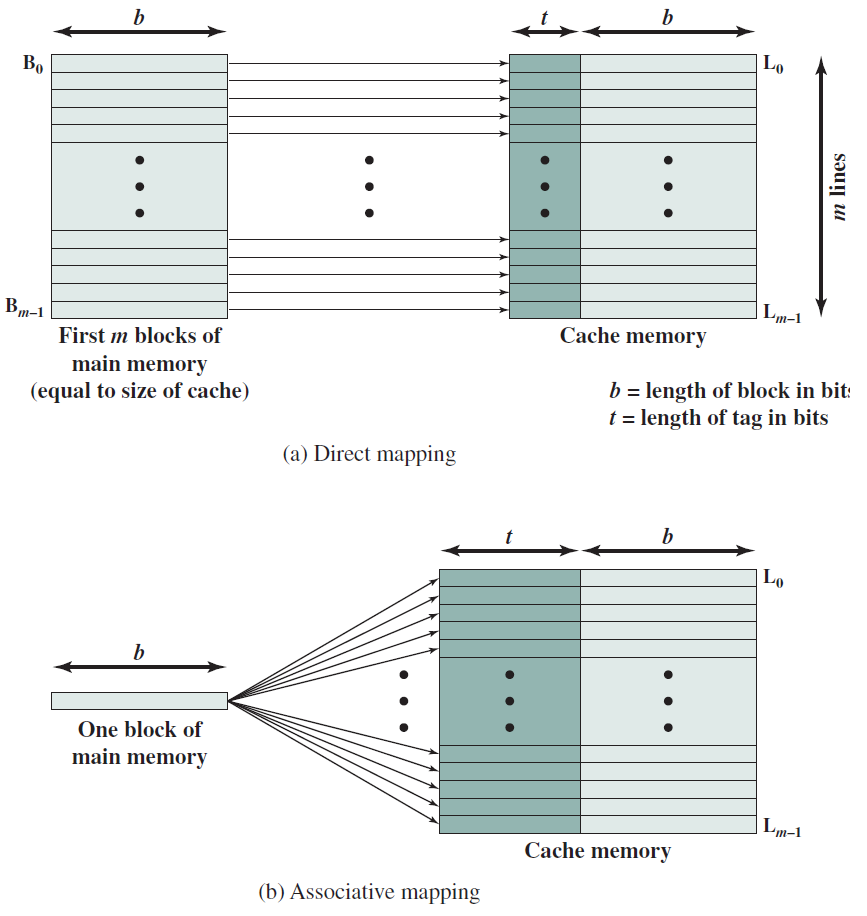

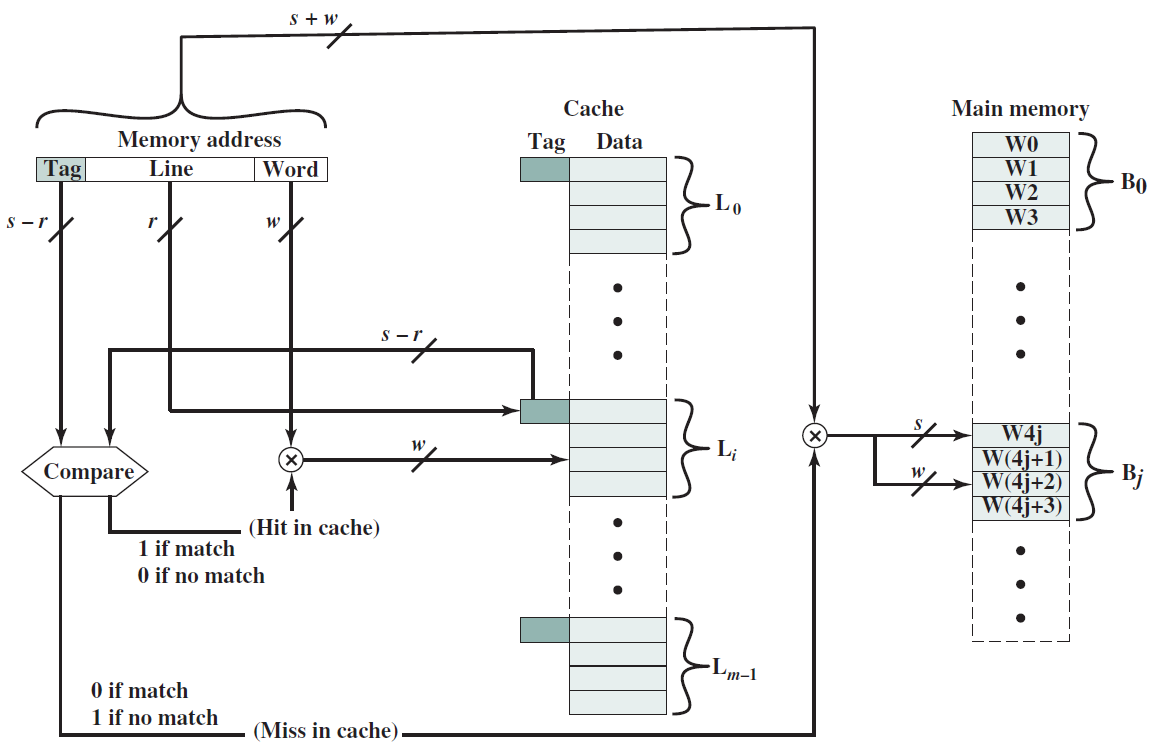

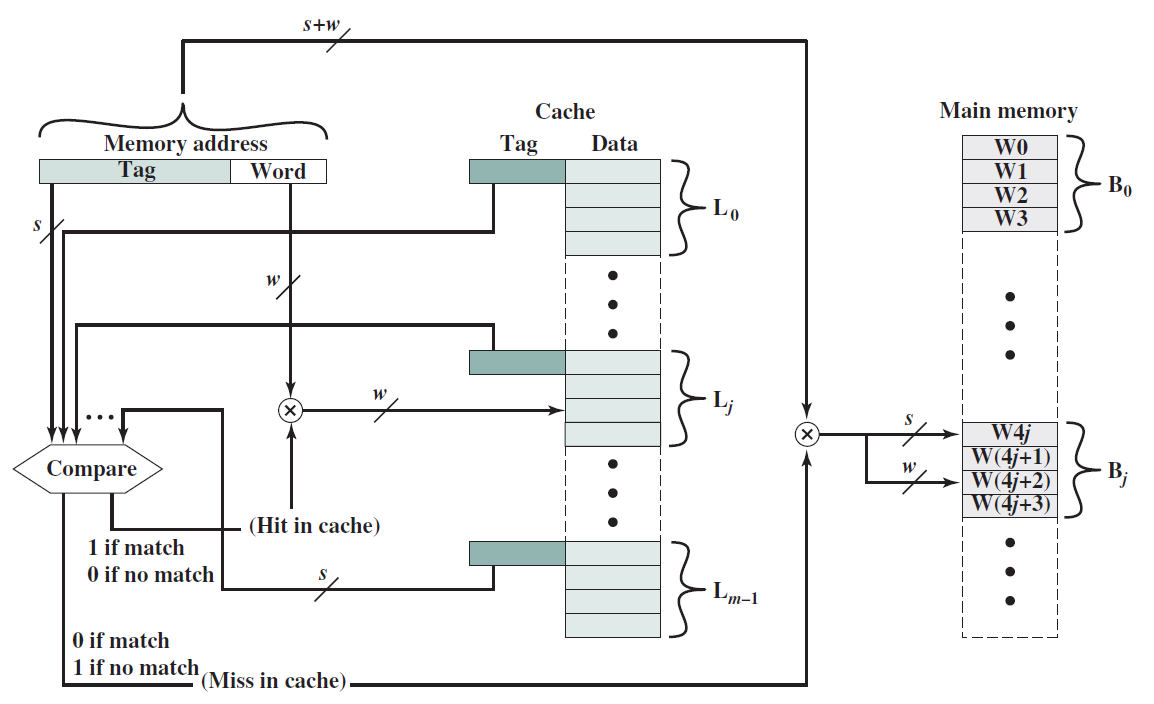

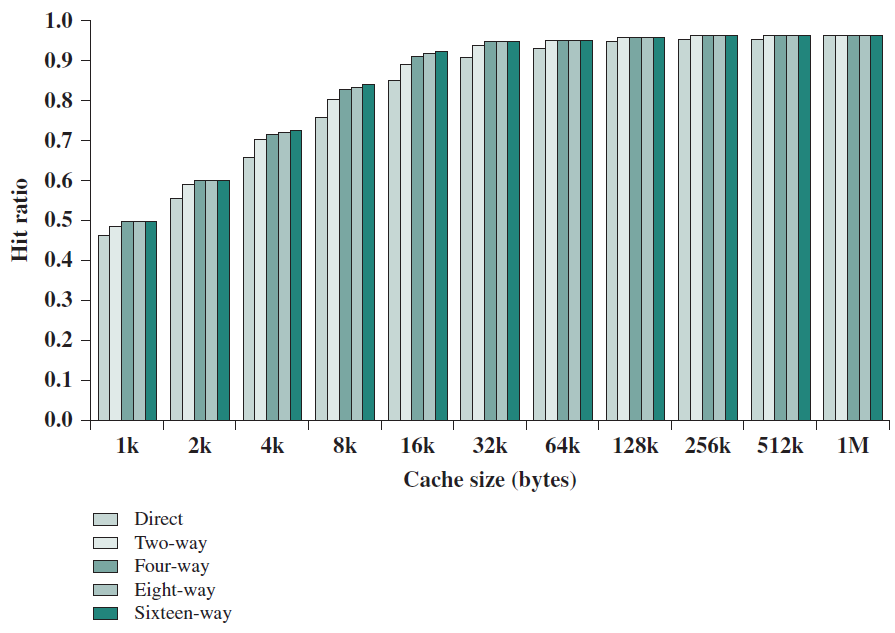

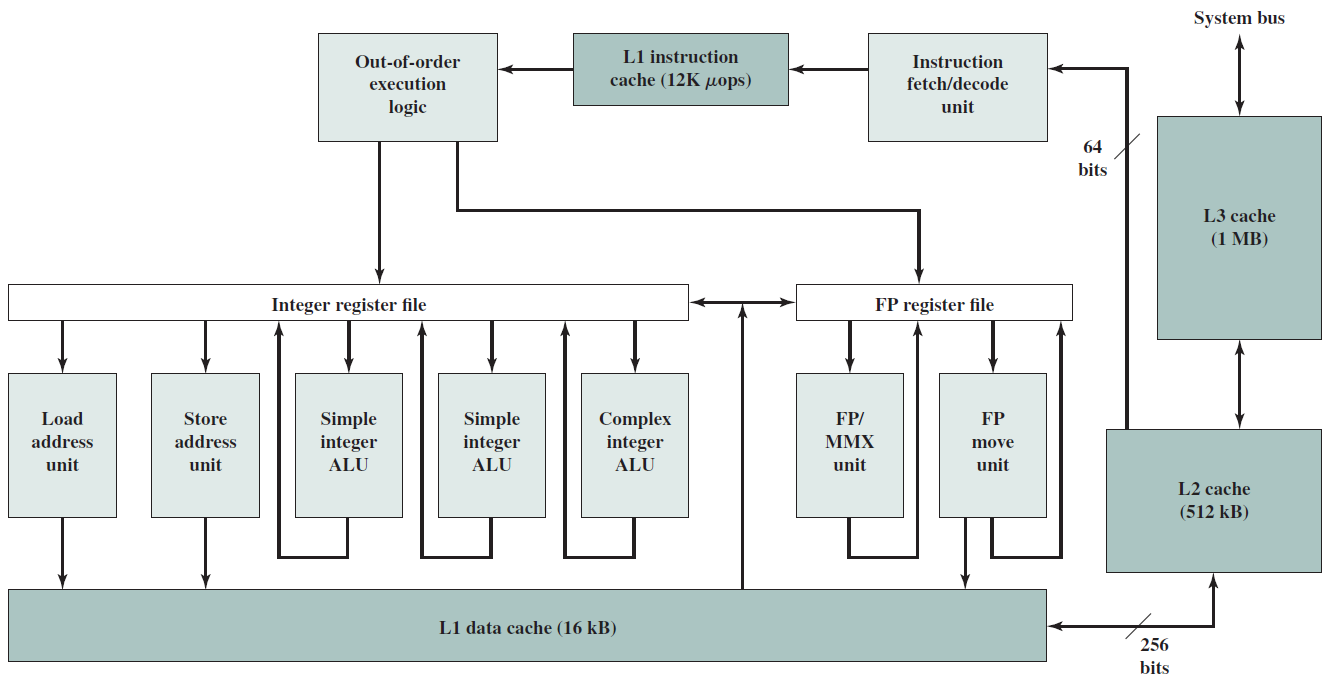

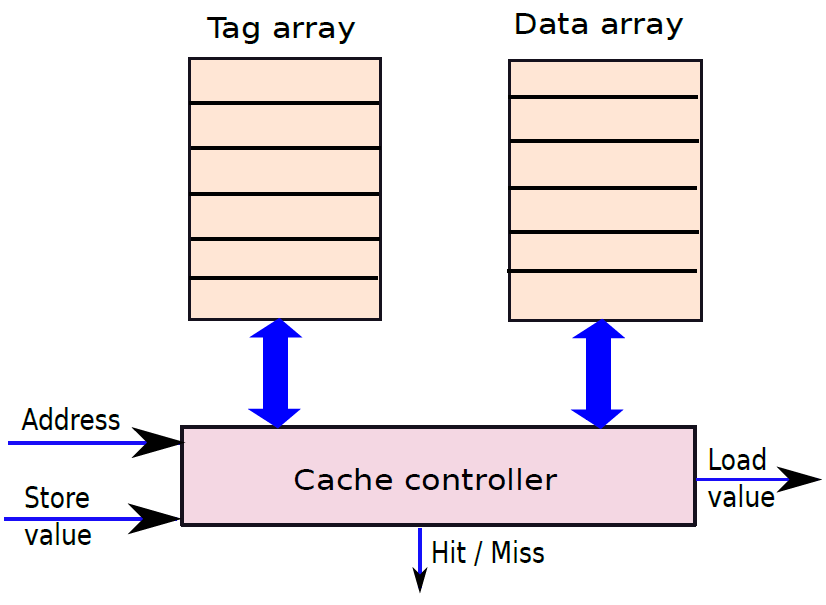

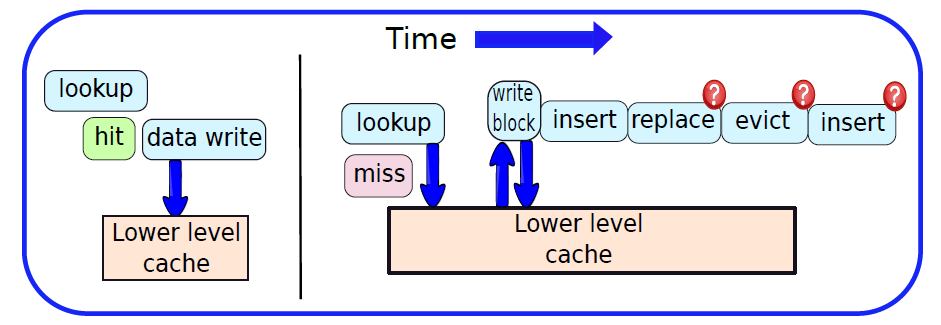

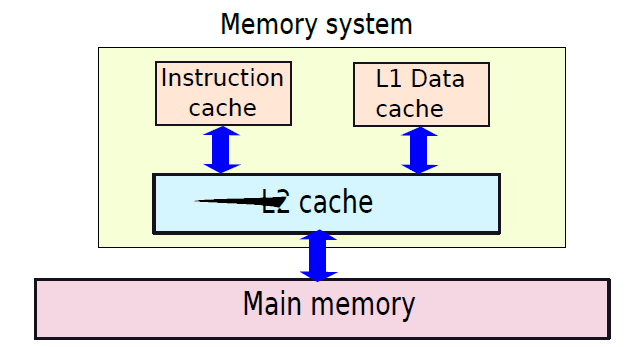

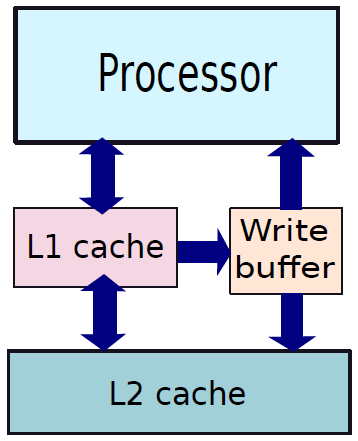

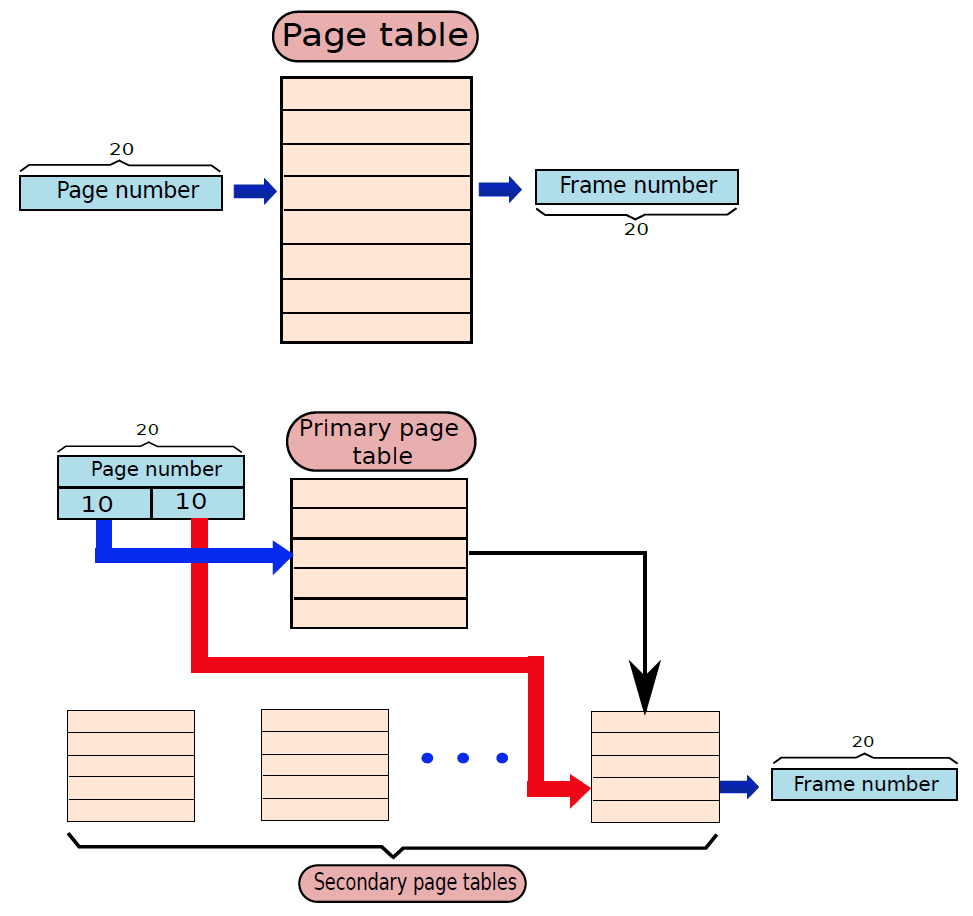

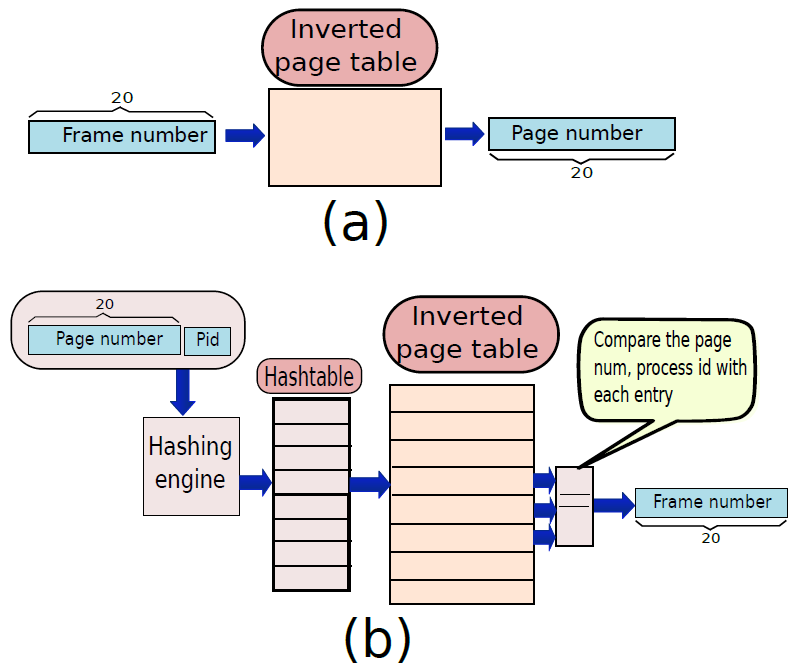

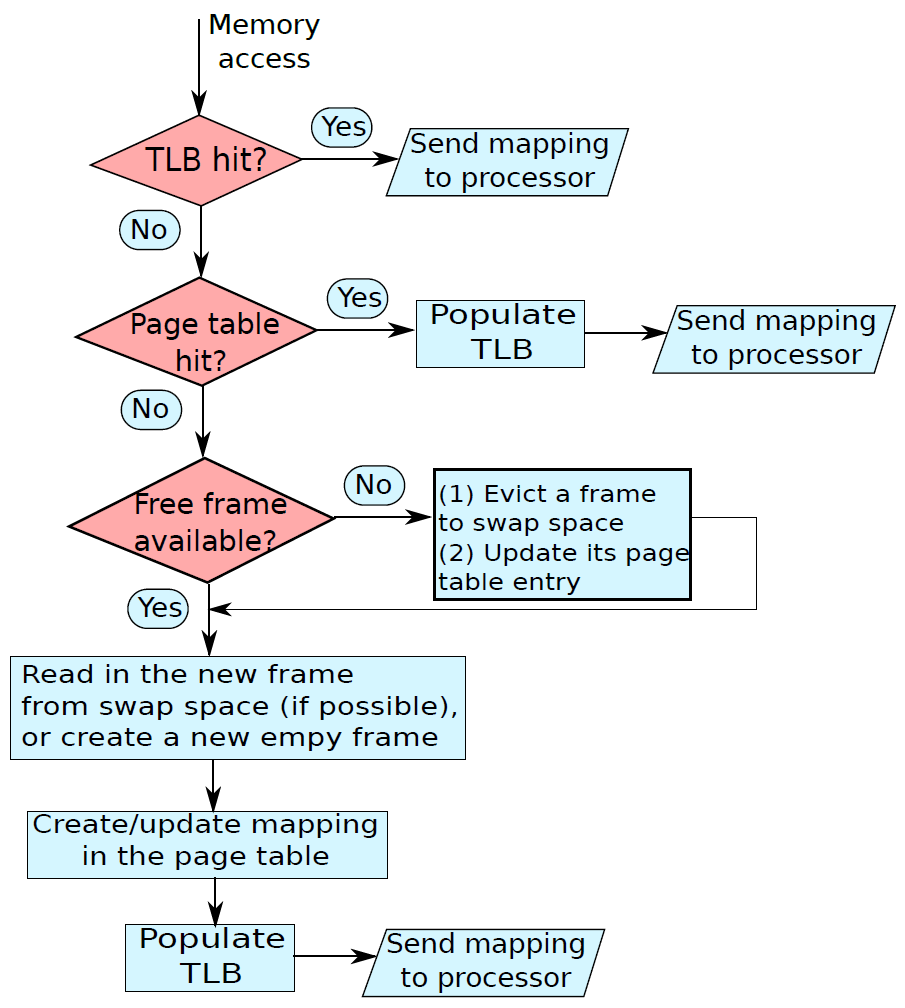

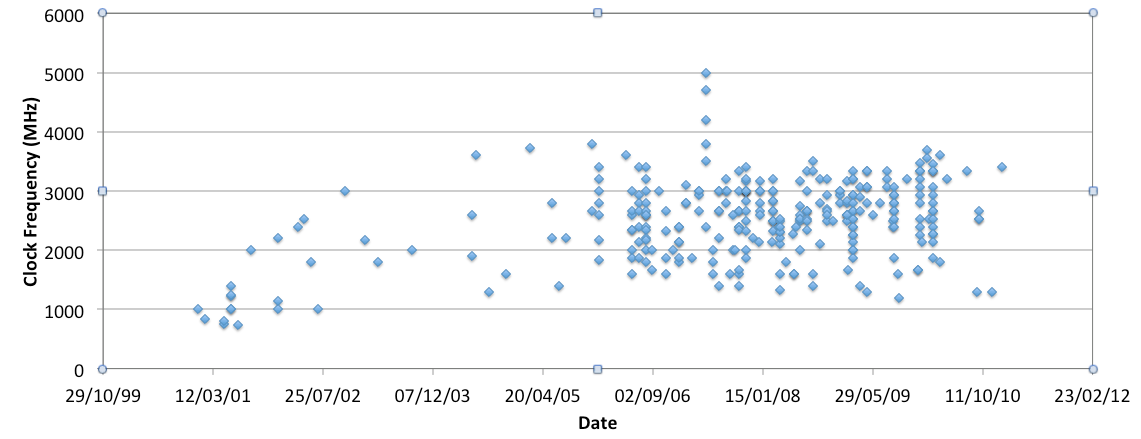

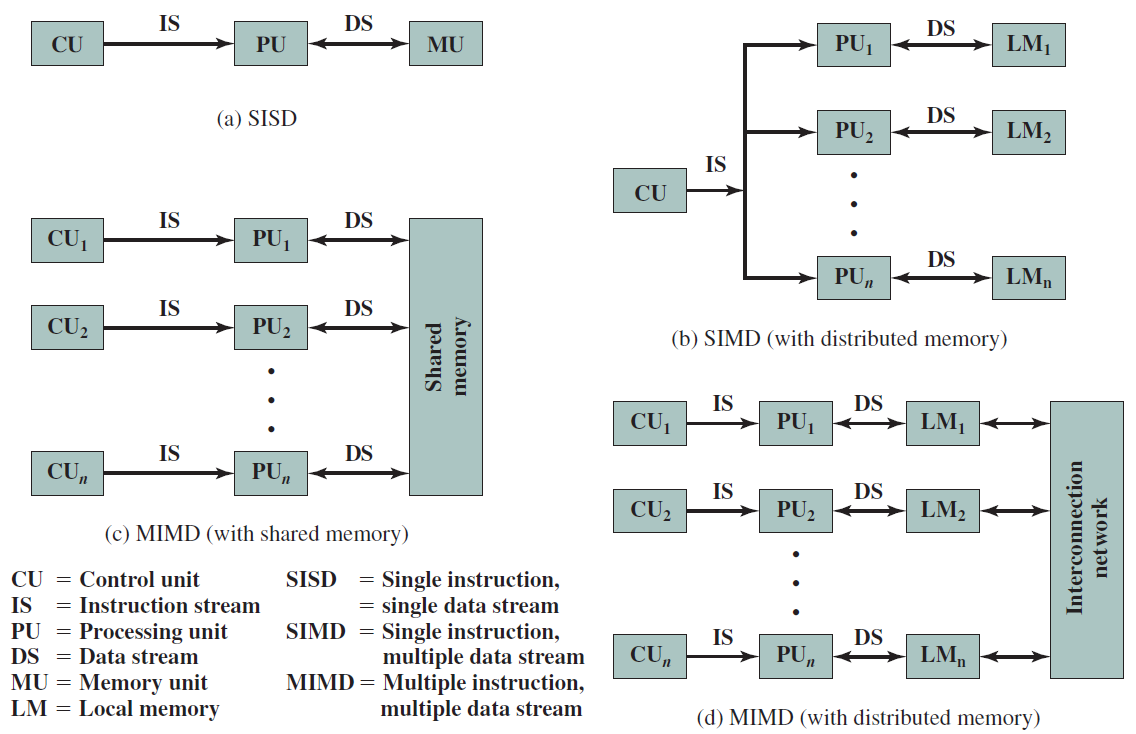

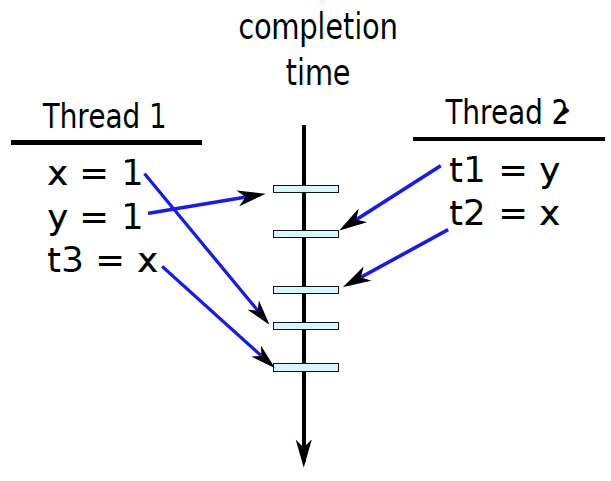

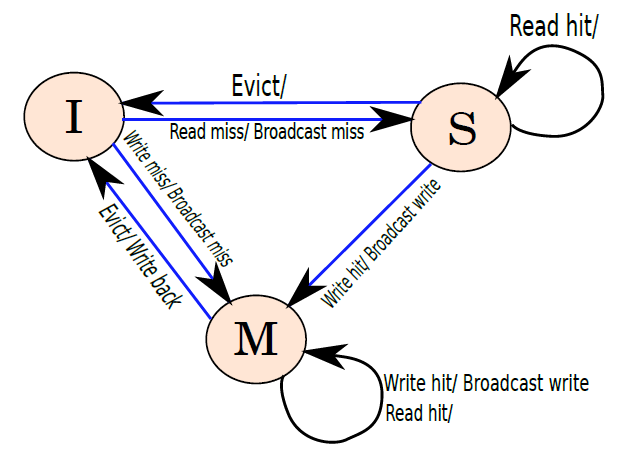

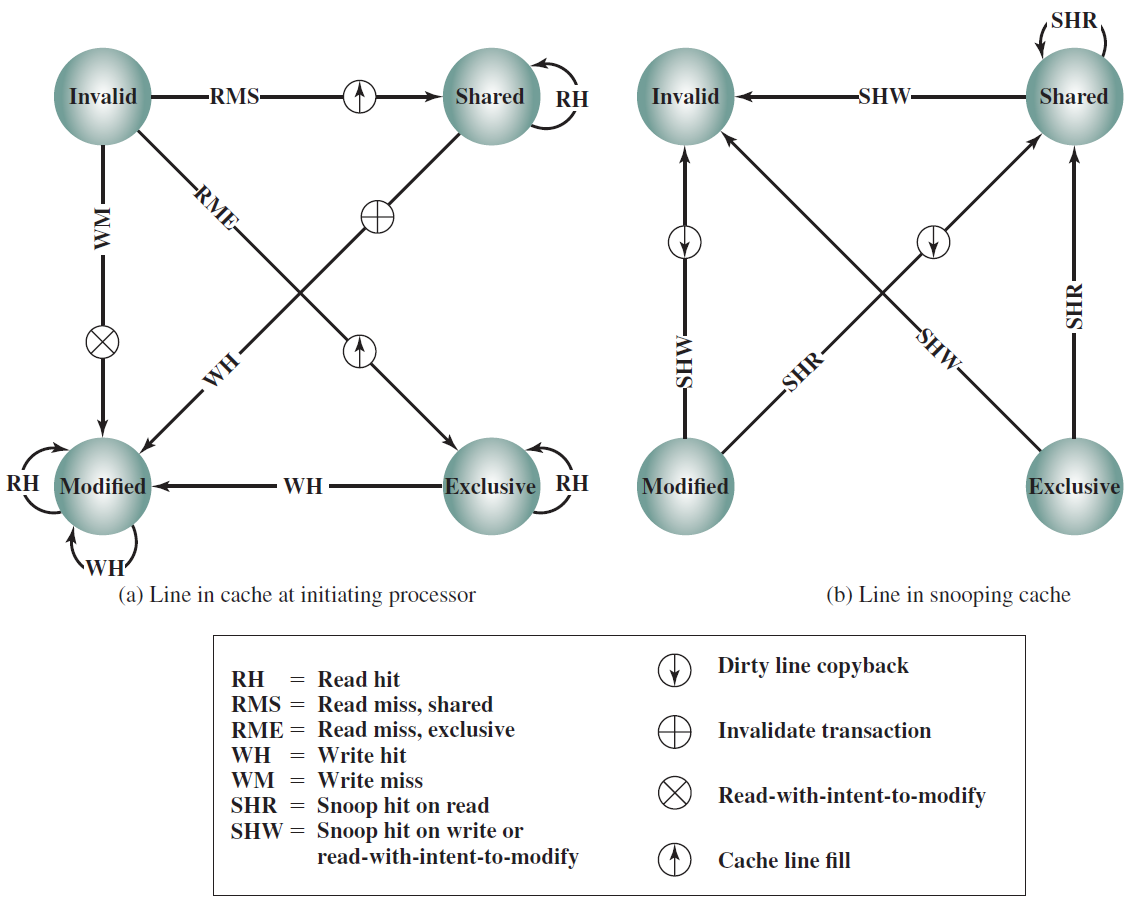

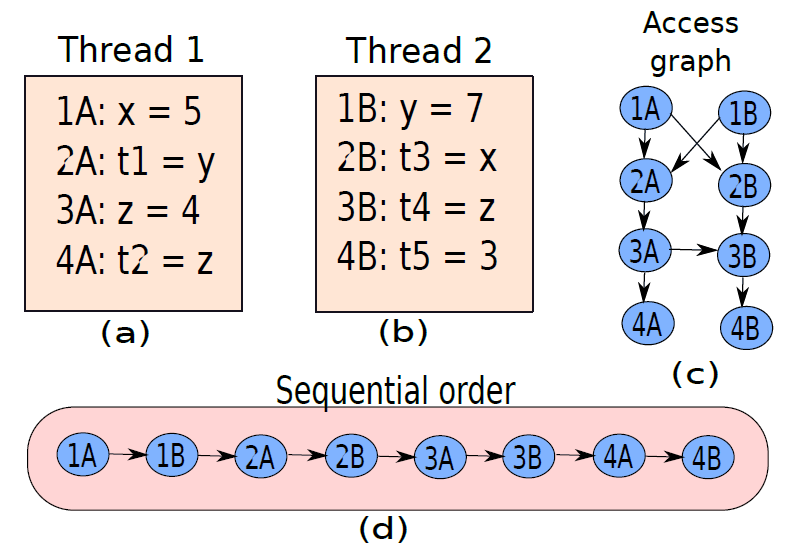

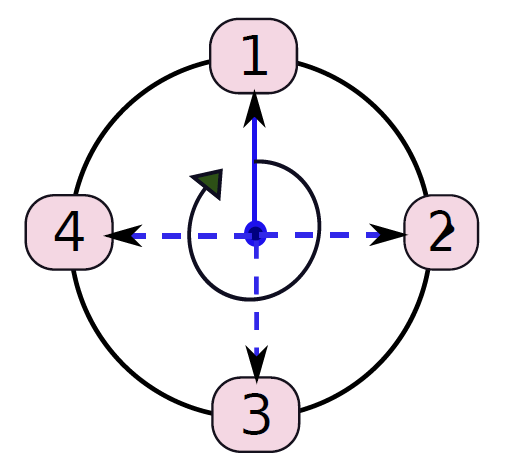

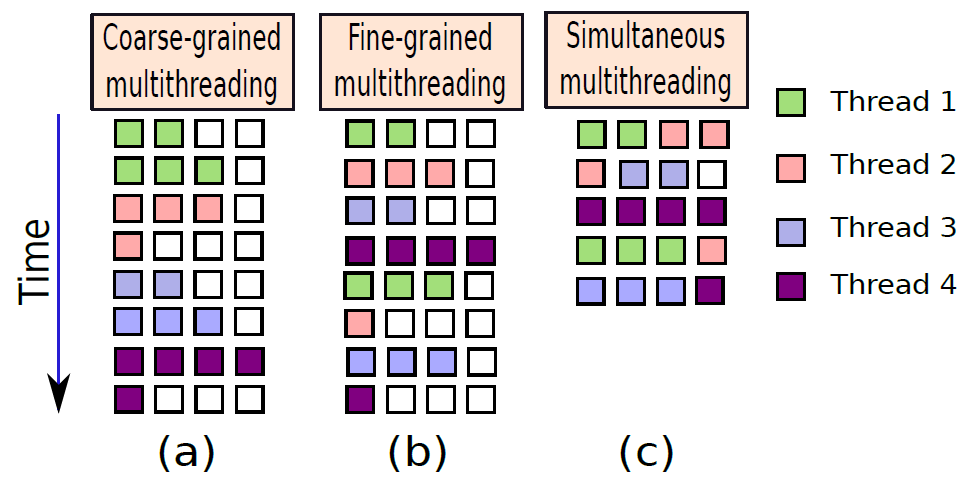

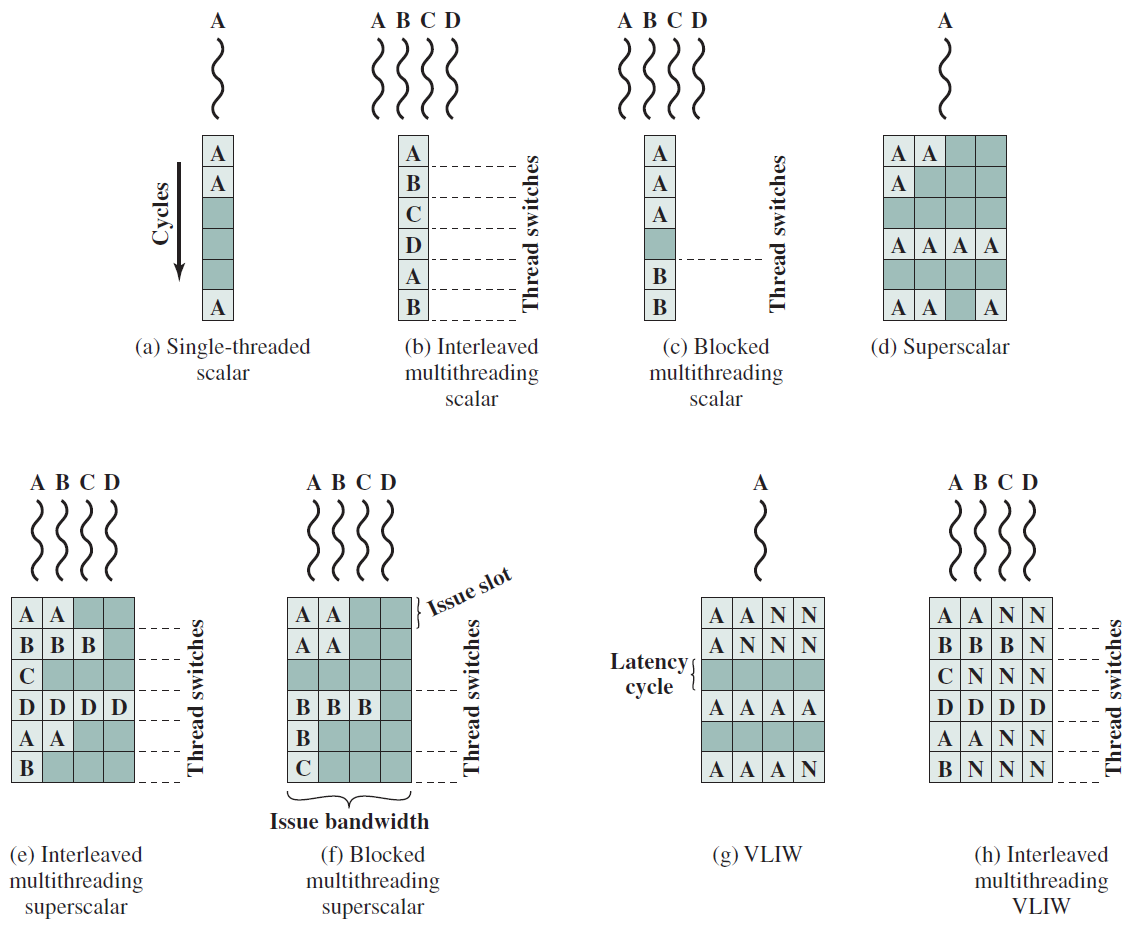

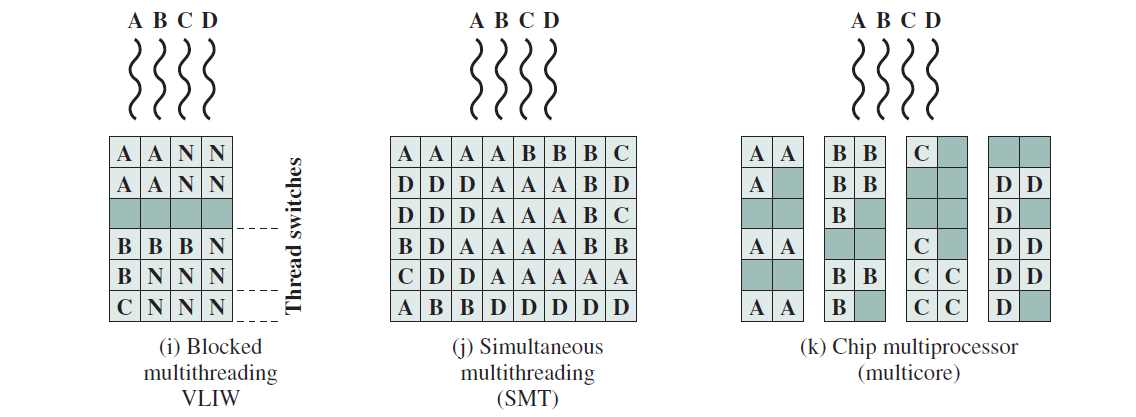

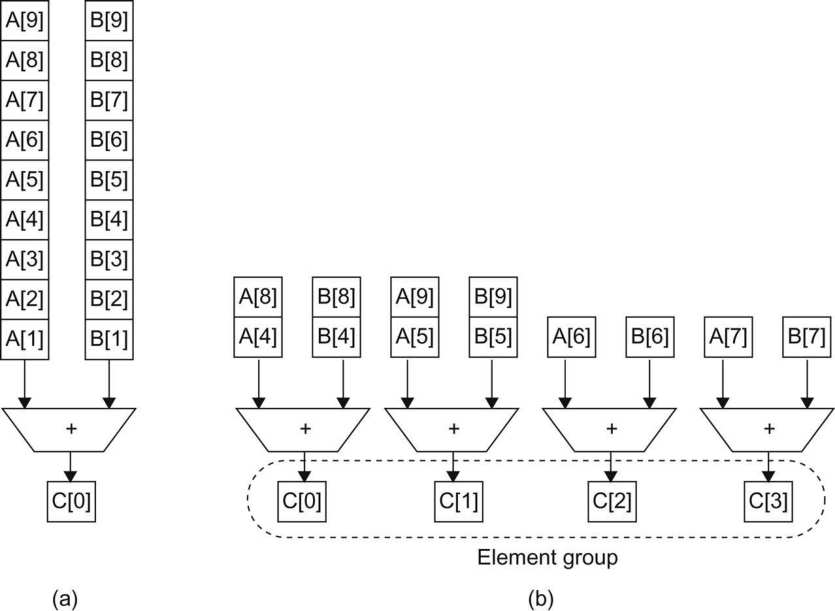

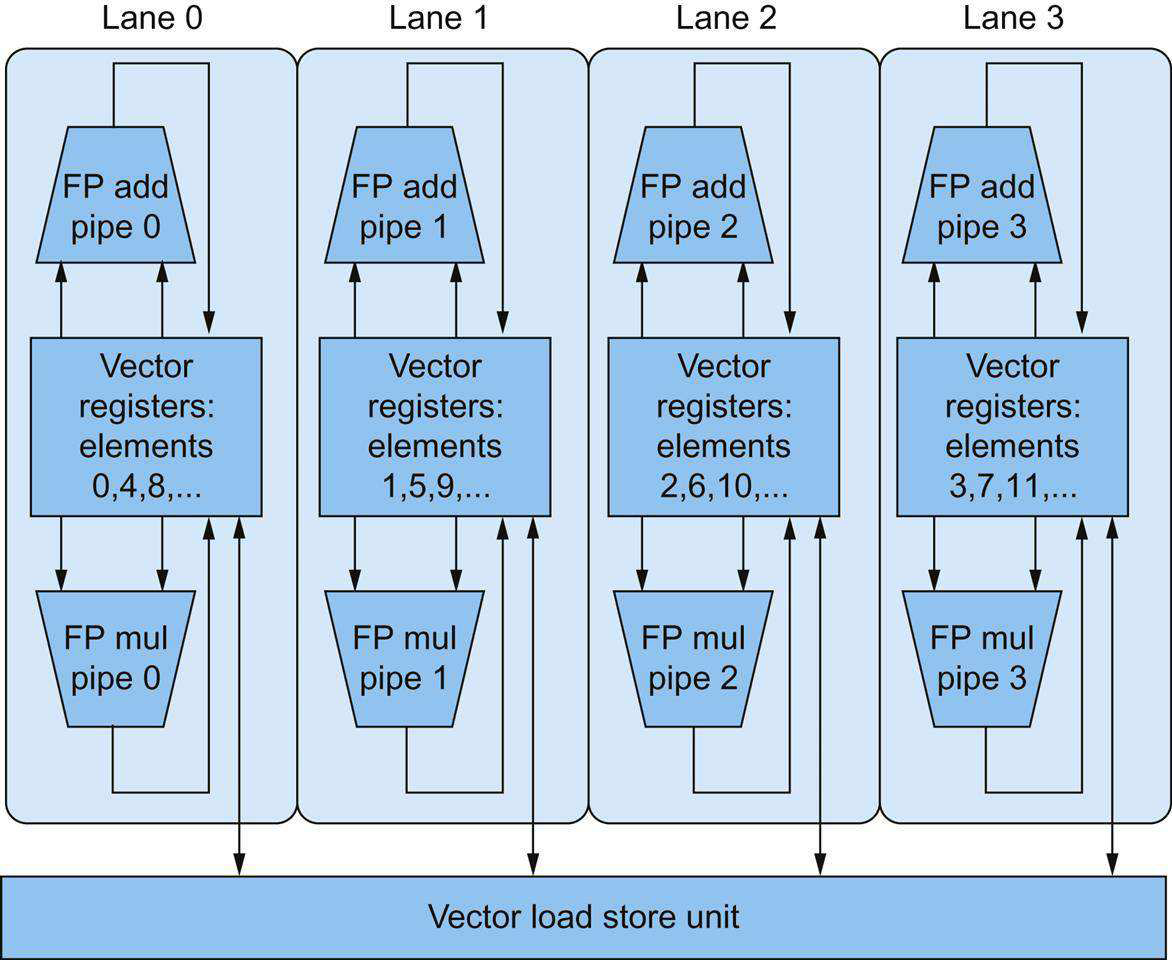

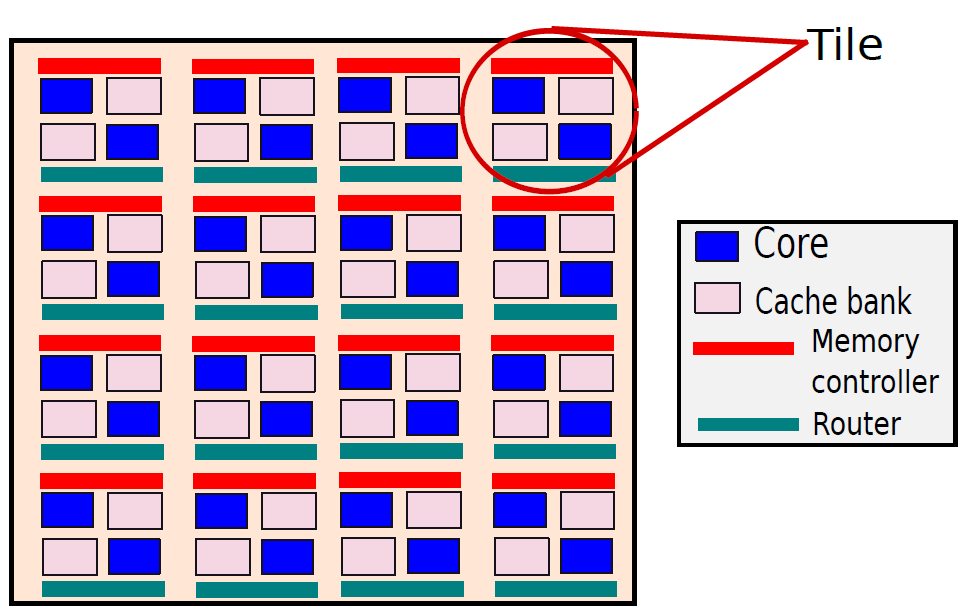

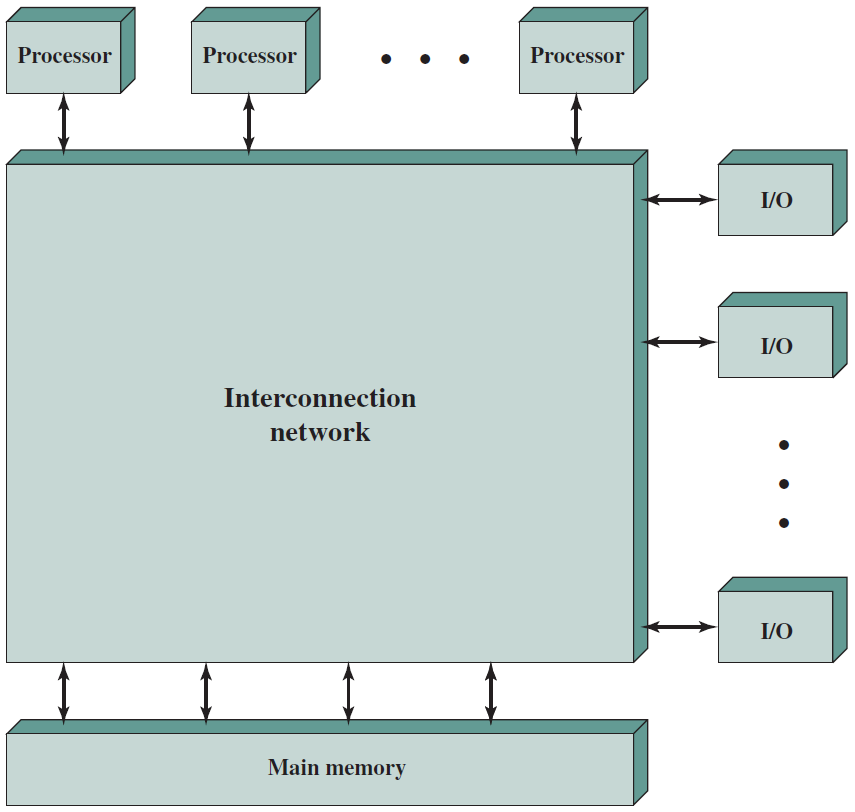

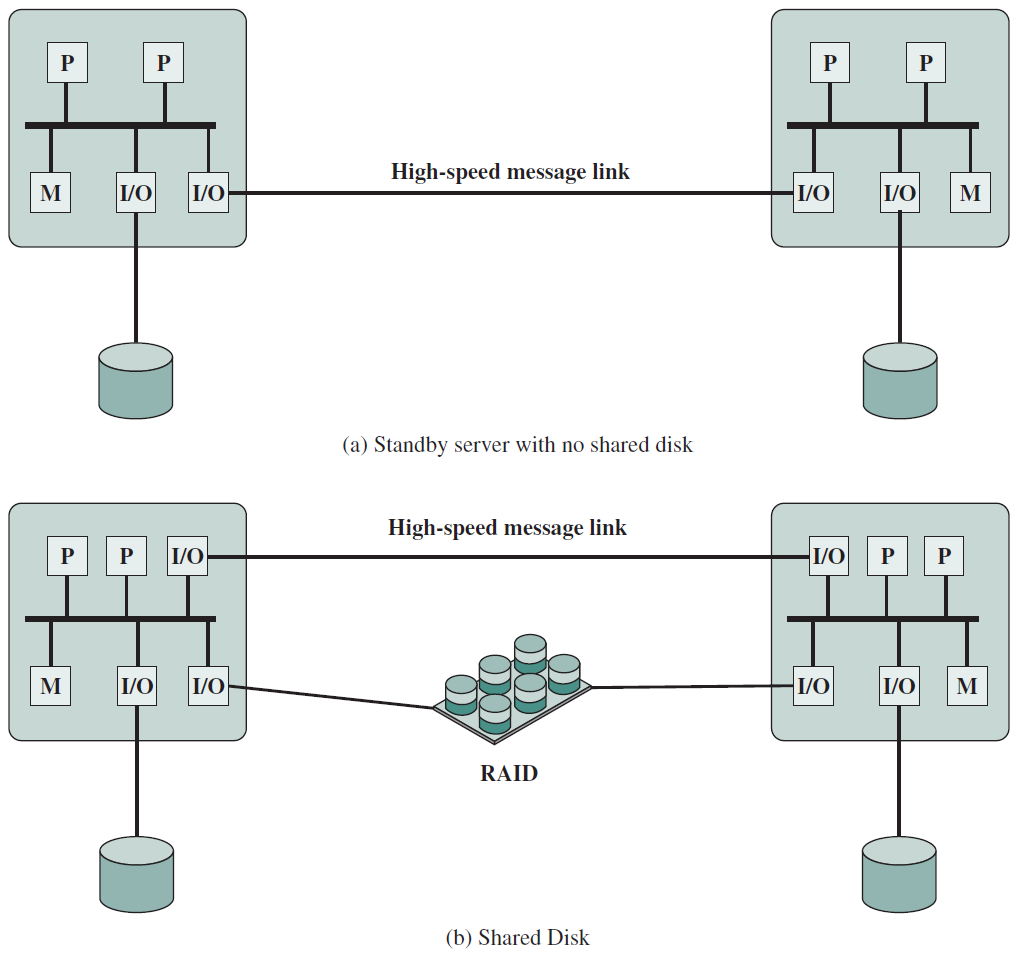

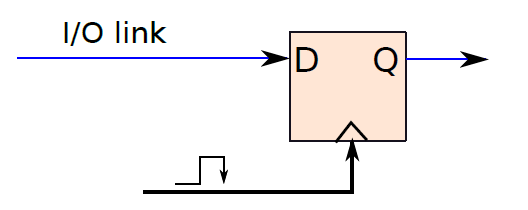

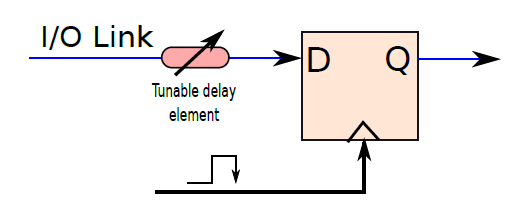

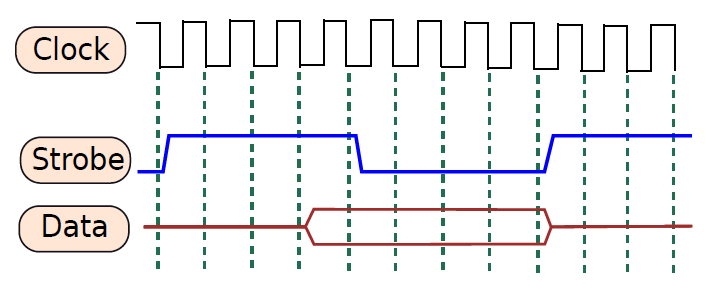

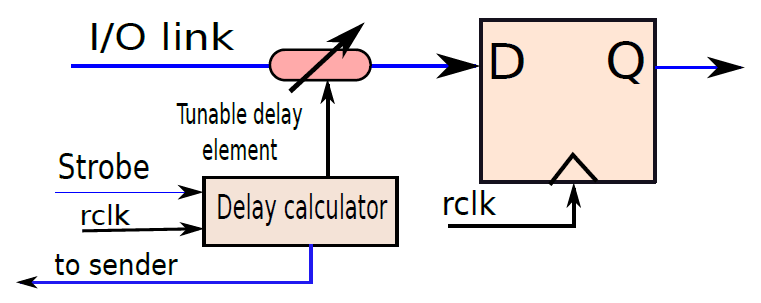

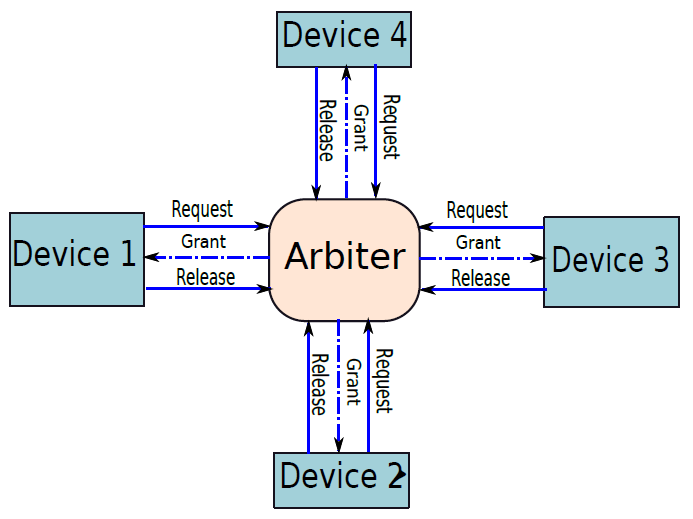

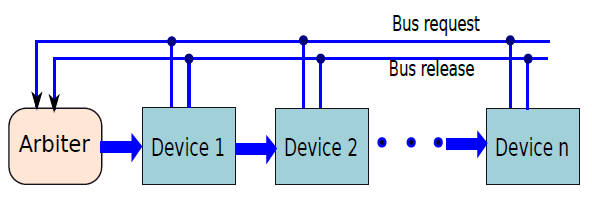

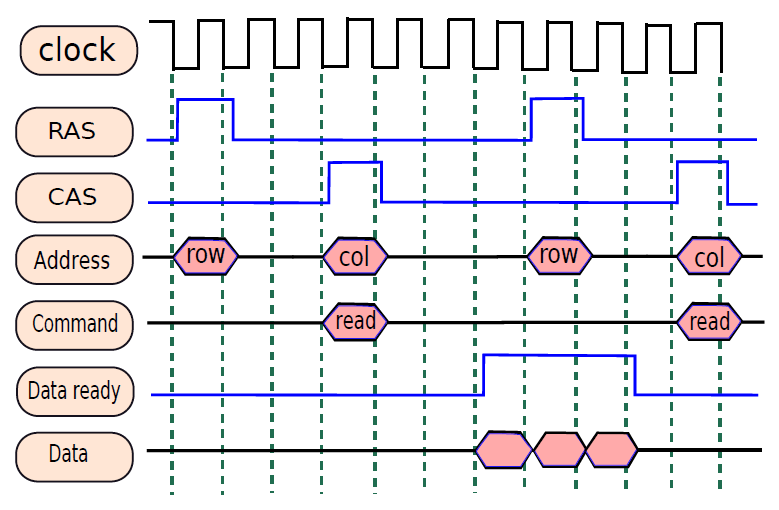

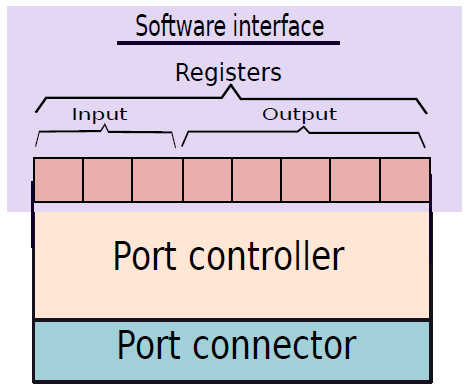

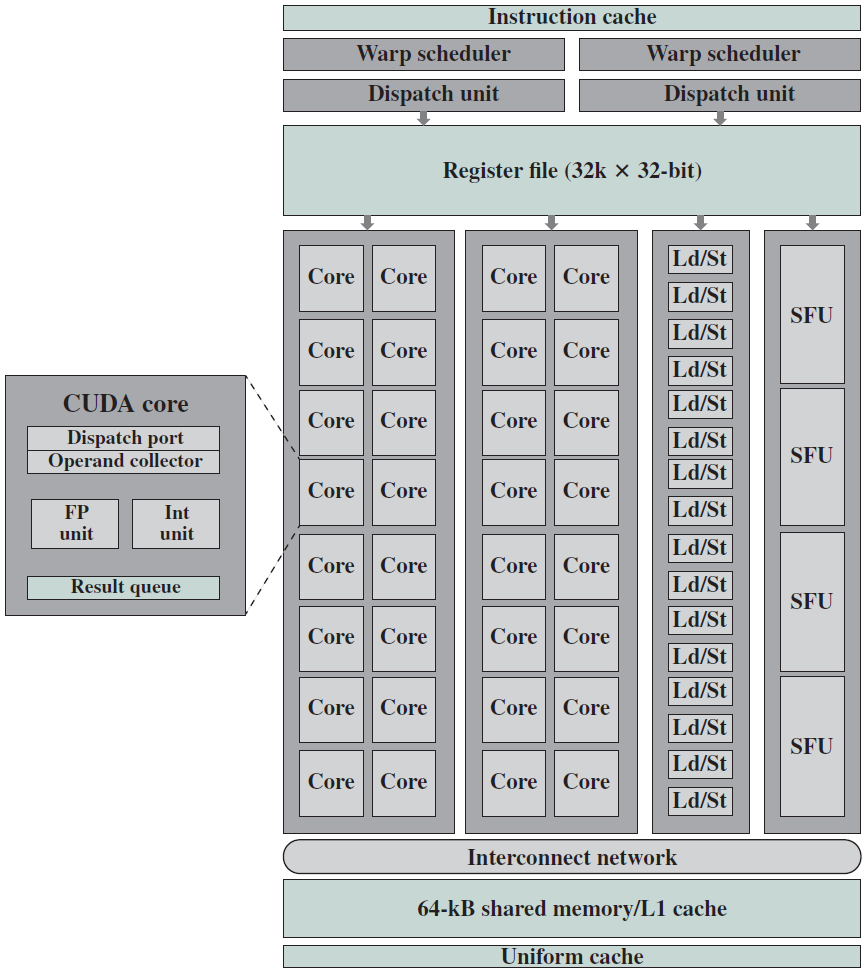

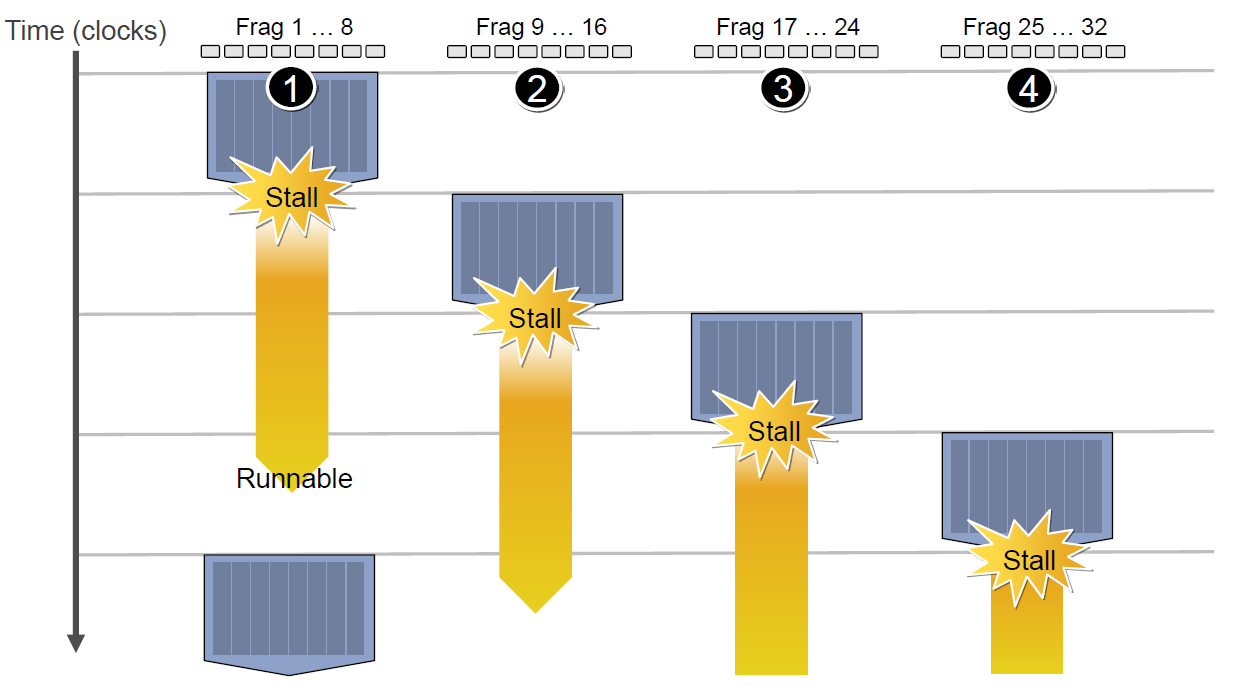

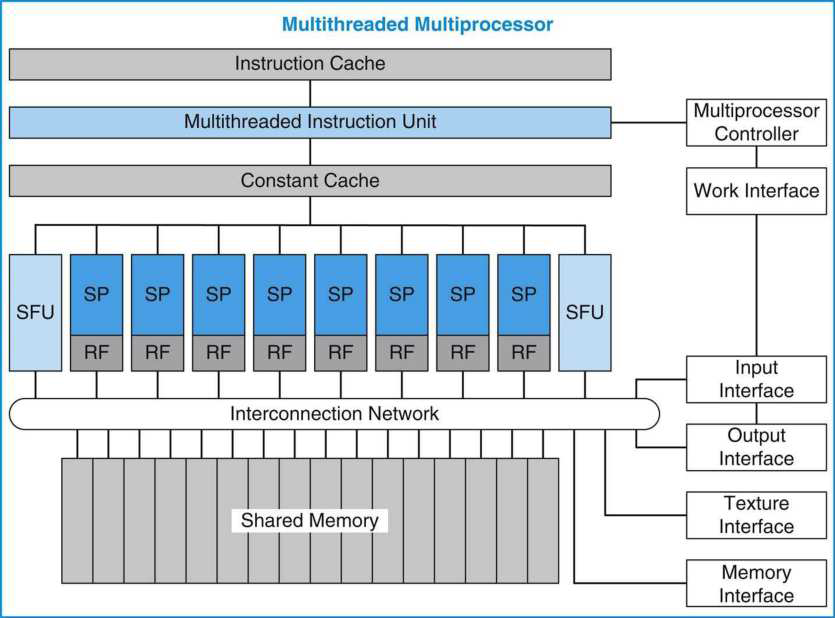

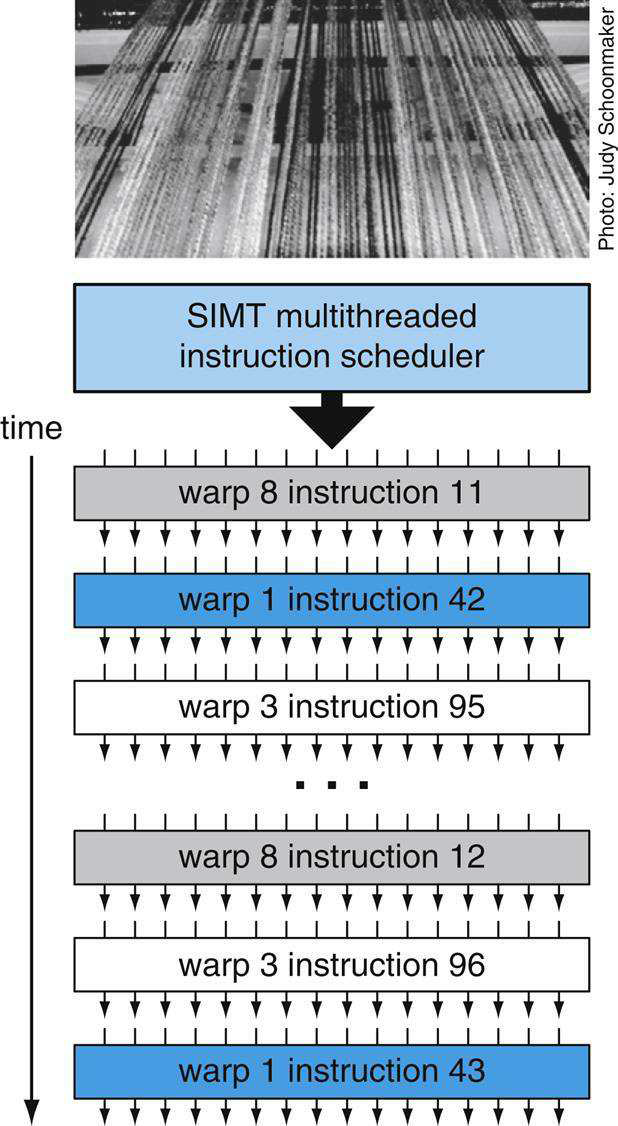

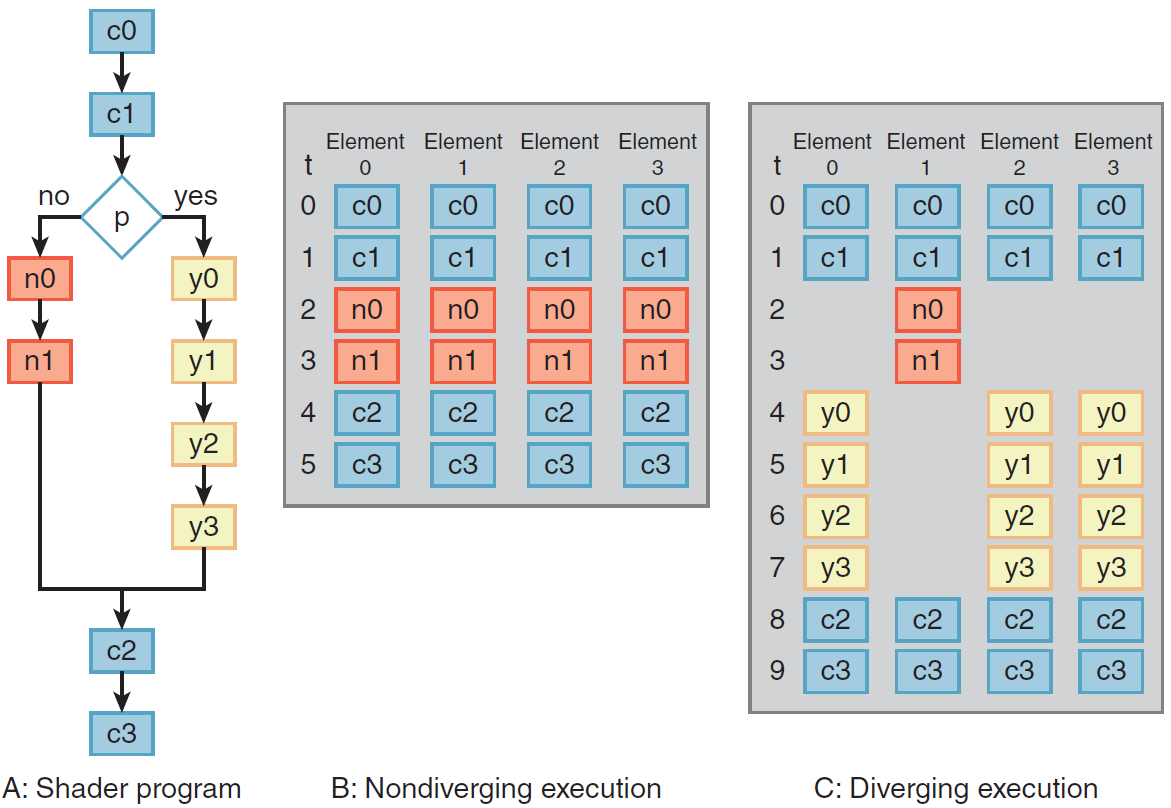

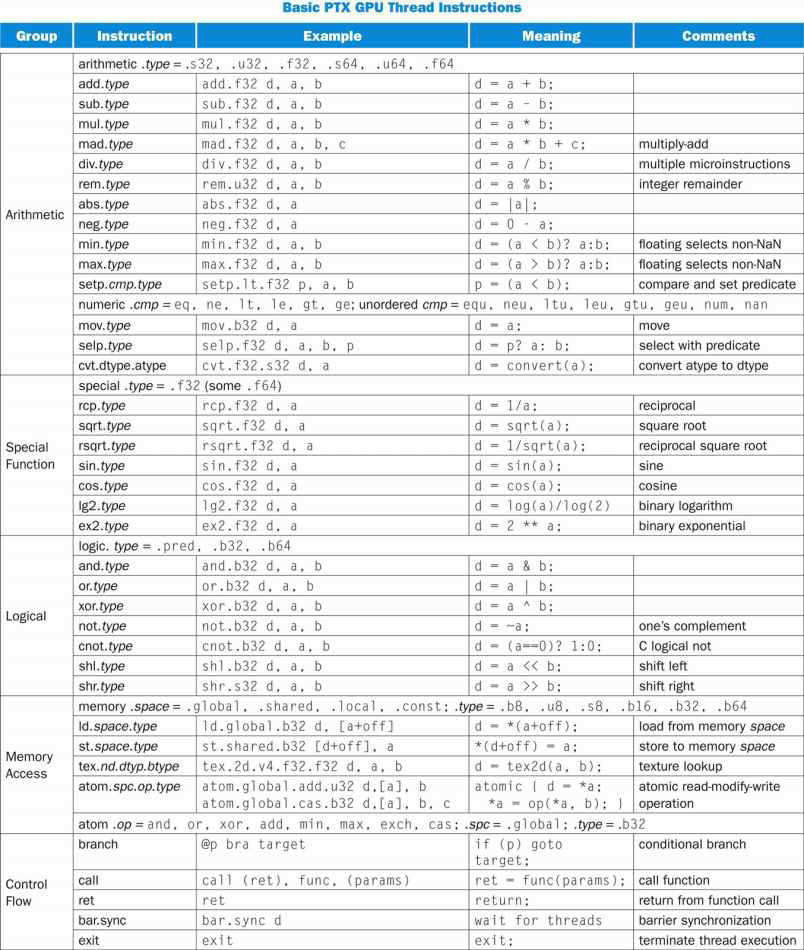

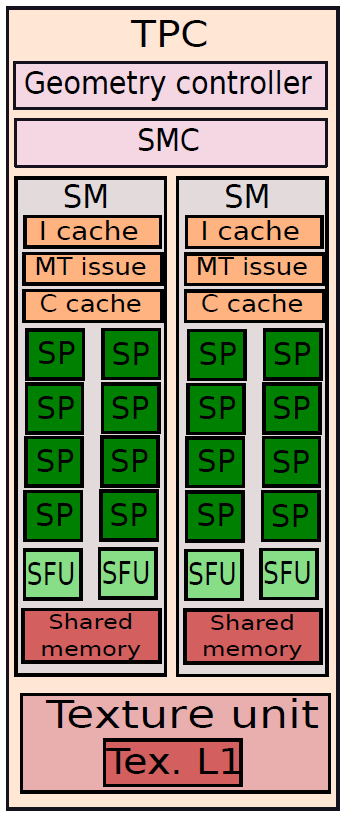

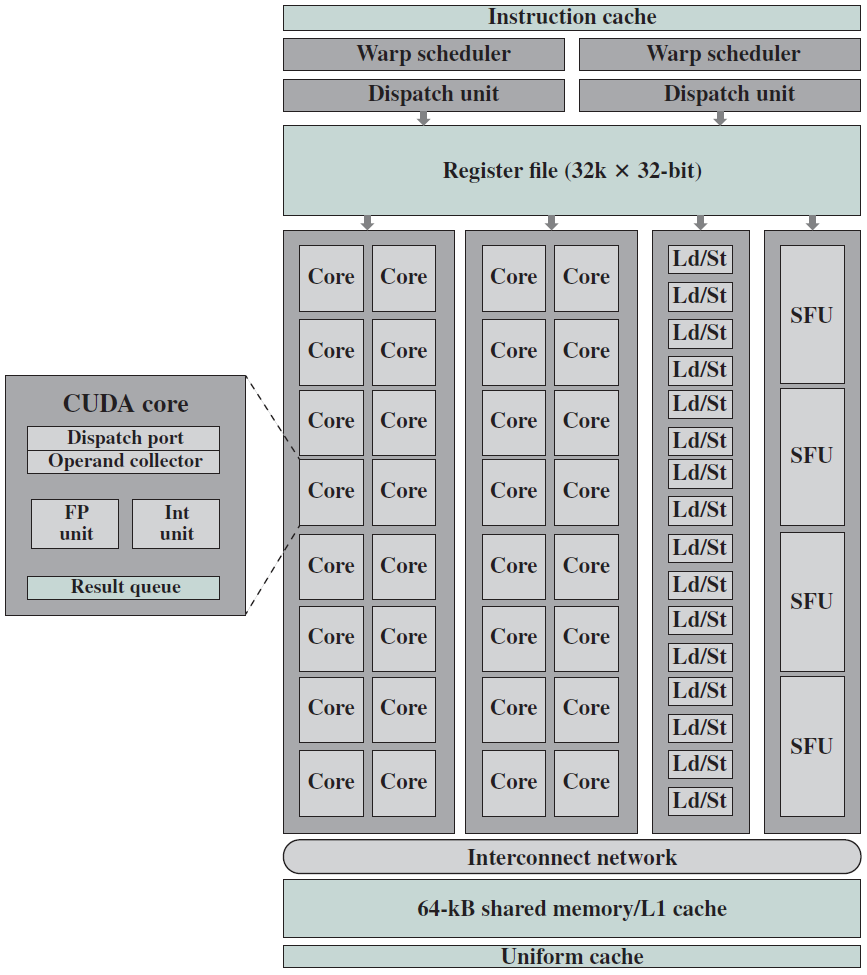

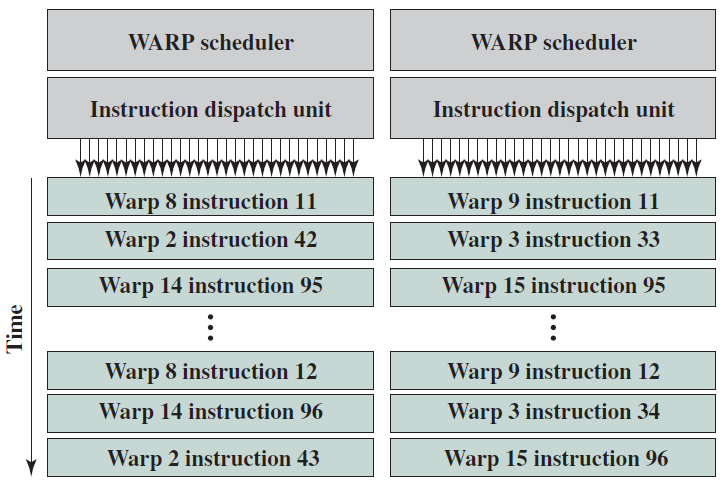

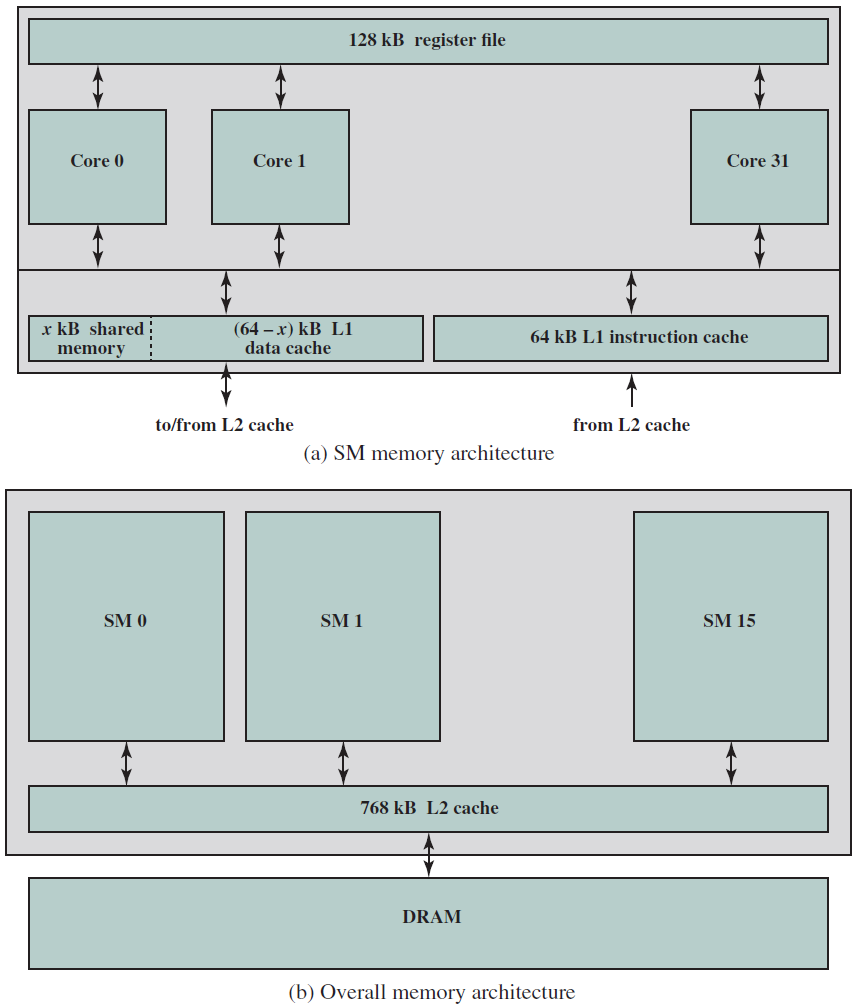

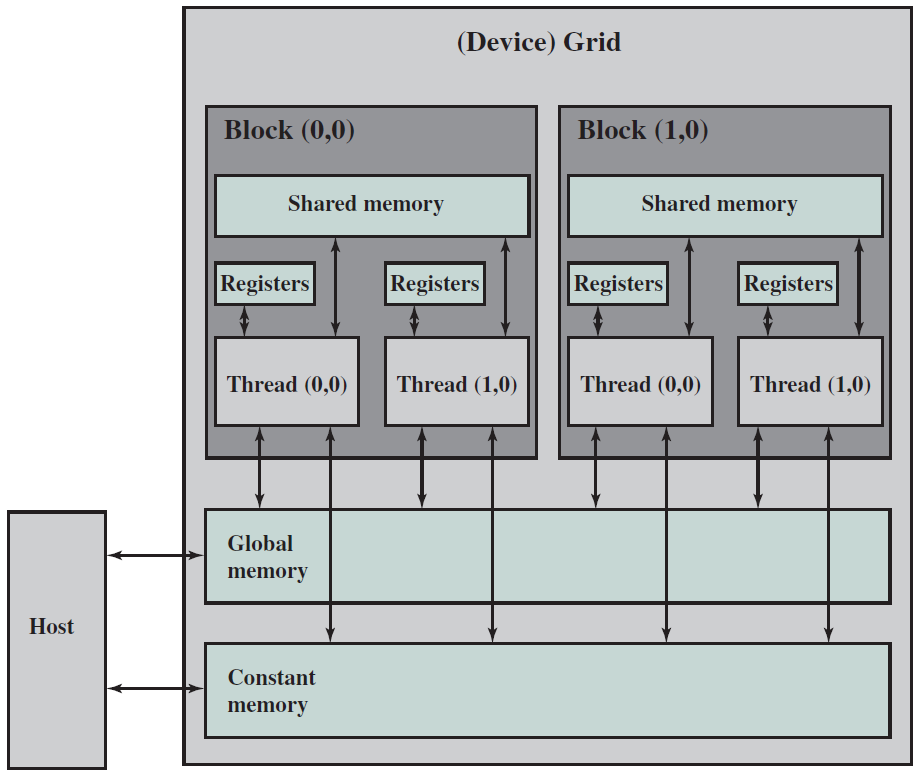

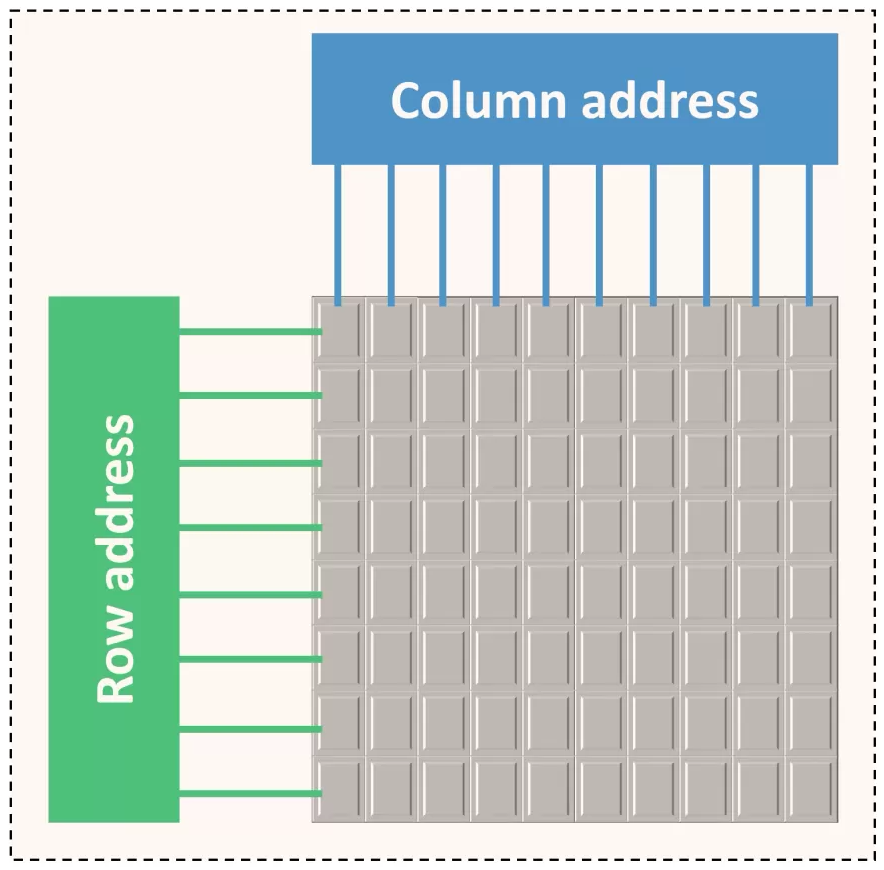

例如,從指令記憶體中獲取指令需要一些時間。然後需要時間從暫存器檔案讀取值,並用ALU計算結果。記憶體存取和將結果寫回暫存器檔案也是相當耗時的操作。需要等待所有這些單獨的子操作完成,然後才能開始處理下一條指令,意味著電路中有大量的空閒,當運算元獲取單元執行其工作時,所有其他單元都處於空閒狀態。同樣,當ALU處於活動狀態時,所有其他單元都處於非活動狀態。如果我們假設五個階段(IF、OF、EX、MA、RW)中的每一個都需要相同的時間,那麼在任何時刻,大約80%的電路都是空閒的!這代表了計算能力的浪費,空閒資源絕對不是一個好主意。