圖解計算機內部的高速公路 —— 匯流排系統

本文已收錄到 GitHub · AndroidFamily,有 Android 進階知識體系,歡迎 Star。技術和職場問題,請關注公眾號 [彭旭銳] 進 Android 面試交流群。

前言

大家好,我是小彭。

在之前的文章中,我們聊到了計算機的馮·諾依曼計算機架構,計算機由五大部件組成。那麼,計算機的五大部件是如何連線成一個整體的呢?這就需要依賴匯流排系統。

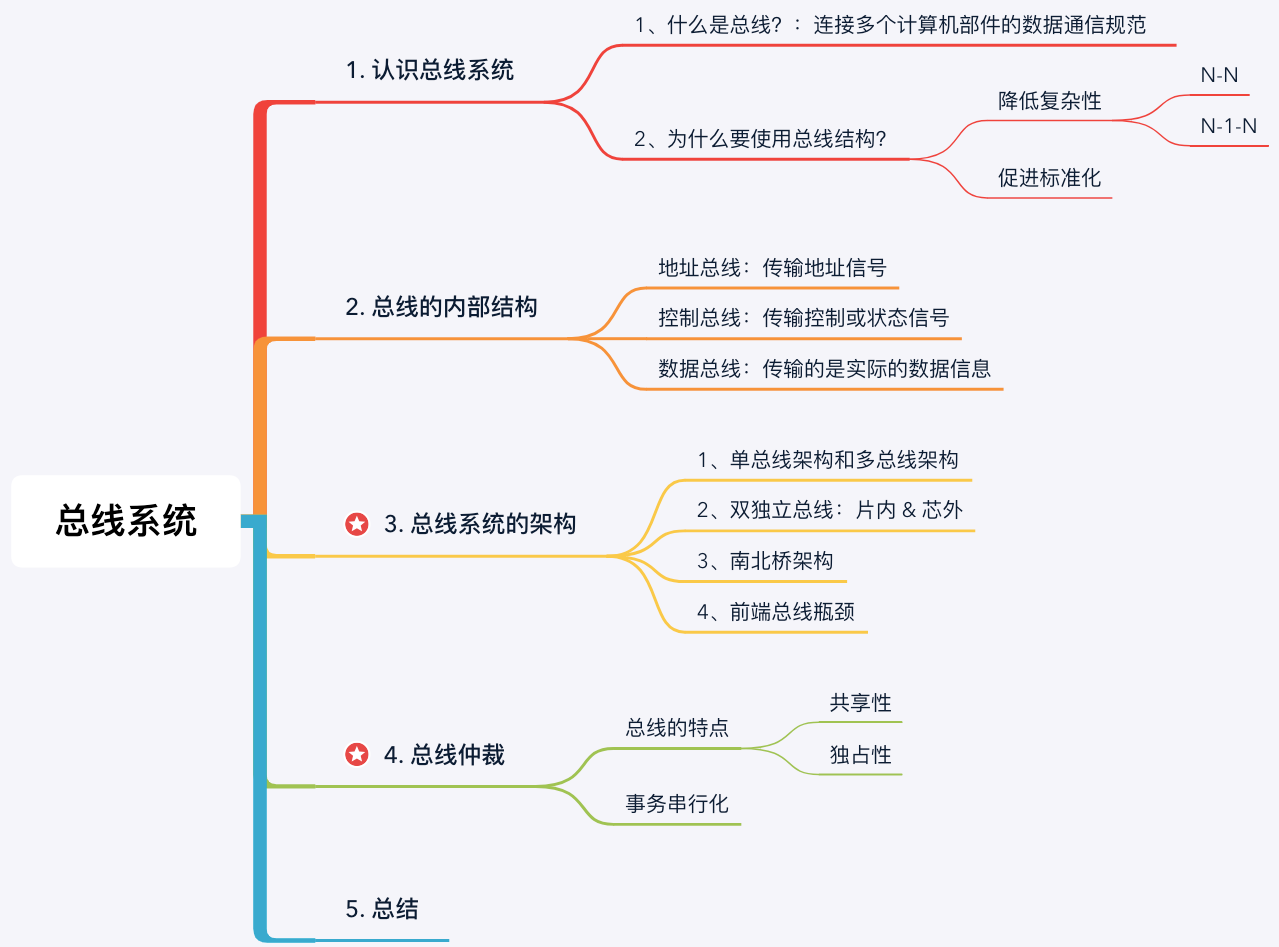

學習路線圖:

1. 認識計算機匯流排系統

1.1 什麼是匯流排?

在馮·諾依曼計算機架構中,計算機由控制器、運算器、記憶體、輸入裝置和輸出裝置五個部分組成,而這五個部分必須進行 「連線」 起來相互通訊才能形成一個完整的整體。 匯流排就是連線多個計算機部件的資料通訊規範。

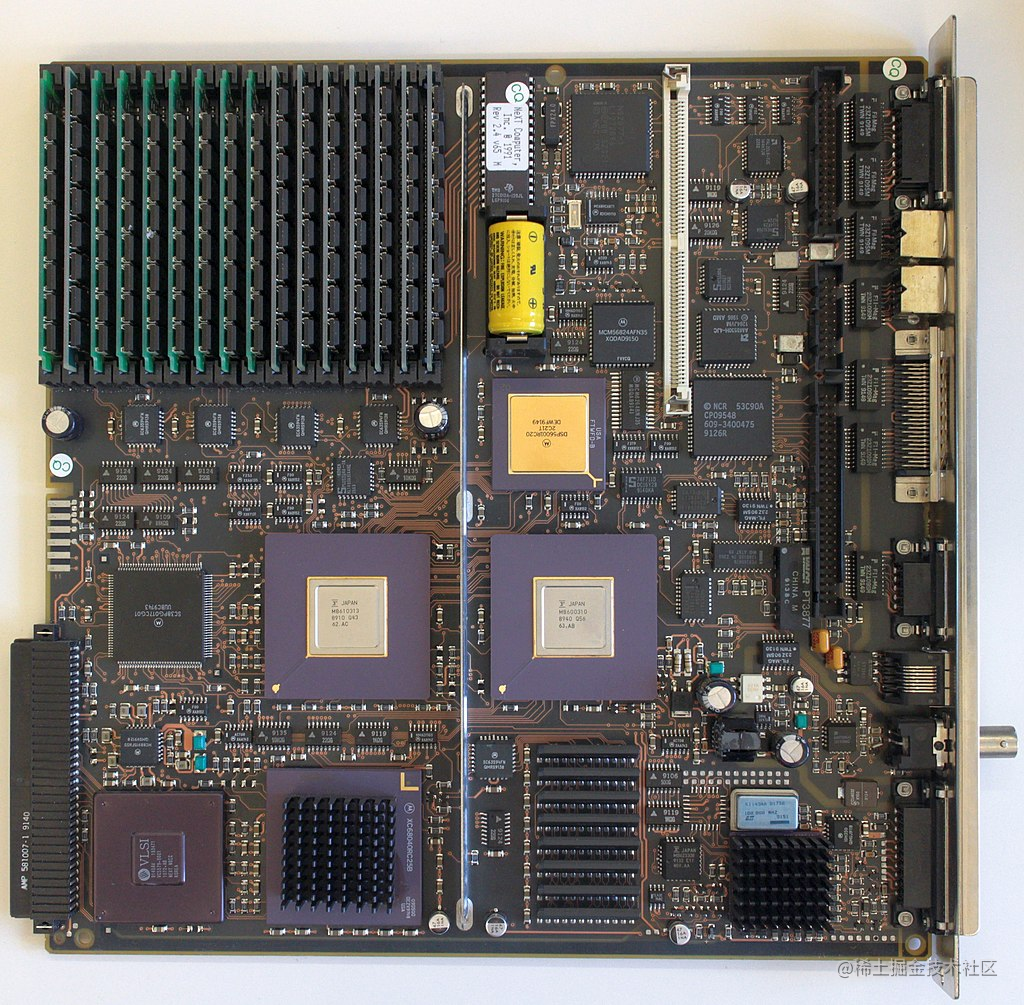

PC 計算機主機板

—— 圖片參照自 Wikipedia

1.2 為什麼要使用匯流排結構?

先解釋一下為什麼現代的計算機系統要採用匯流排結構:

- 原因 1 - 降低複雜性: 這個設計思路跟軟體開發中的中介者模式是相同的。匯流排結構將

N-N網型拓撲結構簡化為N-1-N匯流排型結構或星型+匯流排型拓撲結構,不僅整體的系統結構清晰許多,可以提高系統穩定性。而且需要使用的佈線數目也減少了,製造成本也更低; - 原因 2 - 促進標準化: 匯流排結構提供了一個標準化的資料交換方式,各個硬體按照匯流排的標準實現介面,而無需考慮對方介面或匯流排的工作原理,有利於各個部件模組化設計。

網狀拓撲和匯流排拓撲對比

2. 匯流排的內部結構

匯流排本身的電路功能,又可以拆分成 3 部分:

- 1、地址匯流排(Address Bus,AB): 地址匯流排傳輸的是地址訊號。地址匯流排是單向的,地址資訊只能從主裝置發往從裝置。地址匯流排寬度也決定了一個 CPU 的定址能力,即多大可以存取多少資料空間。舉個例子,32 位地址匯流排可以定址 4GB 的資料空間;

- 2、控制匯流排(Control Bus,CB): 控制匯流排傳輸控制或狀態訊號。控制匯流排是雙向的,訊號可以從主模組發往從模組,也可以從從模組發往主模組(例如 CPU 對記憶體的讀寫控制訊號,例如 I/O 裝置對 CPU 中斷請求訊號);

- 3、資料匯流排(Data Bus,DB): 資料匯流排傳輸的是實際的資料資訊。資料匯流排是雙向的,資料可以從主模組發往從模組(例如 CPU 向記憶體的寫入操作),也可以從從模組發往主模組(例如 CPU 向記憶體的讀取操作)。

舉個例子,當 CPU 要從記憶體讀取資料時,三類匯流排的工作過程概要如下:

- 1、CPU 通過地址匯流排傳送要存取的儲存單元的地址資訊;

- 2、CPU 通過控制匯流排傳送讀控制訊號;

- 3、記憶體通過資料匯流排傳送指定儲存單元上的資料,從 CPU 的視角就是讀取。

匯流排內部結構

3. 匯流排系統的架構

理解了匯流排的概念後,我們先來看匯流排系統的整體架構,現代計算機中的匯流排大多采用分層次多匯流排架構。

3.1 單匯流排架構和多匯流排架構

在早期計算機中,會使用單一匯流排來連線計算機的各個部件,這種結構叫單匯流排架構。這種結構實現簡單,但缺點有 2 個:

- 缺點 1: 計算機不同元件之間的速度差較大,例如 CPU 與記憶體或 I/O 裝置的速度差非常大,當傳輸資料量很大時,CPU 經常需要等待;

- 缺點 2: 所有的訊號都要經過同一個共用的匯流排,不允許兩個以上的部件同時傳輸訊號。

單匯流排架構

因此,單匯流排系統很容易形成系統的效能瓶頸,就算是增大匯流排的頻寬也無法從根本上解決系統性缺陷。目前,單匯流排結構只出現在微型計算機中。大多數現代計算機都採用了分層次多匯流排結構,所有的設計思路都是圍繞單匯流排架構存在的 2 個缺點展開的:

- 應對缺點 1: 將高速部件和低速部件分為不同層級,不同層級之間使用獨立的匯流排,減少高速部件對低速部件的等待;

- 應對缺點 2: 增加多條匯流排,使得資料可以同時在多個部件之間傳輸。

3.2 雙獨立匯流排:片內 & 片外

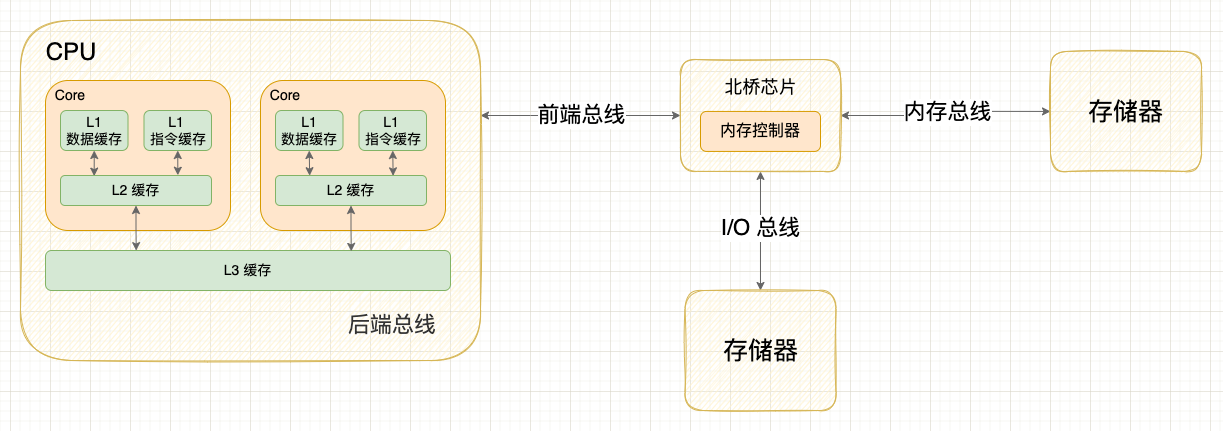

現代 CPU 中通常會使用快取記憶體,由於 「CPU-快取記憶體」 和 「CPU - 記憶體」 的速度差非常大,計算機系統選擇在 CPU 晶片內和 CPU 晶片外使用 雙獨立匯流排(Dual Independent Bus,DIB):

- 前端匯流排(Front Side Bus,FSB): CPU 與外部連線的匯流排(即 CPU 連線北橋晶片的匯流排);

- 後端匯流排(Back Side Bus,BSB): 也叫本地匯流排(Local Bus)或片內匯流排(On-chip Bus),是 CPU 晶片內部獨立使用的匯流排。CPU 晶片內部一個或多個核心、Cache 之間的通訊將不需要佔用晶片外的系統匯流排。

提示: 前端匯流排和系統匯流排的概念容易混淆,不同資料的說法不一。我的理解是:前端匯流排是 「特指」 某些 Intel CPU 架構中,CPU 晶片與外部連線的這條匯流排,而系統匯流排 「泛指」 連線計算機各個部件的所有匯流排。小彭在後續專欄內容都會按照此理解討論。

前端匯流排和後端匯流排

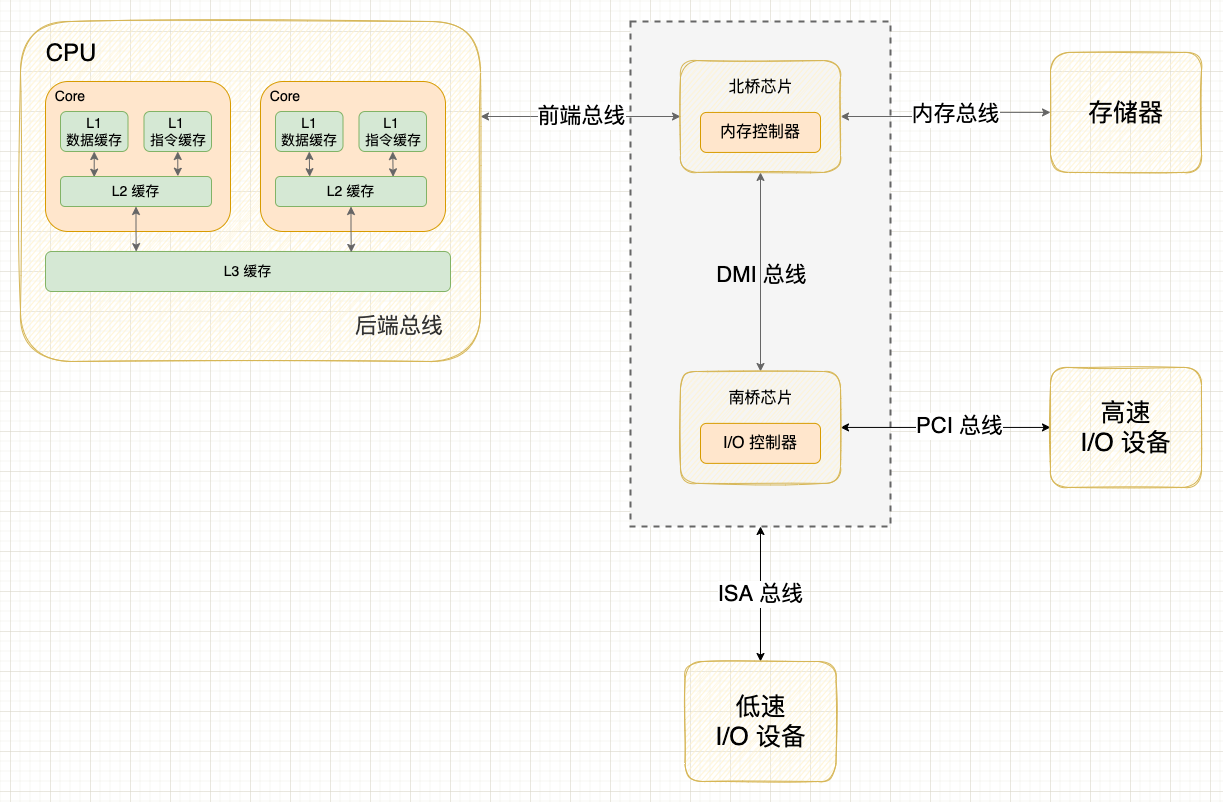

3.3 南北橋架構

南北橋架構是 Intel 提出的匯流排架構,也叫 Hub 架構 。它將計算機部件分為高速部件和低速部件兩類,分為北橋晶片組合和南橋晶片組,中間用兩顆橋晶片連線。使用南北橋設計有 2 個優點:

- 1、緩衝功能: 南北橋晶片實現了兩類匯流排訊號速度緩衝;

- 2、橋接功能: 南北橋晶片實現了兩類匯流排訊號的轉換,有利於系統升級換代。例如在升級 CPU 時,只需要改動 CPU 和北橋晶片,其它南橋部分不需要改動。

南北橋架構

- 北橋晶片(Northbridge): 北橋處理高速訊號。北橋晶片連線的裝置都是高速傳輸裝置,包含 CPU、GPU、記憶體與南橋的通訊。北橋晶片也是 CPU 與外部連線的紐帶;

- 南橋晶片(Southbridge): 南橋處理低速訊號。南橋晶片連線的大多是 I/O 裝置,例如 PCI 匯流排、USB 介面卡、顯示卡介面卡、硬碟控制器;

- 記憶體控制器(Memory Controller): 管理 CPU 和記憶體之間的匯流排資料傳輸,控制著記憶體的讀取和寫入訊號,並且定時重新整理 DRAM 內的資料(DRAM 的儲存單元包含電容,會自動漏電);

- 記憶體匯流排(Memory Bus): 連線北橋晶片與記憶體的匯流排;

- DMI 匯流排(Direct Media Interface): 連線北橋晶片和南橋晶片的專用匯流排;

- I/O 匯流排: 連線南橋晶片與 I/O 裝置的匯流排;

- PCI 區域性匯流排: 連線高速 I/O 裝置的標準;

- ISA 區域性匯流排: 連線低速 I/O 裝置的標準。

3.4 前端匯流排瓶頸

前端匯流排是 CPU 連線外界的唯一通道,因此前端匯流排的資料傳輸能力對於計算機系統的整體效能影響非常大。 近年來隨著 CPU 主頻不斷提升,前端匯流排頻率卻一直跟不上後端匯流排頻率,從而出現效能瓶頸。

為了解決這個問題,傳統的南北橋架構被重新設計,北橋晶片的功能幾乎都移動到 CPU 內部變成 「片上北橋」。前端匯流排被淘汰,CPU / 片上北橋繼續使用 DMI 連線南橋或 PCH 等外部裝置。

4. 匯流排仲裁

匯流排既有共用性又有獨佔性,聽起來有點矛盾,其實是表現的時機不一樣:

- 共用性: 匯流排的共用性是指匯流排對所有連線的裝置共用,主從模組能通過匯流排傳輸資料。

- 獨佔性: 匯流排的獨佔性是指同一時刻,只允許一個部件佔有匯流排的控制權,這個部件就是主模組,主模組可以與一個或多個從模組通訊,但同一時刻只有一個主模組。

匯流排的獨佔性天然地將事務序列化: 如果多個部件同時向匯流排發出匯流排事務,匯流排仲裁(Bus Arbitration)單元會對競爭做出總裁,未獲勝的事務只能等待獲勝的事務處理完成後才能執行。當其中一個匯流排事務在執行時,其他匯流排事務都會被禁止。

5. 總結

-

1、匯流排就是連線多個計算機部件的資料通訊規範;

-

2、匯流排的電路結構由地址匯流排、控制匯流排和資料匯流排組成。舉個例子,當 CPU 要從記憶體讀取資料時,三類匯流排的工作過程概要如下:

- CPU 通過地址匯流排傳送要存取的儲存單元的地址資訊;

- CPU 通過控制匯流排傳送讀控制訊號;

- 記憶體通過資料匯流排傳送指定儲存單元上的資料,從 CPU 的視角就是讀取。

-

3、現代計算機中的匯流排大多采用分層次多匯流排架構,由片內+片外雙獨立匯流排平衡快取記憶體和記憶體的速度差,由南北橋架構平衡高速部件和低速部件的速度差;

-

4、由於前端匯流排瓶頸和晶片整合度提高,南北橋架構逐漸被片上系統替代;

-

5、匯流排具有共用性和獨佔性,當多個部件同時向匯流排發出匯流排事務,匯流排天然地將事務序列化;

參考資料

- 深入淺出計算機組成原理(第 42 講) —— 徐文浩 著,極客時間 出品

- 計算機組成原理教學(第 3 章) —— 尹豔輝 王海文 邢軍 著

- 10分鐘速成課 電腦科學 —— Carrie Anne 著

- System Bus —— Wikipedia

- Northbridge (computing) —— Wikipedia

- Southbridge (computing) —— Wikipedia

- HyperTransport —— Wikipedia

- Intel QuickPath Interconnect —— Wikipedia

- Arbiter (electronics) —— Wikipedia