記憶體、I/O組織、微處理器

重點知識

- 記憶體的內部結構及存取方法

- 記憶體分段以及記憶體中的邏輯地址和實體地址

- I/O埠組織及編址方式

- 時序和匯流排操作以及系統的工作方式和特點。

記憶體組織

- 8086有20根地址線,可定址的記憶體空間為1MB,地址範圍為0220-1(00000HFFFFFH)。

- 記憶體內部按位元組進行組織,兩個相鄰的位元組被稱為一個「字」;儲存資料以位元組為單位,將在記憶體中順序存放。

- 若按字存放,一個字的低位元組放在低地址,高位元組放高地址。並以低地址,做該字地址。

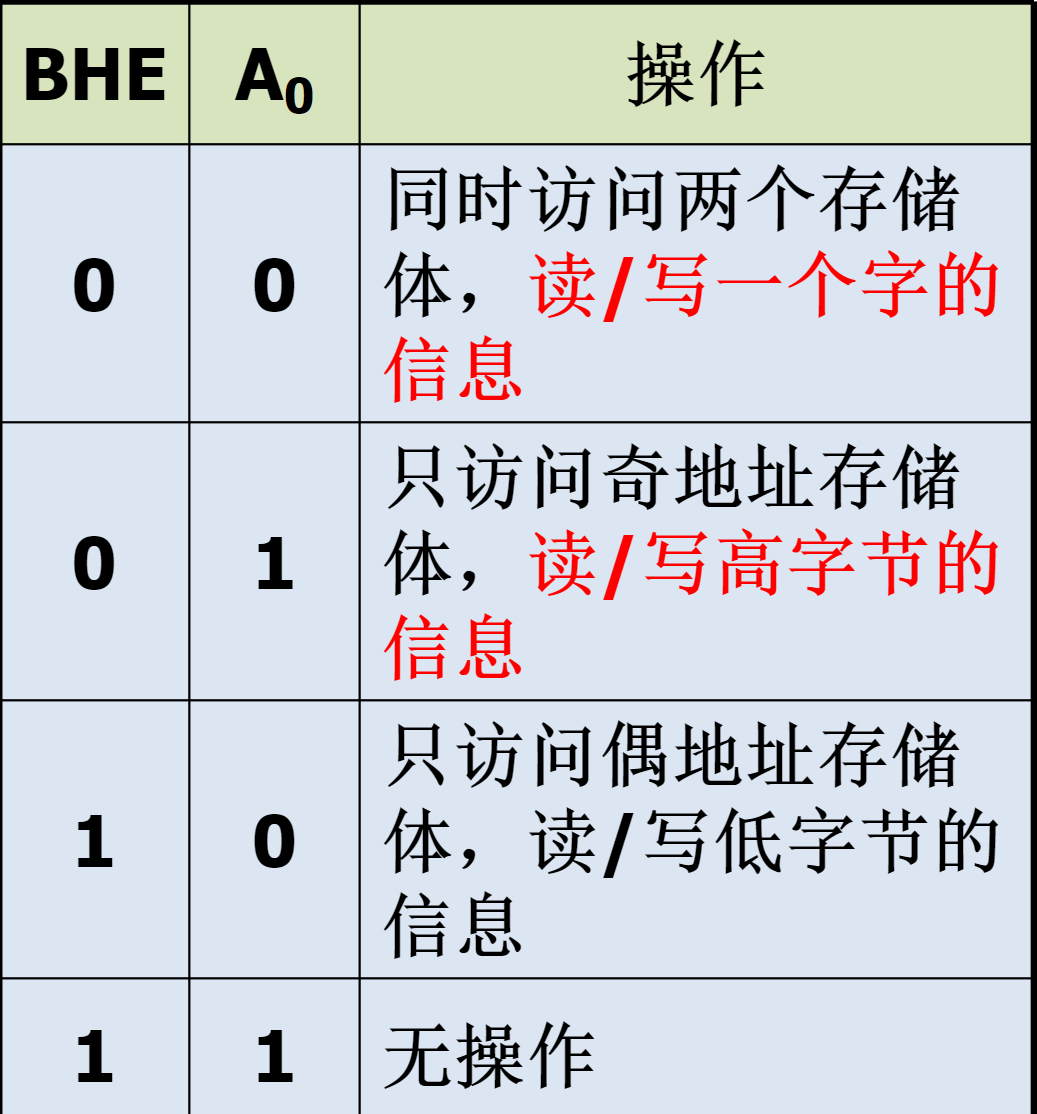

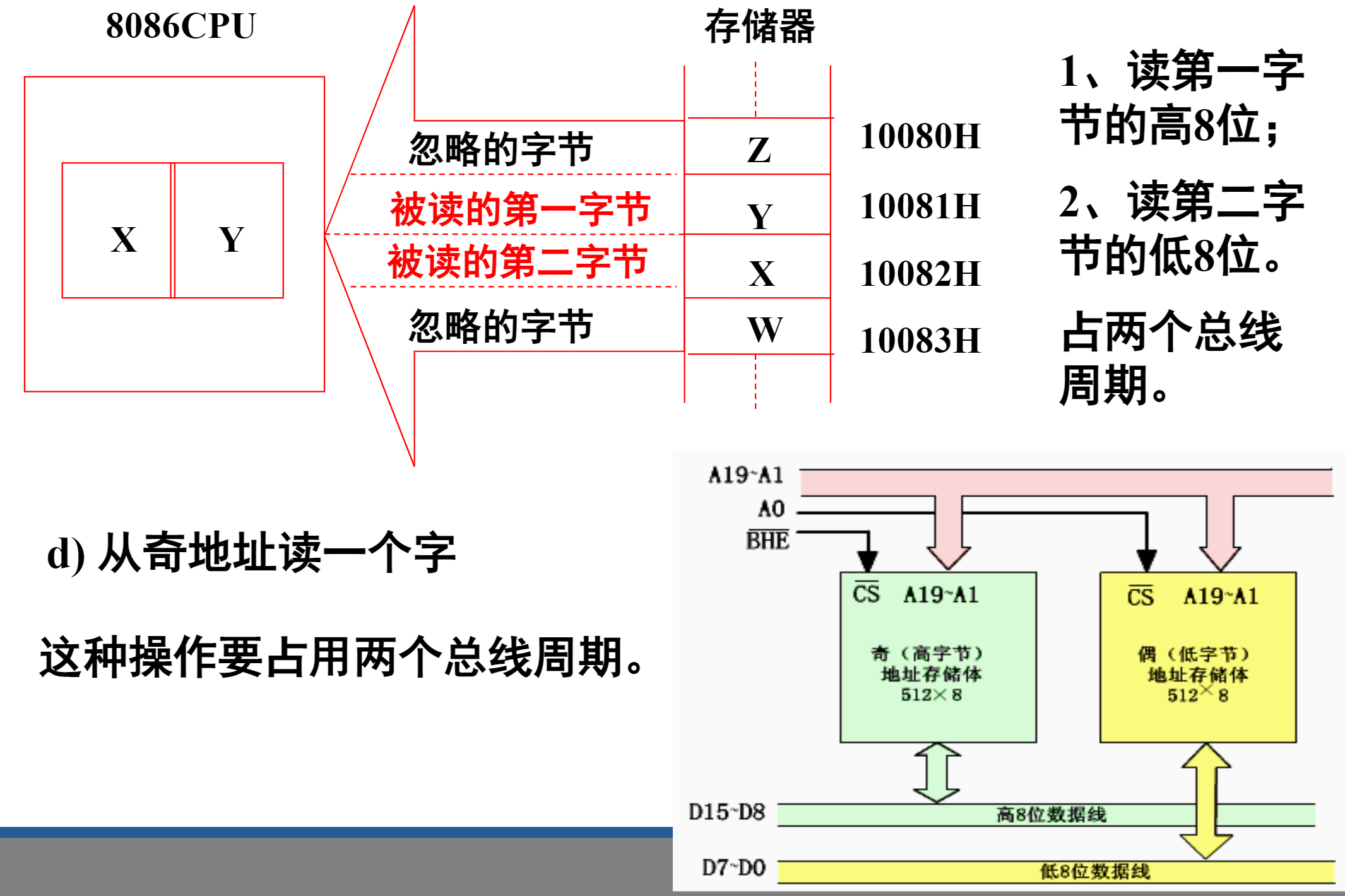

- 若一個字從偶地址開始存放,稱規則存放或對準存放,這樣存放的字稱為規則字或對準字。 對規則字的存取可在一個匯流排週期完成,非規則字的存取需要兩個匯流排週期。

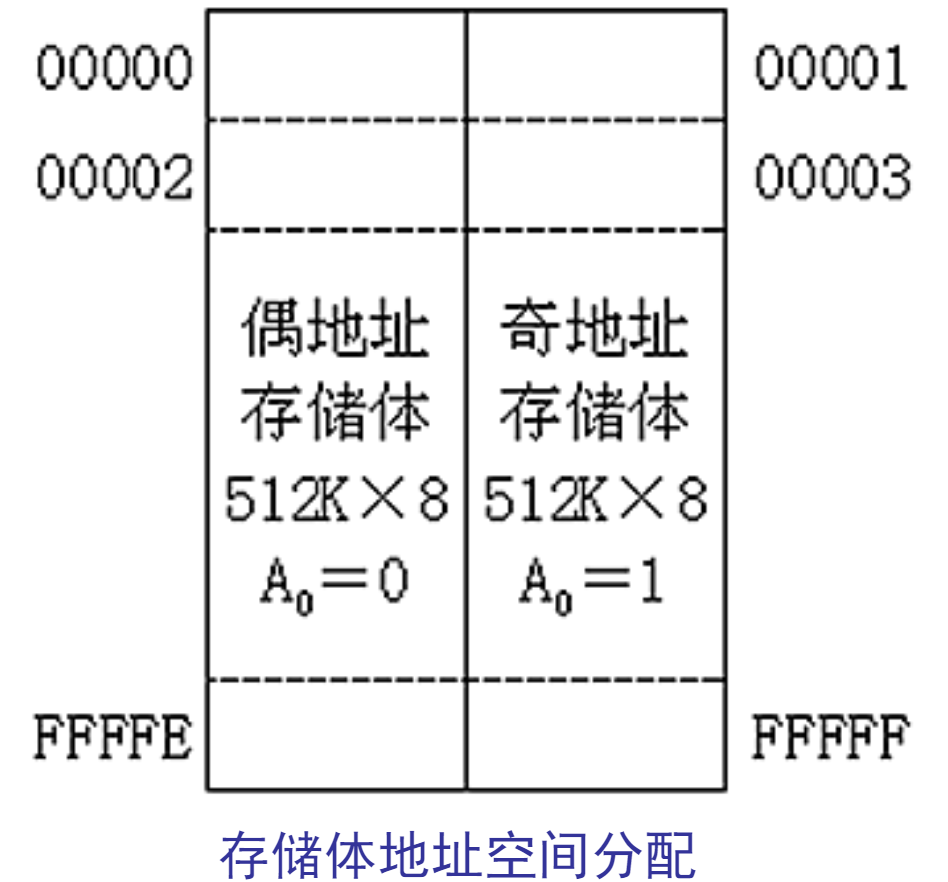

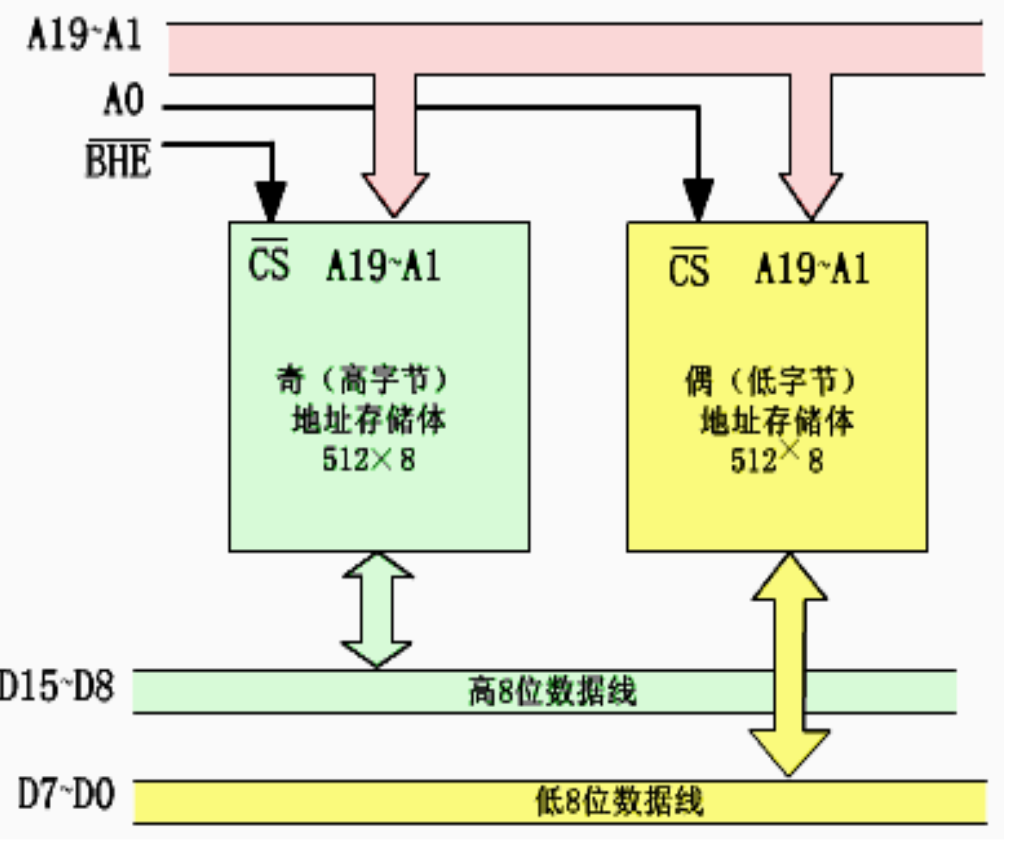

1M位元組的記憶體,儲存空間被分成兩個儲存體,每個儲存體512K位元組。 兩個儲存體之間採用位元組交叉編址方式。

與資料匯流排D15~D8相連的儲存體由奇地址單元組成。稱高位元組儲存體或奇地址儲存體。 用BHE訊號作為選擇訊號;

記憶體分段

- 採用20位地址線來定址。最大可直接定址的記憶體實體地址空間220=1MB 。CPU內暫存器都只有16位元,只能定址64KB(216位元組)

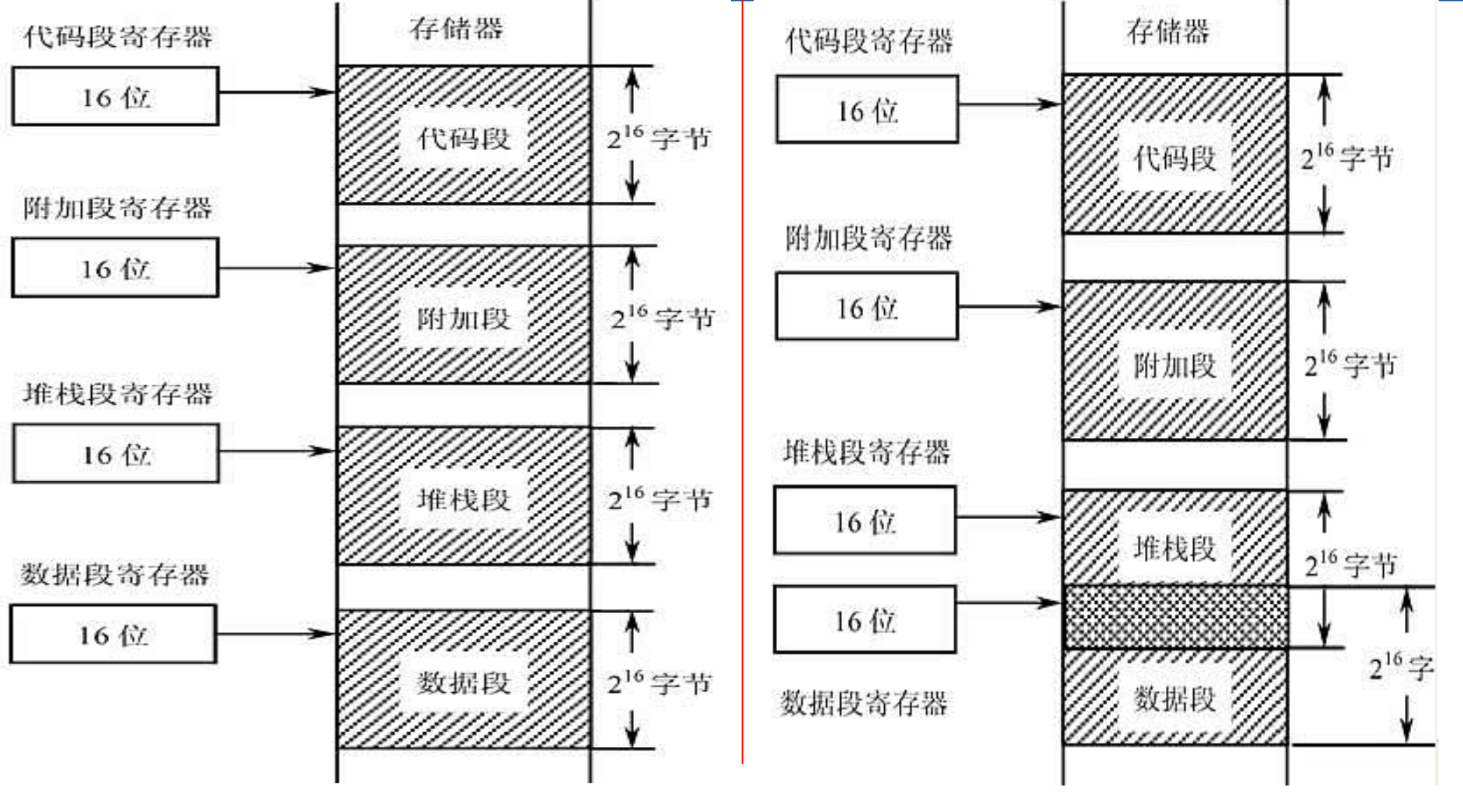

- 把整個儲存空間1MB,分成若干邏輯段, 每個邏輯段的容量最大為64KB,可分為16個互不重疊的邏輯段。

- 邏輯段分為程式碼段、資料段、堆疊段和附加段四種型別;

- 各個邏輯段在整個儲存空間中浮動,可相連,可重疊,可分開一段距離。

允許各個邏輯段在整個儲存空間浮動,可以相連,也可以重疊,可以分開一段距離

記憶體地址

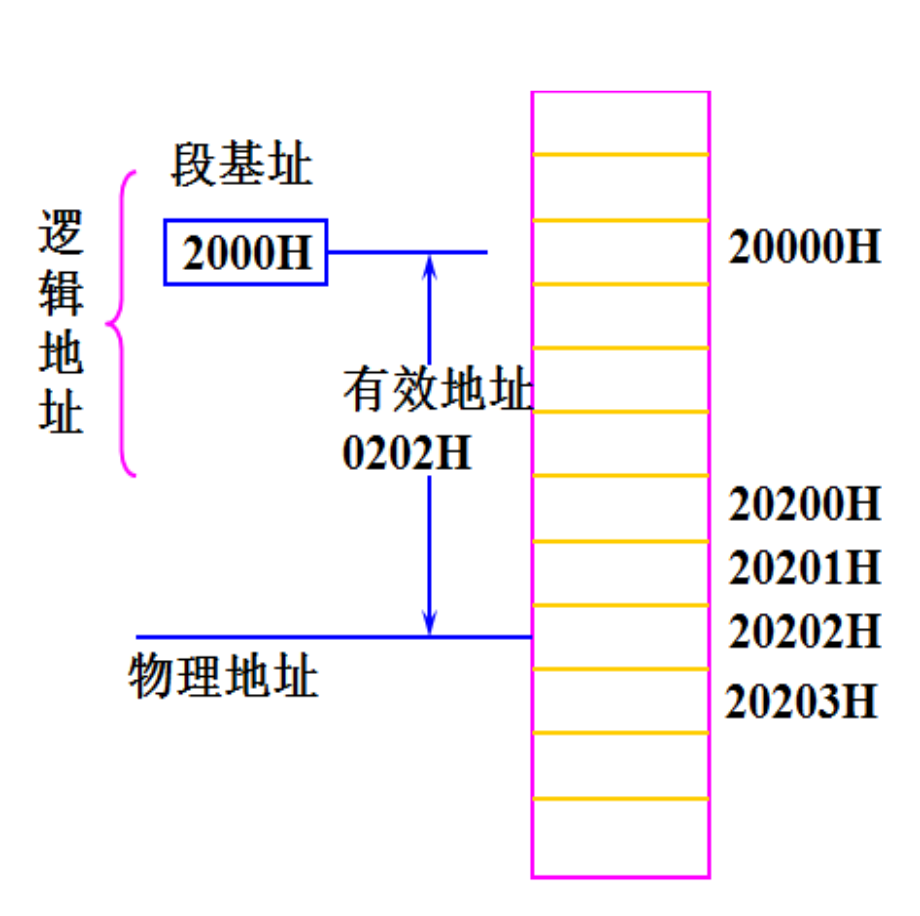

- 段地址:一般存放在段暫存器中(CS、SS、DS和ES)。是指一個段的起始地址,最低4位元為零, (2000H)

- 偏移地址(有效地址):要定址的記憶體單元距本段段首的偏移量。同一個段內,各個儲存單元的段地址是相同的,偏移地址是不同的。(0202H)

- 邏輯地址:在程式中使用的地址,由段地址和偏移地址兩部分組成。表示形式為「段地址:偏移地址」。(2000:0202H)

- 實體地址:儲存單元的實際地址(20位)。實體地址與儲存單元是一一對應關係。(20202H)

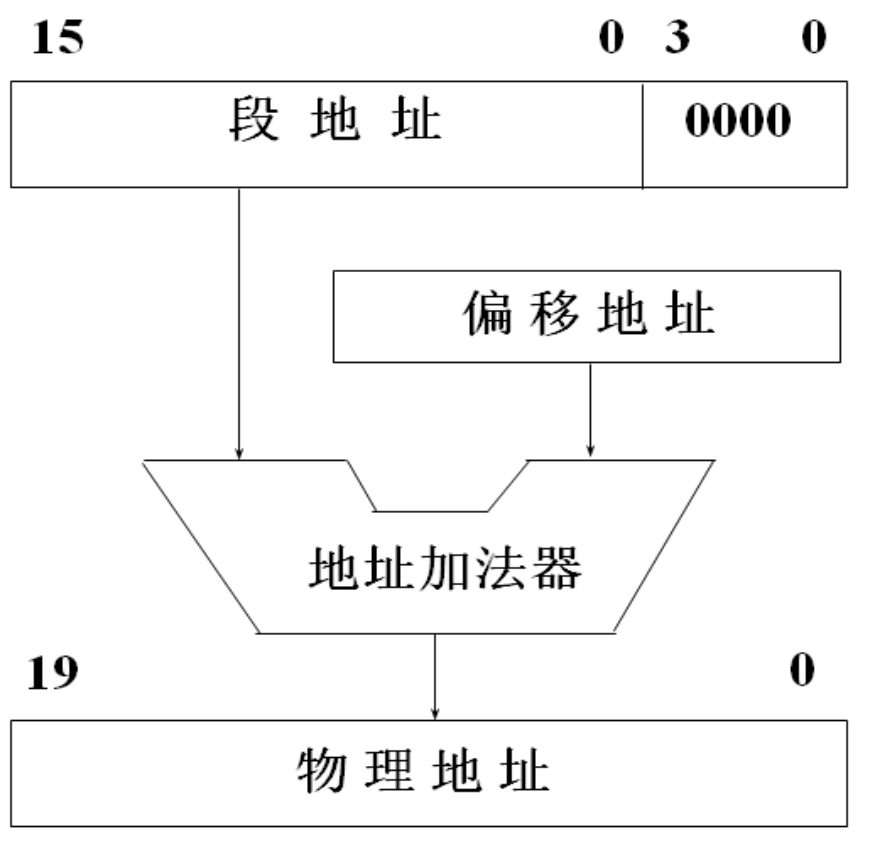

實體地址的計算方法:

實體地址

=段暫存器內容×10H + 偏移地址

=段暫存器內容左移4位元+偏移地址

- 取指令實體地址=(CS)×10H+(IP)

- 堆疊操作實體地址=(SS)×10H+(SP)/(BP的表示式)

- 記憶體運算元實體地址=(DS)/(ES)×10H+偏移地址

例:記憶體有由10個位元組組成的資料區,起始地址1100H:0020H。計算該資料區在記憶體的首末單元實際地址。

解:記憶體資料區邏輯地址1100H:0020H,可知該資料段地址:(DS)=1100H,偏移地址為0020H,對應實體地址:

PA=(DS)×10H+0020H

=1100H×10H+0020H

= 11020H

即該資料區在記憶體中首單元的實體地址(實際地址)為11020H。

儲存空間中10個位元組對應10個地址,應占用從起始地址0單元到9號單元的位置,該資料區在記憶體中末單元實體地址(實際地址):

PA = 11020H+0009H

= 11029H

所以:本題中10個位元組組成的資料區,在記憶體首單元實際地址是11020H,記憶體末單元實際地址是11029H。

專用和保留的記憶體單元

8086系統規定:

1)00000H~003FFH(共1KB):存放中斷向量表,中斷服務程式的入口地址。每個中斷向量佔4位元組,前2位元組存放中斷服務程式的入口偏移地址(IP),後2位元組存放中斷服務程式的入口段地址(CS)。1KB區域可存放256箇中斷服務入口地址。當系統啟動、引導後,這個區域的中斷向量就被建立起來。

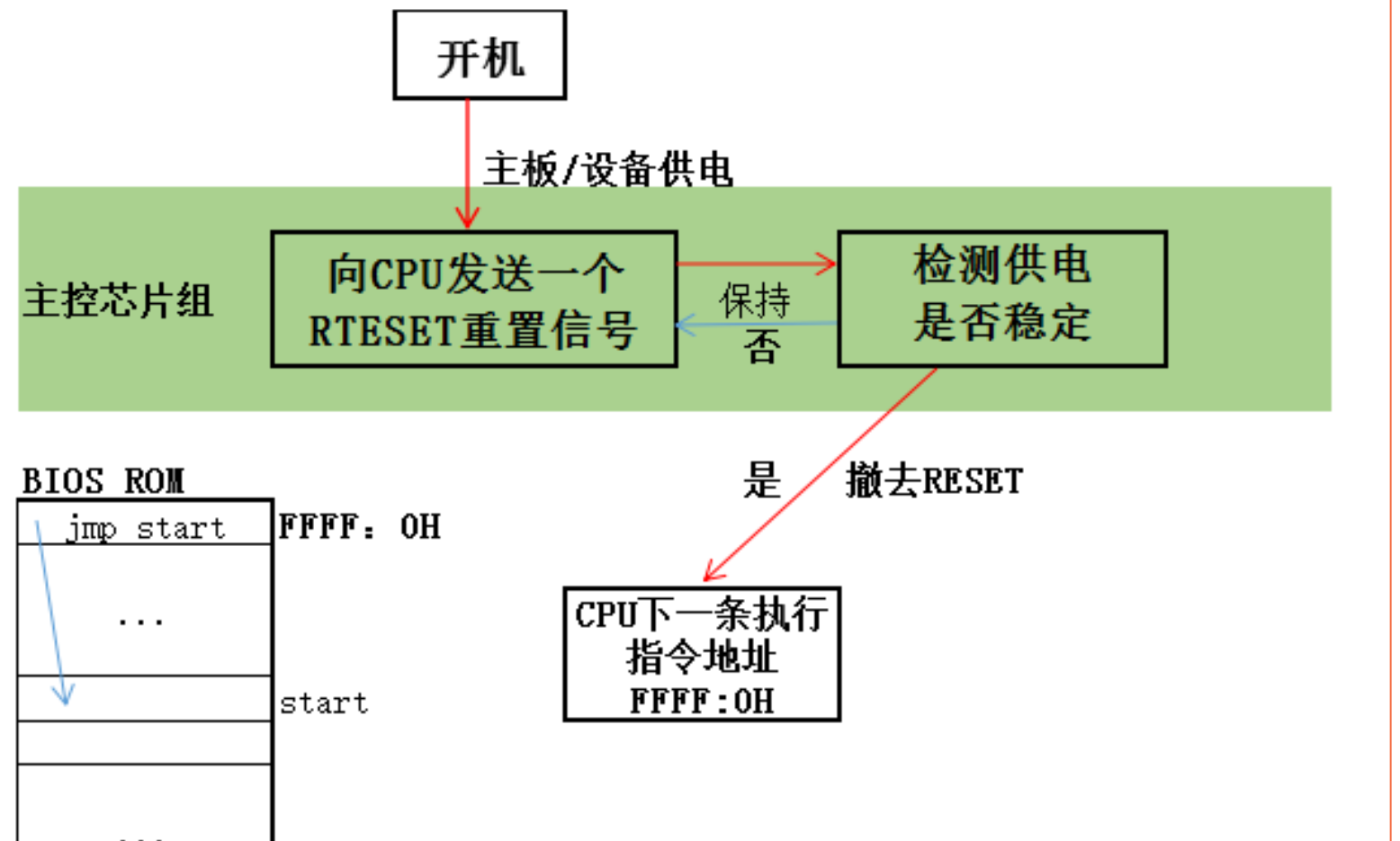

2)FFFF0H~FFFFFH(共16B):存放一條無條件轉移指令,使系統在上電或復位時,自動跳轉到系統的初始化程式。

系統啟動後,CS=0FFFFH,IP=0000H,初始指令的實體地址為0FFFF0H,存放一條無條件轉移指令,即轉移到系統初始化程式部分。

FFFF:0000H:是BIOS(Basic Input Output System) ROM的起始地址,但不是有效指令開始地址。Jmp指令跳轉的START是真正進行BIOS程式起始地址

I/O埠組織

8086微處理器用地址匯流排的低16位元作為對8位元I/O埠的定址線,所以8086可存取的8位元I/O埠有216(65536)個。兩個編號相鄰的8位元埠可以組成一個16位元的埠。一個8位元的I/O裝置可以連線在資料匯流排的高8位元,也可連線低8位元。

1、統一編址: 把I/O埠看作記憶體單元,每個埠佔用一個儲存單元的地址。CPU存取記憶體的指令和各種定址方式都可用於定址I/O埠。

2、獨立編址: 埠單獨編址構成一個I/O空間,不佔用記憶體地址。有專門輸入/輸出指令(IN和OUT)。使用16條地址線A15~A0來存取I/O埠,可存取最多64K容量的8位元埠或32K容量的16位元埠。

8086CPU的操作是在時鐘CLK統一控制下進行的。 8086CPU由外部的一片8284A時鐘訊號發生器提供主頻為5MHz的時鐘訊號。

- 8284A能產生8086所需的系統時鐘訊號,即系統主頻。

- 8284A還可對外界輸入準備就緒訊號RDY和RES進行同步操作。

- 輸出READY訊號作為8086的就緒訊號READY;輸出RESET訊號作為8086的復位訊號RESET。

8086CPU的匯流排週期和工作方式

8086CPU經外部匯流排對記憶體或I/O埠進行一次資訊的輸入或輸出過程,稱為匯流排操作,執行該操作所需要的時間,稱為匯流排週期。

1個匯流排週期,包含4個T時態。T1,T2,T3,T4。

不同的匯流排操作需要不同的匯流排訊號,對這些訊號的變化進行時間順序的描述稱為「匯流排時序」。

CPU的操作是在時鐘統一控制下進行。描述匯流排操作的微處理器時序有三級

指令週期 → 匯流排週期 → 時鐘週期

- 指令週期:計算機完成對一條指令的讀取並執行所需的時間。

- 匯流排週期:CPU經外部匯流排對記憶體或I/O埠進行一次資訊的輸入或輸出過程所需要的時間。

- 時鐘週期 T: CPU的基本時間計量單位,由主頻決定。

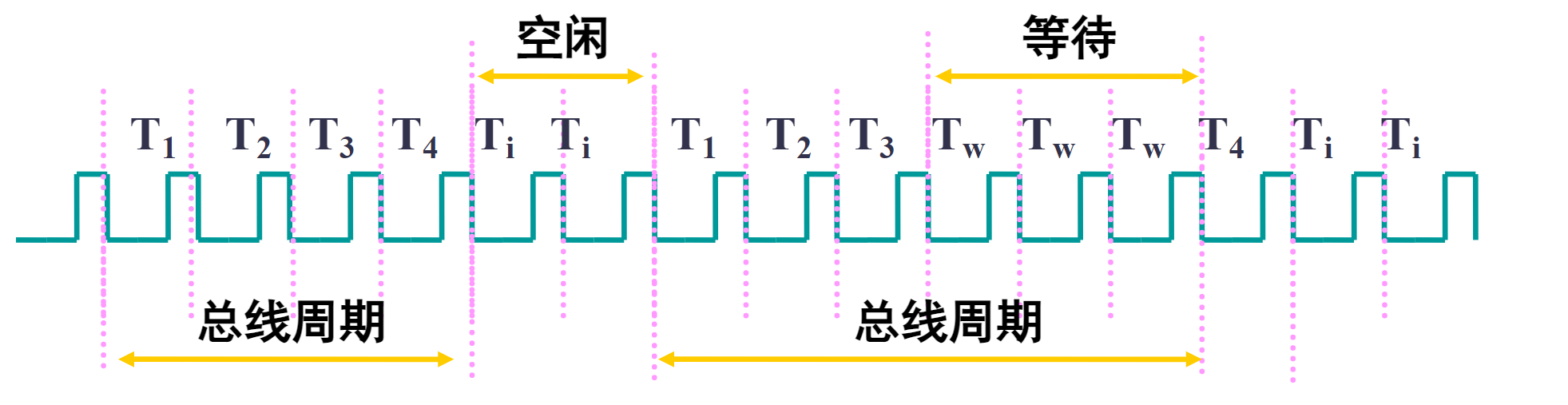

- 等待週期TW:當慢速的記憶體或I/O介面,無法在3個時鐘週期內完成資料讀寫操作時,在匯流排週期中插入等待週期。

- 空閒週期 TI:是指在二個匯流排週期之間的時間間隔(匯流排處在空閒狀態)。無匯流排操作時進入空閒週期。

8086CPU由外部的一片8284A時鐘訊號發生器提供主頻為5MHz的時鐘訊號。

- 基本匯流排週期:由4個T狀態組成:T1、T2、T3、T4。

- 等待時鐘週期Tw:在匯流排週期的T3和T4之間插入。

- 空閒時鐘週期Ti:在兩個匯流排週期之間插入。

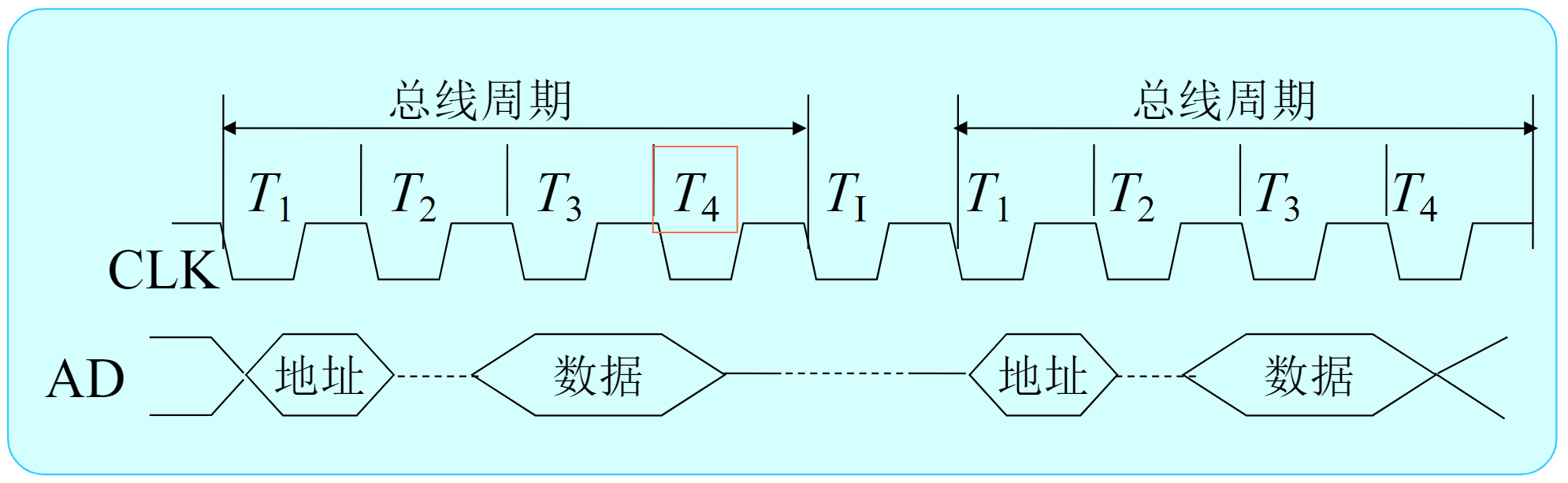

8086CPU採用匯流排複用操作方式,16位元資料匯流排和地址匯流排的低16位元是共用的,典型的匯流排週期如圖

在沒有插入等待時鐘週期TW的情況下,匯流排週期由4個時鐘週期組成,即圖中T1、T2、T3、T4

- 在T1期間:CPU把記憶體或外設的地址放到匯流排上。

- T2期間:分時複用的地址/資料匯流排處於高阻態,以便為讀入或寫出資料作準備。

- 在T3和T4期間:讀或寫的資料出現在匯流排上,以使完成讀或寫的操作。

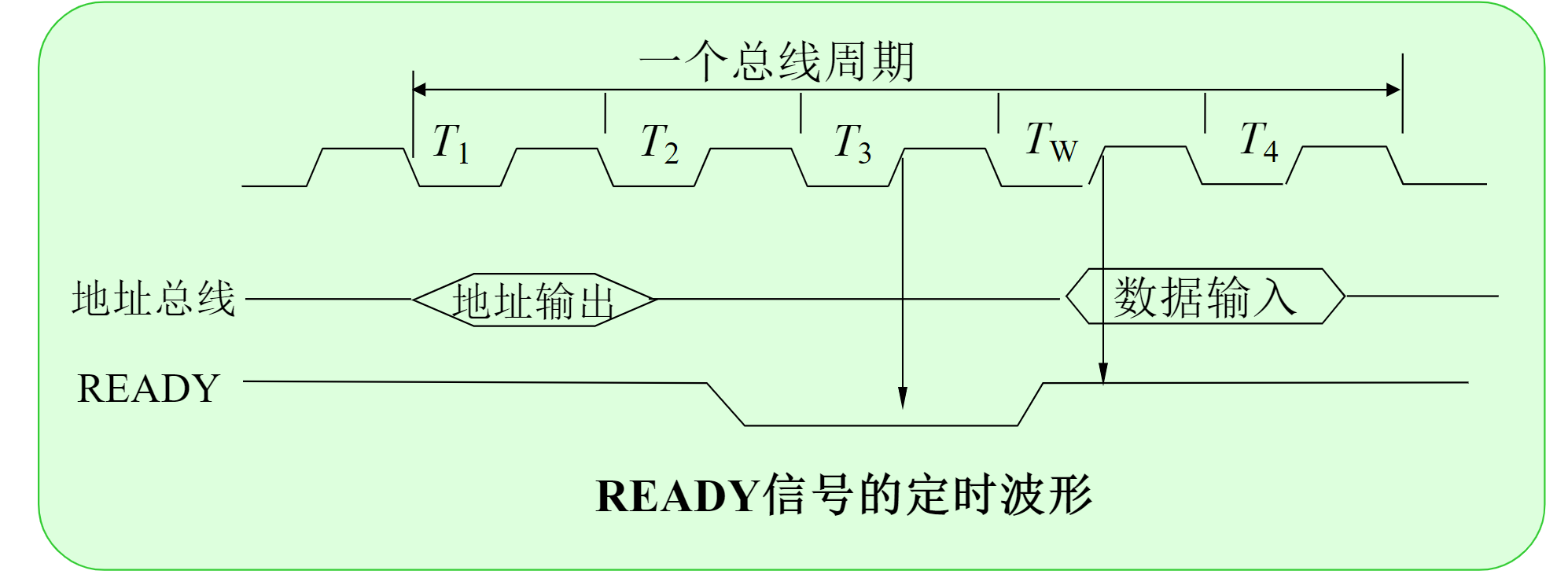

等待週期TW:

如果在T3週期結束之前,記憶體或外設未準備好資料傳送,就要輸入CPU的READY線使之變低電平,從而在T3和T4之間插入一個或多個TW等待週期,直到READY變高,轉入T4週期,完成讀寫操作。

- 任何指令的取指階段都需要記憶體讀匯流排週期,讀取的內容是指令程式碼

- 任何一條以儲存單元為源運算元的指令都將引起記憶體讀匯流排週期,任何一條以儲存單元為目的運算元的指令都將引起記憶體寫匯流排週期

- 只有執行IN指令才出現I/O讀匯流排週期,執行OUT指令才出現I/O寫匯流排週期

- CPU響應可遮蔽中斷時生成中斷響應匯流排週期

為了適應各種場合的要求,8086CPU在設計中提供了兩種工作模式,即最小模式和最大模式。

通過CPU的第33條引腳 MN/MX 來控制。

(1)最小工作模式(MN/MX =1):適用於單微處理器組成的小系統,系統中通常只有一個微處理器,所有的匯流排控制訊號都直接由8086CPU產生,系統中的匯流排控制邏輯電路被減到最少。

(2)最大工作模式(MN/MX=0):此時,系統中存在兩個或兩個以上的微處理器,其中有一個主處理器8086,其他處理器稱為協處理器。

舉例:8086最小模式基本時序

- 匯流排讀週期 8086CPU進行記憶體或I/O埠讀操作時,匯流排進入讀週期;

- 匯流排寫週期 8086CPU進行記憶體或I/O介面寫操作時,匯流排進入寫週期。

- 中斷響應週期 當8086的INTR引腳上有高電平訊號,且中斷標誌IF=1時,8086CPU在執行完當前指令後,進入中斷響應週期。響應中斷時CPU將執行兩個中斷響應週期。

- 匯流排響應週期 當系統中有其它的匯流排主裝置請求匯流排控制時, CPU進入匯流排響應週期。

- 系統復位週期 8086CPU的RESET引腳,可以用來啟動或再啟動系統

8086在最大與最小模式下的主要區別是增加了一個8288匯流排控制器。8288接受8086CPU的狀態訊號S2、S1和S0,經過變換和組合,由8288發出對記憶體和I/O埠的讀/寫訊號,對鎖存器8282及對匯流排收發器8286的控制訊號。

32位微處理器

80386的主要特點

- 80386微處理器擁有32位元資料匯流排和32位元地址匯流排,可直接定址4GB(232)的物理儲存空間,同時具有虛擬儲存的能力,虛擬儲存空間達64TB。記憶體採用分段結構,一個段最大可為4G位元組。

- 系統採用了流水線和指令重疊技術、虛擬儲存技術、片記憶體儲器管理技術、記憶體管理分段分頁保護技術等,使80386系統實現了多使用者多工操作,功能得到大大加強。

- 提供32位元的指令,可支援8位元、16位元、32位元的資料型別,具有8個通用的32位元暫存器,具有片內地址轉換的高速緩衝記憶體Cache。

- 提供32位元外部匯流排介面,最巨量資料傳輸速率為32Mbps。系統可同高速的DRAM晶片介面,支援動態匯流排寬度控制,能動態地切換32位元/16位元資料匯流排。

- 具有片內整合的記憶體管理部件MMU,可支援虛擬儲存和特權保護,可選擇片內分頁單元。片內具有多工機構,能快速完成任務的切換。

- 通過設定浮點協處理器80387實現資料高速處理,加快了浮點運算速度。

- 80386系統能在時脈頻率為12.5 MHz或16 MHz下可靠工作,指令的執行速度可達3~4MIPS以上。

80486的主要特性

- 80486是在複雜指令集計算機CISC技術的基礎上,首次採用了精簡指令集計算機RISC技術的80X86系列微處理器。

- 把浮點運算部件和高速緩衝記憶體Cache整合在晶片內,使運算速度和資料存取速度得到大大提高

- 80486增加了多處理器指令,增強了多重處理系統,片上硬體確保了超快取記憶體一致性協定,並支援多級超快取記憶體結構。

- 80486具有機內自測試功能,可以廣泛地測試片上邏輯電路、超快取記憶體和片上分頁轉換快取記憶體,支援硬體測試、Intel軟體和擴充套件的第三者軟體。

80486的基本結構

80486CPU的內部結構如圖所示,它包括匯流排介面部件、片內高速緩衝記憶體Cache、指令預取、指令譯碼、控制/保護、整數、浮點運算、分段和分頁等功能部件。80486將這些部件整合在一塊晶片上,既可以減少主機板空間,還可以提高CPU的執行速度。

Pentium系列微處理器

Pentium系列微型計算機的主要特點

- 高整合度,片內整合有310萬個電晶體。

- 時脈頻率高,從60MHz或66MHz發展到500MHz,700MHz和1500MHz。

- 資料匯流排頻寬增加,內部匯流排為32位元,外部資料匯流排寬度為64位元。

- 內採用分立的指令Cache和資料Cache結構,可無衝突地同時完成指令預取和資料讀寫。

- 採用RISC型超標量結構。超標量是指微處理器內具有多條指令執行流水線,以增加每個時鐘週期內可以執行的指令數,從而使微處理器的執行速度成倍提高。

- 高效能的浮點運算器。Pentium採用全新設計的增強型浮點運算器(FPU),使得它的浮點運算速度比80486DX要快3~5倍

- 雙重分離式快取記憶體。將指令快取記憶體與資料快取記憶體分離,各自擁有獨立的8KB快取記憶體。

- 增強了錯誤檢測與報告功能。內部增強了錯誤檢測與報告功能,特別引進了片功能冗餘檢測(FRC)。

- 64位元資料匯流排。Pentium為了大幅度提高資料傳輸速度而使用64位元的資料匯流排。

- 分支指令預測。處理器內部採用了分支預測技術,大大提高了流水線執行效率。

- 常用指令固化及微程式碼改進。把一些常用的指令改用硬體實現,不再使用微程式碼操作。

- 系統管理方式。具有實地址方式、保護方式、虛擬8086方式及具有特色的SMM(系統管理方式)。

- 軟體向上相容 80386/80486,可以在MS-DOS,Windows 95,Windows NT,OS/2,UNIX和Solaris等作業系統下執行。

Pentium微處理器的內部結構

Pentium微處理器的主要部件包括匯流排介面部件、指令快取記憶體器、資料快取記憶體器、指令預取部件(指令預取緩衝器)與轉移目標緩衝器、暫存器組、指令譯碼部件、具有兩條流水線的整數處理部件(U流水線和V流水線)、擁有加乘除運算且具有多用途電路的流水浮點處理部件FPU等。