微處理器效能簡介(8086)

微處理器效能簡介

微處理器職能:執行各種運算和資訊處理,控制各個計算機部件自動協調地完成系統規定的各種操作

典型微處理器的主要效能指標

主頻:微處理器的時脈頻率;

外頻:系統匯流排的工作頻率;

倍頻:微處理器主頻與外頻相差的倍數,主頻=外屏*倍頻

微處理器具有以下基本功能:

(1)指令控制:使計算機中的指令或程式嚴格按照規定的順序執行。

(2)操作控制:將計算機指令產生的控制訊號送往相應的部件,控制這些部件按指令的要求完成規定的工作。

(3)時間控制:使計算機中各類控制訊號嚴格按照時間上規定的先後順序進行操作。

(4)資料加工:對資料進行算術運算和邏輯運算等操作,或其他資訊的處理。

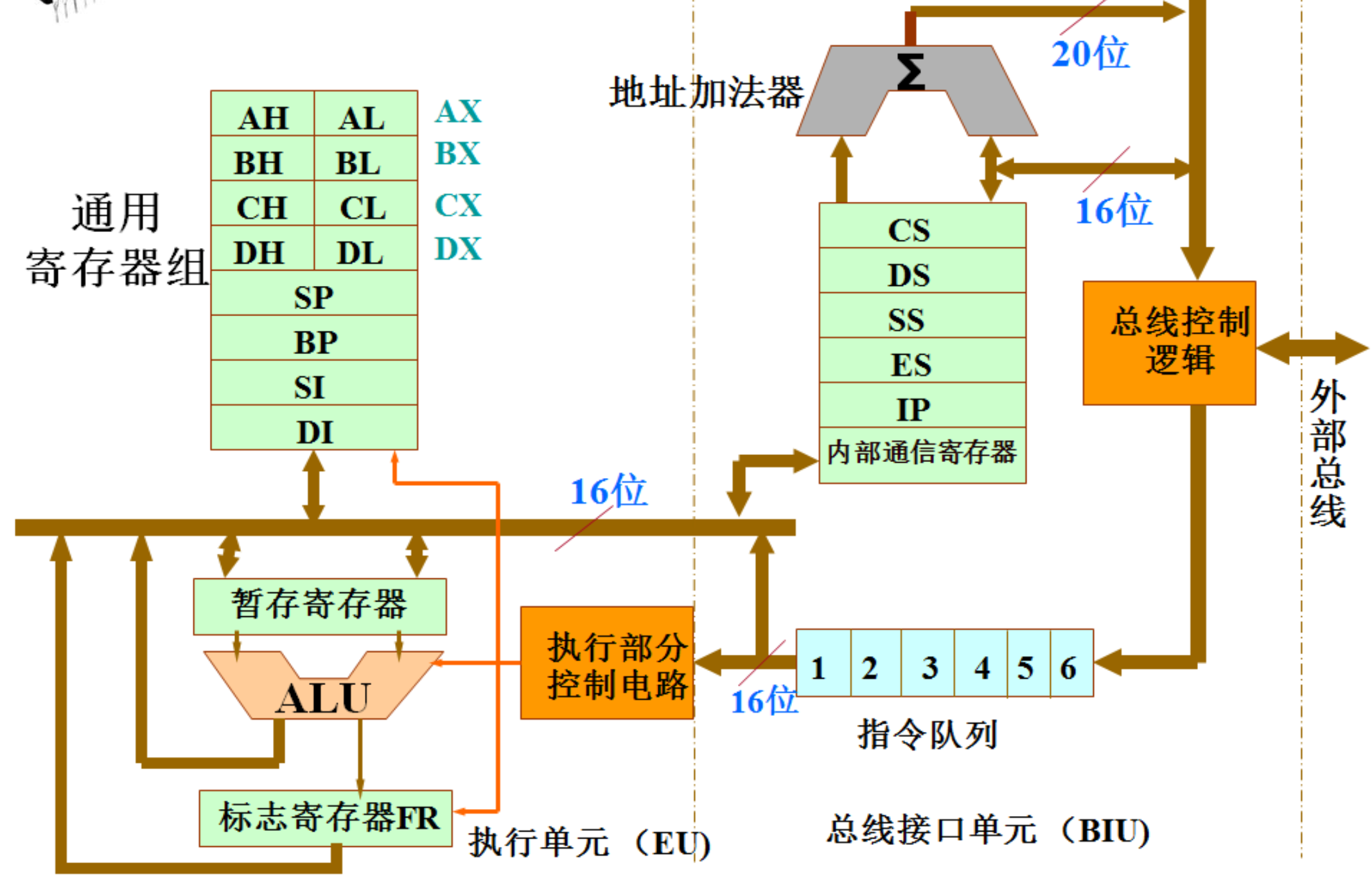

Intel 8086微處理器的內、外部結構

Intel 8086微處理器是一種具有代表性的處理器,後續推出的各種微處理器均保持與之相容。

- 8086微處理器使用+5V電源

- 40條引腳雙列直插式封裝

- 時脈頻率為5MHz~10MHz

- 有16根傳輸線和20根地址線,可定址的記憶體地址空間達1MB(220B)

8086微處理器的特點

- 採用並行流水線工作方式,通過設定指令預取佇列實現

- 對記憶體空間實行分段管理,實現對1MB空間的定址

- 支援多處理器系統;工作於最小模式和最大模式兩種工作模式。

指令執行部件EU

- 算術邏輯運算單元ALU

完成8位元或16位元的二進位制算術運算和邏輯運算;

運算結果送到通用暫存器或標誌暫存器或寫入記憶體。 - FR標誌暫存器

存放ALU運算後的結果特徵或機器執行狀態。 - 資料暫存暫存器

暫時存放參加運算的運算元,不可程式化。 - 通用暫存器組

4個16位元資料暫存器: AX、BX、CX、DX;

4個16位元地址指標與變址暫存器: SP、BP、SI、DI。 - EU控制電路

接收從BIU指令佇列中取來的指令,經過指令譯碼形成各種定時控制訊號,對EU的各個部件實現特定的定時操作。

匯流排介面單元BIU

根據EU的請求,完成CPU與記憶體、I/O介面之間的資訊傳送。

提供從記憶體取指令送指令佇列或直接送EU執行;

從記憶體或外設取資料送EU,或把EU操作結果送記憶體或外設。

- 4個16位元段地址暫存器

CS:程式碼段暫存器; DS:資料段暫存器; SS:堆疊段暫存器; ES:擴充套件(附加)資料段暫存器。 - 16位元指令指標暫存器IP

存放下一條將要執行指令的偏移地址(有效地址EA); - 20位地址加法器

將16位元的邏輯地址變換成訪記憶體的20位實體地址,完成地址加法操作。 - 6位元組指令佇列

預存6個位元組的指令程式碼。 - 匯流排控制電路

發出匯流排控制訊號。 將8086CPU內部匯流排與外部匯流排相連。

8086功能上劃分:執行部件EU;匯流排介面部件BIU

- 當8086指令佇列中有2位元組空閒時,匯流排介面部件就自動將指令從記憶體中預取到指令佇列緩衝器中。

- 當EU部件要執行一條指令時,它就從指令佇列頭部取出指令,後續指令自動向前推進。

- EU在執行指令中若需要存取記憶體或I/O裝置,EU就向BIU申請匯流排週期,若BIU匯流排空閒,則立即響應,若BIU正在取一條指令,則待取指令操作完成後再響應EU的匯流排請求。

- 遇到轉移、呼叫及返回指令時,BIU就自動清除指令佇列中已有內容,從轉移、呼叫或返回的新地址開始,重新從記憶體中預讀取指令並填充指令佇列。

- 這兩部分既非同步工作方式,也不完全無關,而是互相配合工作的。

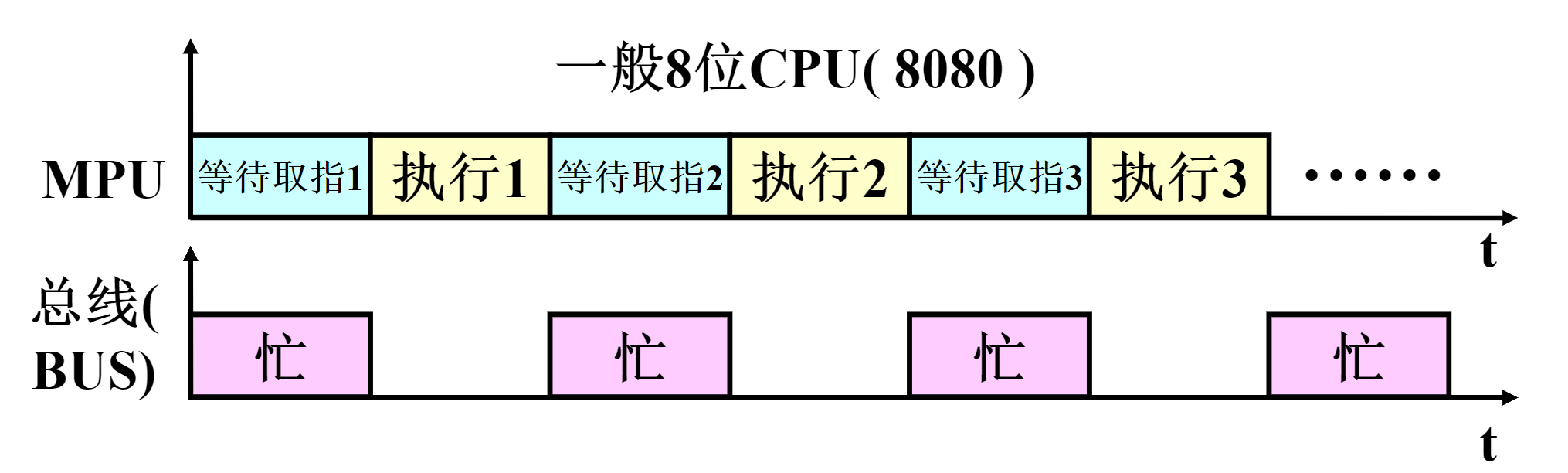

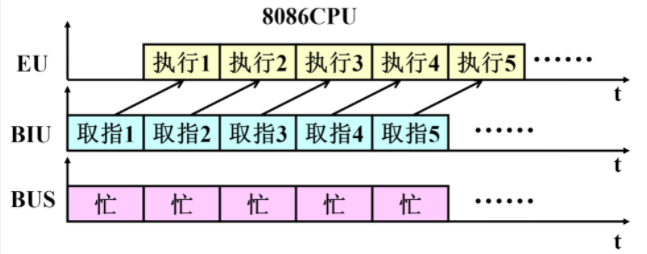

傳統微處理器執行程式時先從記憶體取出一條指令,然後讀出運算元,最後執行指令。取指令和執行指令序列進行,取指令期間,CPU必須等待。

8086中取指令和執行指令分別由BIU和EU來完成,BIU和EU可並行工作。EU負責執行指令,BIU負責取指令、讀出運算元和寫入結果。大多數的情況下,取指令和執行指令可重疊進行。

8086中BIU和EU並行工作方式,減少了CPU為取指令等待的時間,整個程式執行期間, BIU是充分利用了匯流排,極大的提高了CPU的工作效率,成為8086突出優點。

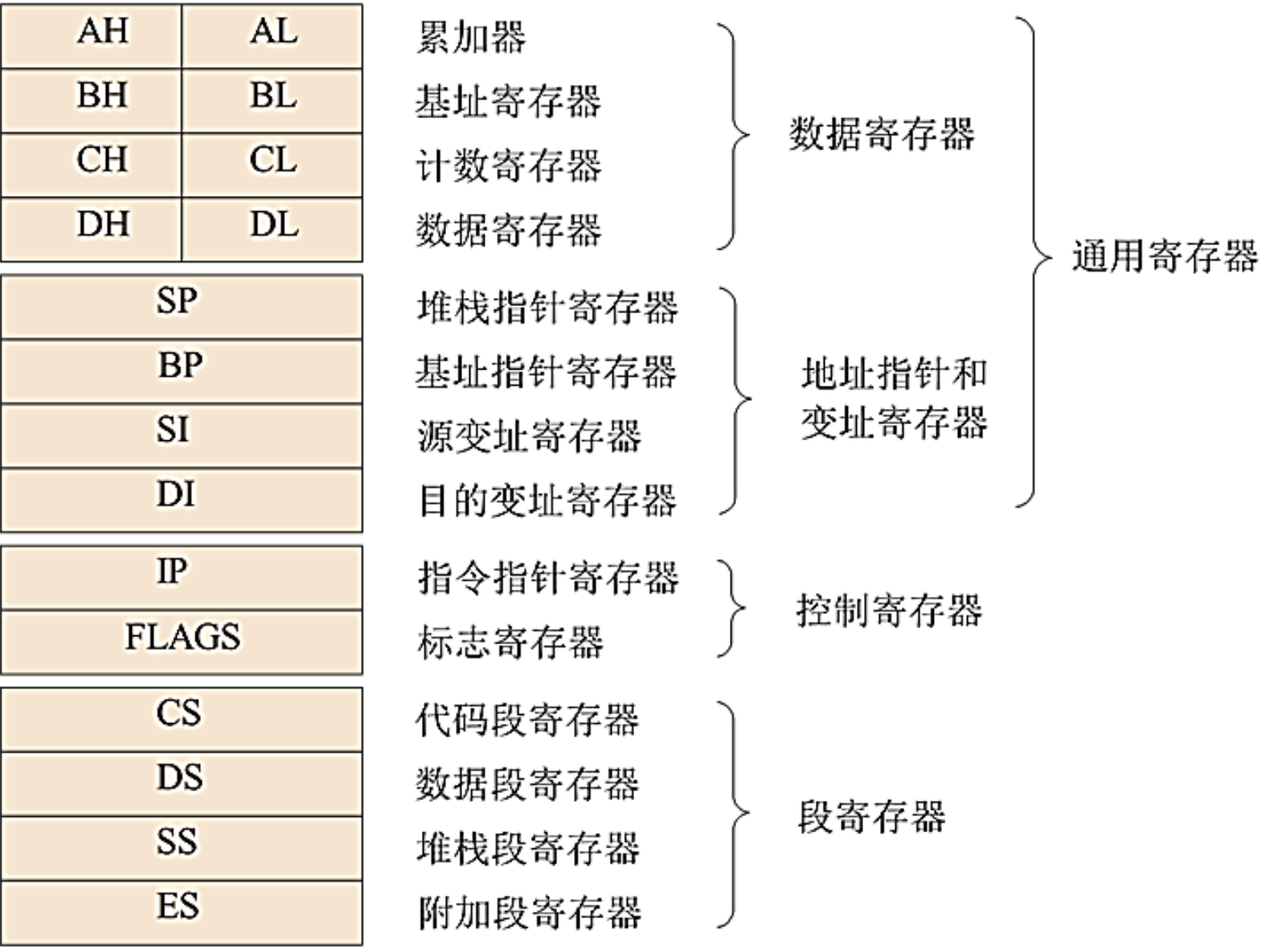

8086微處理器的暫存器結構

8086CPU中可供程式設計使用的有14個16位元暫存器。分為3類: 通用暫存器、控制暫存器、段暫存器。

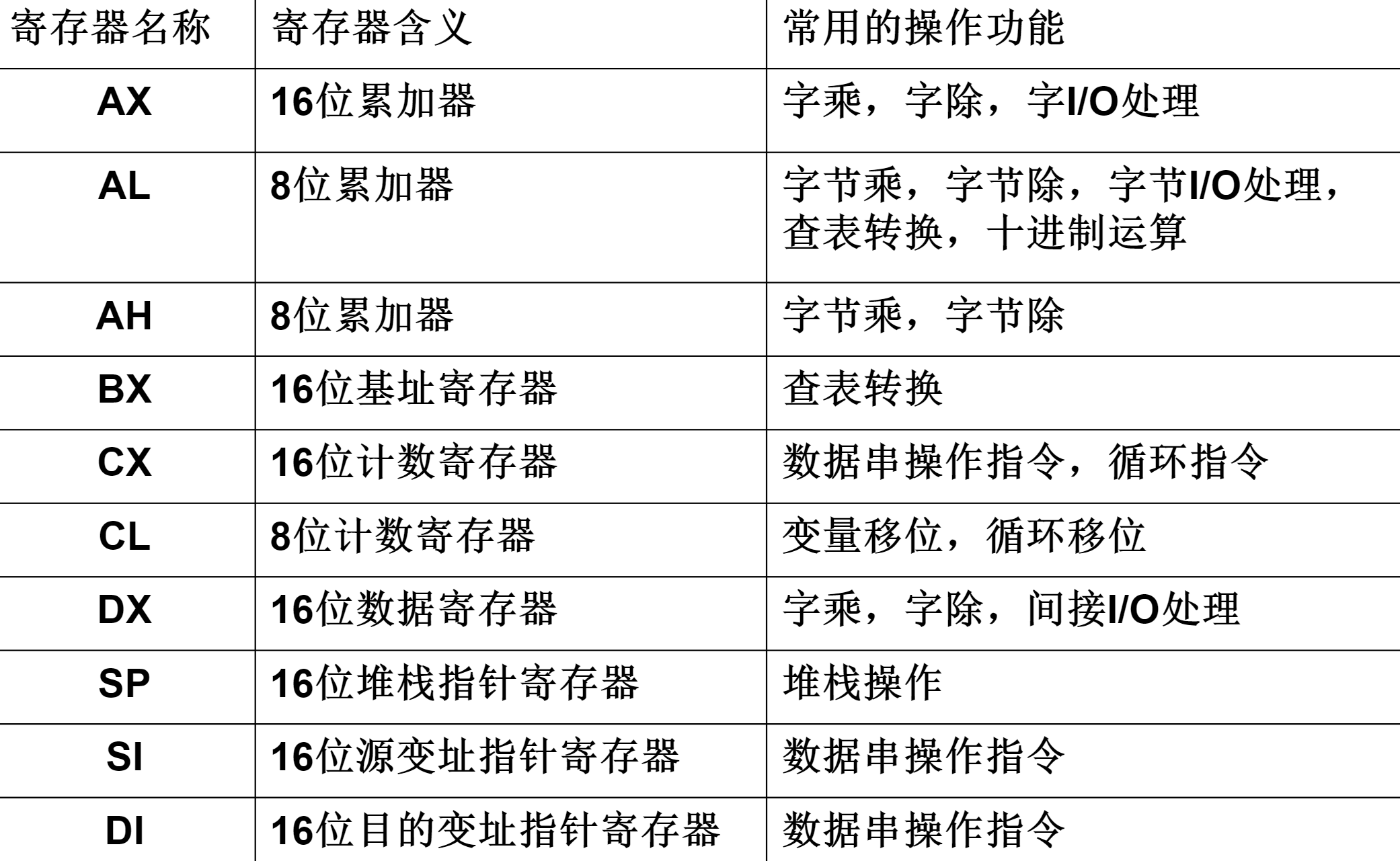

通用暫存器

資料暫存器: 存放運算元或中間結果。

- 16位元暫存器:AX;BX; CX;DX;

- 可分成8位元暫存器使用: AH;AL; BH;BL; CH;CL; DH;DL。

指標和變址暫存器:存放地址偏移量。

- 16位元的指標暫存器SP、BP

SP 堆疊指標暫存器:給出棧頂偏移地址;

BP 基址指標暫存器:存放位於堆疊段中資料區基址的偏移地址。 - 變址暫存器SI、DI :

用於指令變址定址,SI和DI用來存放當前資料段的偏移地址 。

SI:源變址暫存器: DI:目的變址暫存器:

控制暫存器

指令指標暫存器

IP(Instruction Pointer)指令指標暫存器: 存放EU要執行的下一條指令的偏移地址,控制程式中指令的執行順序。

IP 用來存放程式碼段中的偏移地址。 在程式的執行過程中,它始終指向下一條指令的偏移地址,和CS一起形成下一條指令的實體地址(CS:IP)

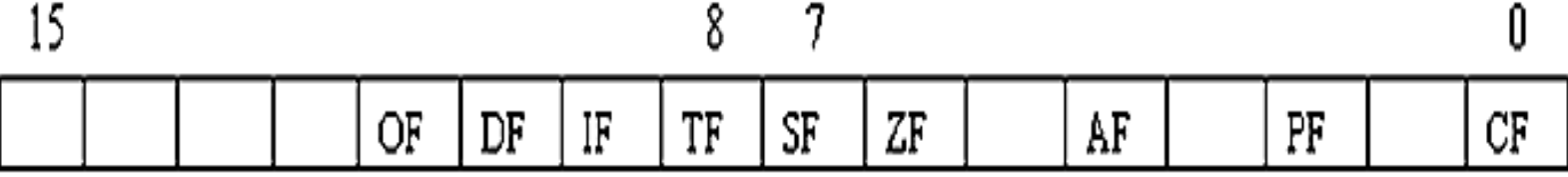

**標誌暫存器 **

8086內部標誌暫存器的內容,又稱為處理器狀態字PSW。 存放ALU運算後的結果特徵或機器執行狀態,只用9位。

條件標誌位(6位): 表示前一步操作(如加、減等)執行後,ALU所處的狀態,後續操作可以根據這些狀態標誌進行判斷,實現轉移;

控制標誌位(3位): 通過指令人為設定,用以對某一種特定的功能起控制作用,反映了人們對微機系統工作方式的可控制性。

狀態標誌位:

- CF—進位標誌位,做加法時最高位出現進位或做減法時最高位出現借位,該位置1。

- PF—奇偶標誌位,當運算結果的低8位元中l的個數為偶數時,則該位置1。

- AF—半進位標誌位,做位元組加法時,當低四位有向高四位的進位,或在做減法時,低四位有向高四位的借位時,該標誌位就置1。通常用於對BCD算術運算結果的調整。

控制標誌位:

- TF—陷阱標誌位(單步標誌位、跟蹤標誌)。當該位置1時,將使8086進入單步工作方式,通常用於程式的偵錯。

- IF—中斷允許標誌位,若該位置1,則處理器可以響應可遮蔽中斷。

- DF—方向標誌位,若該位置1,則串操作指令的地址修改為自動減量方向,反之,為自動增量方向。

段暫存器

8086微處理器最大定址1MB儲存空間。

1)包含在指令中的地址,以及在指標和變址暫存器中的地址只有16位元長;

2)16位元地址定址空間216=64KB,存取不到1MB儲存空間。

3)解決該問題,採用記憶體分段技術來實現。

4)8086CPU把1MB的儲存空間分成若干個邏輯段,邏輯段的長度不超過64KB(216B)。把段地址左移4位元和偏移地址相加形成20位地址,可存取1M空間。

4個16位元的段暫存器,用來存放每一個邏輯段的段起始地址。

1)程式碼段暫存器CS:給出當前的程式碼段起始地址,CPU執行的指令將從程式碼段取得。

2)資料段暫存器DS:指向程式當前使用的資料段,用來存放資料。

3)堆疊段暫存器SS:給出程式當前所使用的堆疊段,堆疊操作的執行地址就在該段。

4)附加段暫存器ES:指出程式當前所使用的附加段,通常也用來存放資料。

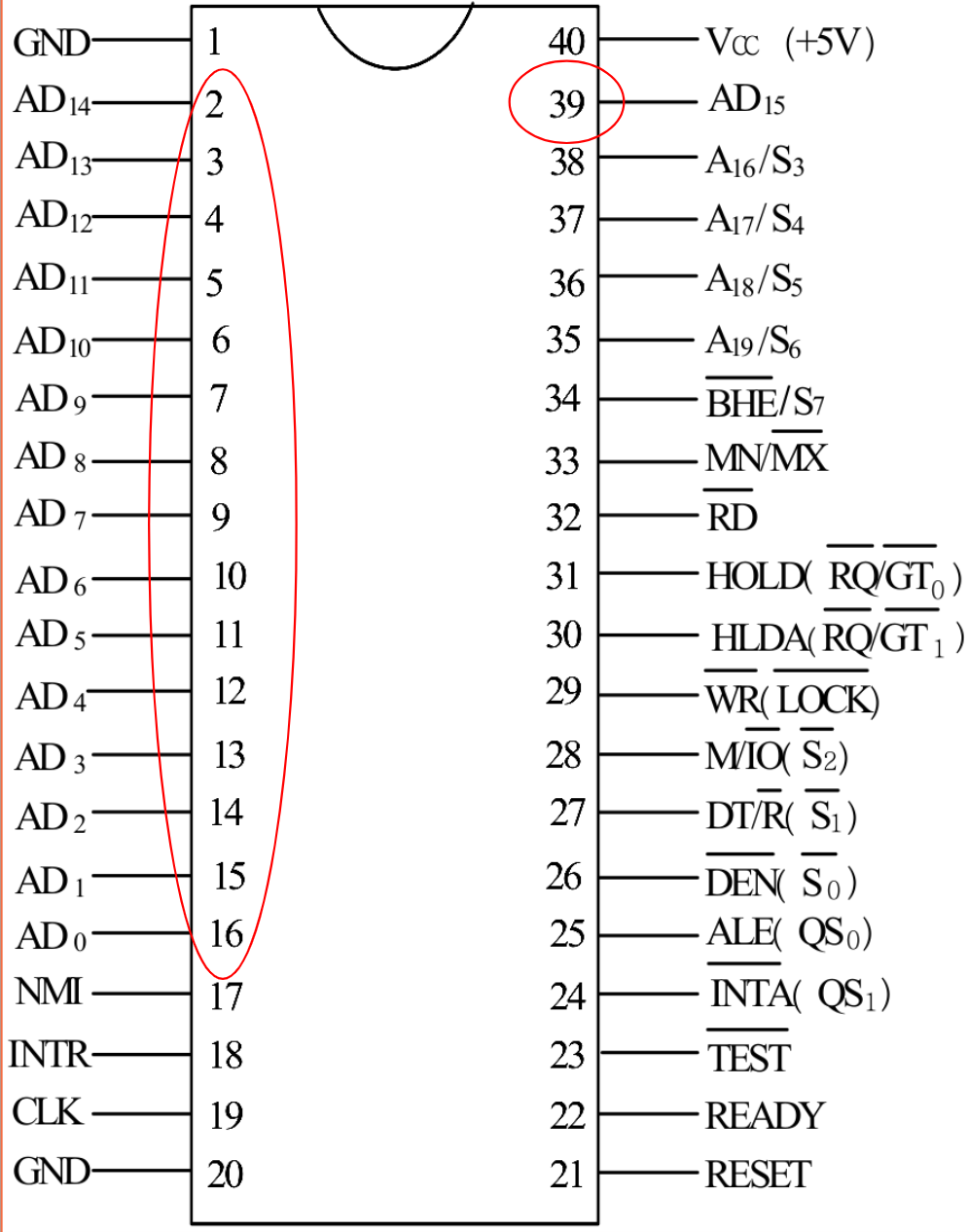

8086微處理器的外部引腳特性

8086CPU具有40個引腳。 可以分成5類訊號:

16位元傳輸線:AD0~AD15

20位地址線:AD0~AD19

可直接定址空間為1M位元組。地址/資料匯流排採用了分時複用方式。 其餘為狀態線、控制訊號線、電源、地線等。

地址/資料匯流排16條:

- AD15-AD0(2—16,三態):地址/資料複用訊號,輸入/輸出引腳,低16位元地址訊號及資料訊號的輸入/輸出。

- 地址/資料匯流排採用分時複用方式。

- 匯流排分時複用:同一匯流排在不同時間傳輸的是不同的訊號。8086採用匯流排分時複用方法在不影響CPU功能的情況下,減少了CPU的引腳數目,使系統得到簡化。

地址/狀態線4條:

- A19/S6A16/S3(3538,三態):地址/狀態訊號,輸出引腳。

- 在記憶體操作匯流排週期的第一個時鐘週期,輸出20位地址高4位元A19A16,與AD15AD0組成20位地址訊號。

- 其他時鐘週期輸出狀態訊號S6~S3。其中S6為0,指示8086CPU當前與匯流排連通; S5為1表明8086CPU可以響應可遮蔽中斷;

- S4、S3共有四個組合狀態,指明當前使用的段暫存器,00-ES,01-SS,10-CS,11-DS。

控制匯流排9條:

- BHE/ S7 (34,三態):高8位元資料允許/狀態複用訊號,輸出。

- 在匯流排週期的第一個時鐘週期輸出匯流排高位元組允許訊號BHE,表示高8位元傳輸線D15—D8上的資料有效。

- 其餘時鐘週期輸出狀態S7 。

- BHE和地址線A0配合用來產生儲存體的選擇訊號。

RD(32,三態):

- 讀控制輸出訊號,低電平有效,用以指明要執行一個對記憶體單元或I/O埠的讀操作,具體是讀記憶體單元還是I/O埠,取決於控制訊號M/IO。

- CPU部分引腳的三態性

- 所謂三態是指匯流排輸出可以有三個狀態:高電平、低電平和高阻狀態。當處於高阻狀態時,該匯流排在邏輯上與所有連線負載電氣斷開。

READY(22):「準備好」狀態訊號輸入,高電平有效。「Ready」 引腳接收來自記憶體或I/O向CPU發來的「準備好」狀態訊號。表明記憶體或I/O已經準備好進行讀寫操作。協調CPU與記憶體或I/O之間進行資訊傳送的聯絡訊號。

TEST(23):測試訊號輸入,低電平有效。TEST訊號與WAIT指令結合起來使用,CPU執行WAIT指令後,處於等待狀態,當TEST引腳輸入低電平時,系統脫離等待狀態,繼續執行被暫停執行的指令。

INTR(18):可遮蔽中斷請求訊號輸入引腳,引入中斷源向CPU提出的中斷請求訊號,高電平有效。

NMI(17) 非遮蔽中斷請求訊號輸入引腳,高電平有效。該訊號不受中斷允許標誌IF狀態的影響,NMI比INTR的優先順序別高。

RESET(21):復位訊號輸入,高電平有效。復位訊號輸入之後,CPU結束當前操作,並對處理器的標誌暫存器、IP、DS、SS、ES暫存器及指令佇列進行清零操作,而將CS設定為0FFFFH。

CLK/(19):時鐘訊號輸入,8086CPU的時脈頻率為5MHz,即從該引腳輸入的時鐘訊號的頻率為5MHz。

MN/MX(33):最小/最大模式設定訊號輸入引腳。

- 該輸入引腳電平的高、低決定了CPU工作在最小模式還是最大模式。

- 當該引腳接+5V時,CPU工作於最小模式下,當該引腳接地時,CPU工作於最大模式下。

電源線和地線3條: VCC(40)、GND(1、20):電源、接地引腳,8086CPU採用單一的+5V電源,有兩個接地引腳。

總結

8086微處理器從功能結構上可以劃分為執行部件和匯流排介面部件兩大部分。8086並行工作方式,減少了CPU等待取指令的時間,充分利用了匯流排,有力地提高了CPU的工作效率,成為8086的突出優點。

8086微處理器的暫存器使用非常靈活,可供程式設計使用的有14個16位元暫存器。按其用途可分為3類:通用暫存器、段暫存器、指標和標誌暫存器。

8086微處理器有40條引腳,按作用可分為5類:

- 地址/資料匯流排16條;

- 地址/狀態線4條;

- 控制匯流排9條;

- 電源線和地線3條;

- 其他控制線8條。