Xilinx PLL IP核功能模擬

2020-10-25 17:00:31

0 本章目錄

1)軟體環境

2)PLL IP核模擬流程

3)結束語

1 軟體環境

1)vivado 2016.1

2)modelsim10.4c

2 PLL IP核模擬流程

PLL IP核模擬流程如下:

1)vivado 關聯modelsim模擬軟體;

2)PLL IP核設定;IP設定,輸入時鐘clk_in1為100MHz,輸出時鐘clk_out1為50MHz, clk_out1為100MHz。

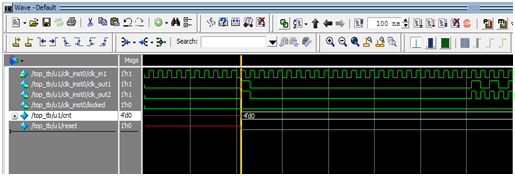

3)模擬剛開始時,兩個輸出時鐘會產生一個時鐘週期的電平如圖1所示。

圖1 模擬毛刺

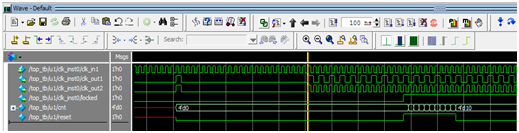

4)接著模擬,產生輸出時鐘且locked訊號為低,代表這時產生的輸出時鐘不穩定還不能用它去驅動其他邏輯如圖2所示。

圖2 模擬截圖

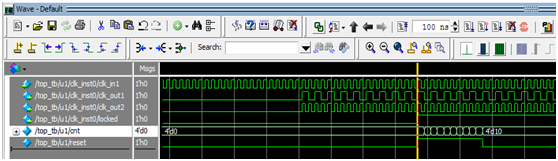

5)只有當locked訊號為高時,輸出時鐘才會穩定,可以用它去驅動其他邏輯如圖3所示。

圖3 模擬截圖