VARON設計流程及範例

本文介紹有關使用VARON的設計流程和基礎範例的介紹。

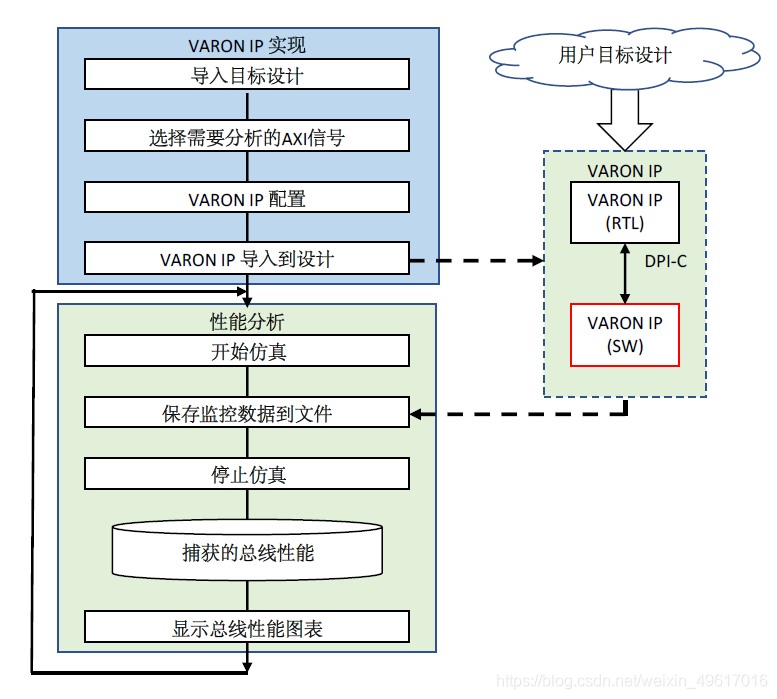

設計流程

圖1顯示了VARON的設計流程。 第一步,將VARON IP匯入使用者的目標設計。 VARON IP用RTL(Verilog HDL)編寫。 這允許使用者將VARON IP匯入到Verilog HDL或VHDL編寫的使用者設計和環境中。第二步是選擇要觀察的AXI訊號,然後完成VARON IP設定並注入使用者設計。

VARON IP實施完成後,執行模擬,將選擇的訊號資料提取到檔案中並進行模擬。

最後,啟動VARON監控器並載入匯流排效能資料,然後使用各種效能分析工具開始效能分析。

VARON IP設定

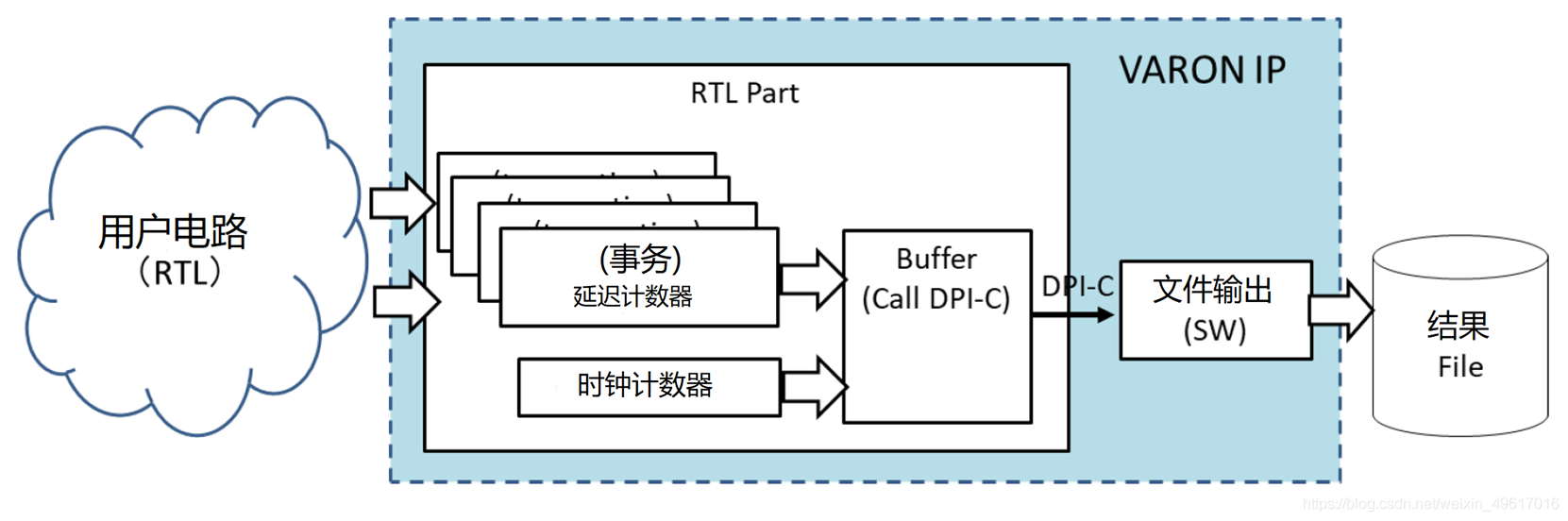

圖2顯示了VARON IP。 VARON IP由時鐘計數器,讀取側/寫入側的延遲計數器和RTL編寫的緩衝區組成,以及由C語言編寫的檔案輸出軟體組成。

1. 時鐘計數器

- ACLK的計數(由ARESETn初始化)

- 單位時間的測量:週期間隔(單位時間)可以從模擬引數中設定。

2. 延遲計數器(事務)

- 一個延遲計數器可以捕獲1個AXI匯流排埠。

- 捕獲交易時間和突發長度。

3. 緩衝區(DPI-C)

- 收集時鐘計數器和每個埠的事務處理資訊,並通過DPI-C將其傳遞到檔案輸出軟體以輸出檔案。

時鐘計數器

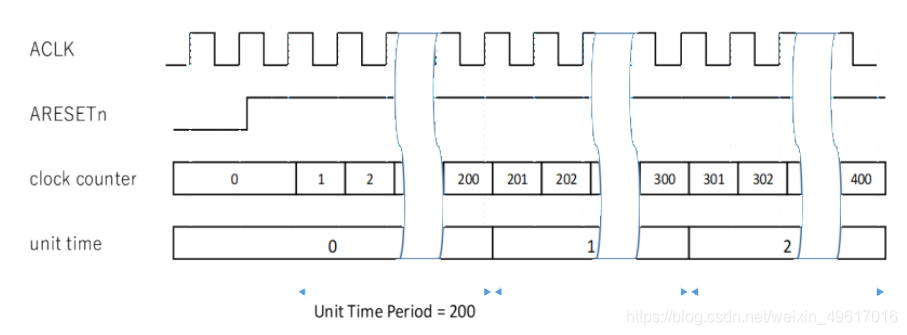

時鐘計數器對ACLK的數量進行計數,並將時間戳新增到VARON IP輸出的輸出資料中(由ARESETn初始化)。 收集每個計數器的捕獲資料並將其一次儲存到緩衝區中,以減少軟體(DPI-C)對硬體模擬器效能的呼叫。 在捕獲AXI事件和寫入時間到檔案裡之間存在延遲。 每個捕獲資料都包含時間戳資訊,以補償將捕獲儲存到緩衝區時的延遲。

有兩種方法可以對單位時間的間隔時間進行程式設計,一種是從模擬引數開始,另一種是VARON RTL輸入訊號。

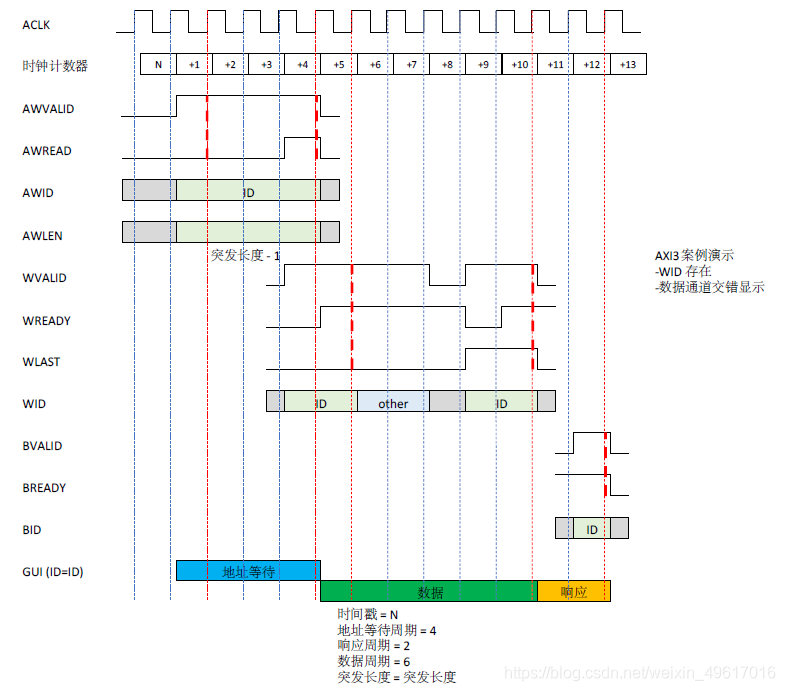

時鐘計數器時序如圖3所示。

單位時間計數器通過引數設定週期來輸出時間,或者從使用者電路輸入表示單位時間週期的訊號。

延遲計數器

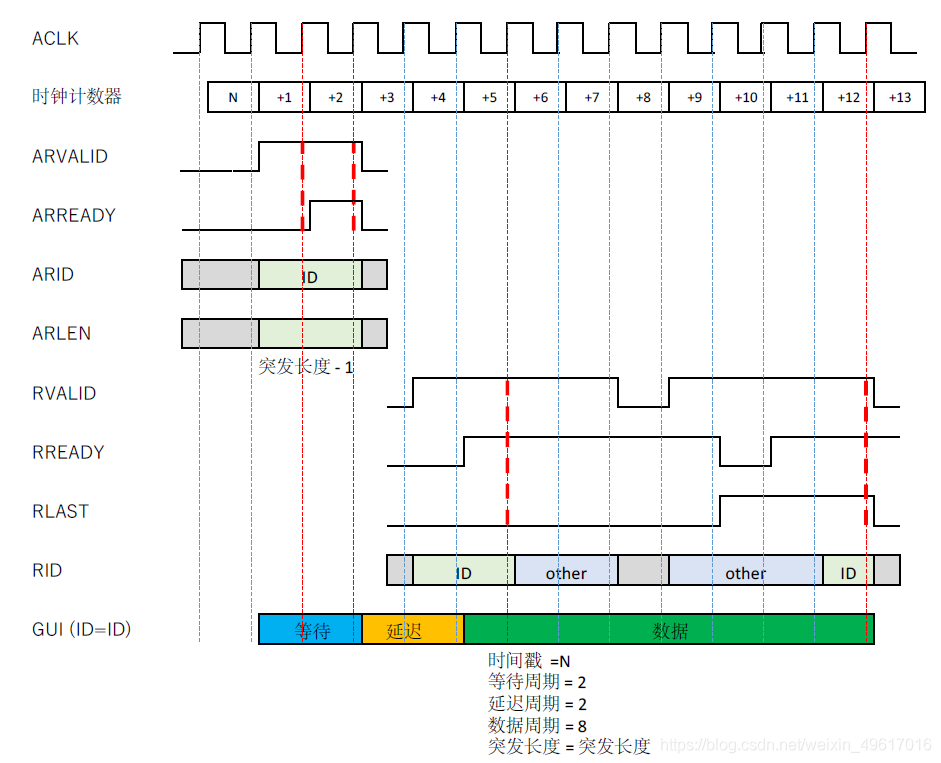

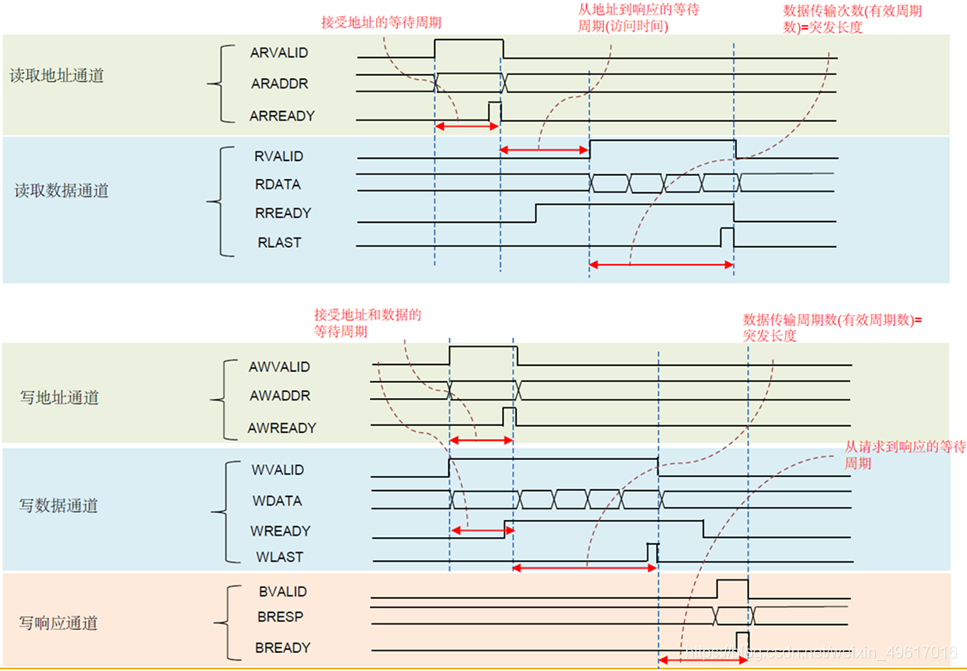

圖4顯示了延遲計數器的讀取通道時間以及與GUI圖表的關係。

圖5顯示了延遲計數器的寫入通道時間以及與GUI圖表的關係。

AXI匯流排時序觀察

圖6顯示了在AXI匯流排標準上讀取/寫入事務的捕獲時序。

例如,VARON測出讀取事務需要3個等待週期。

- 地址等待週期是從ARVALID宣告到ARREADY宣告,它表示從主機到主機傳送地址到從機的延遲。

- 存取時間是指從接受地址到開始資料傳輸的時間。

- 資料週期是從接收到的第一個突發資料到最後一個接收的突發資料的週期,取決於RVALID和RREADY握手,它可能與真實的傳輸突發長度不同。

範例設計

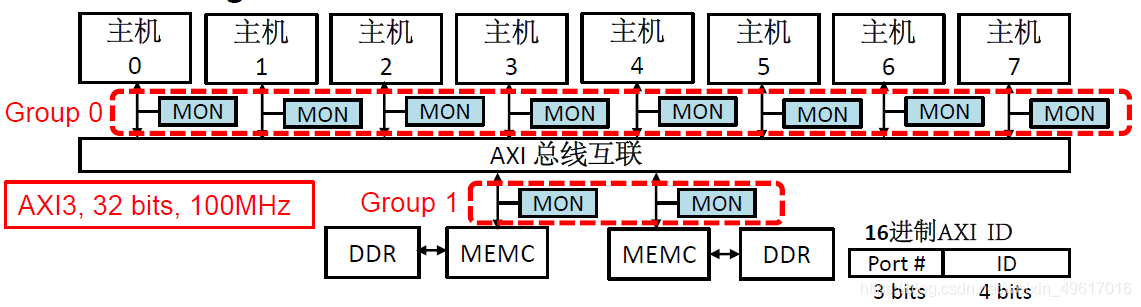

圖7顯示了一個簡單的範例設計。 該範例設計包含8個讀/寫主通道,這些通道由主控器和2個從屬埠連線到MEMC AXI匯流排互連,通過主控器的AXI ID和接收到的埠號產生從屬(連線到MEMC)埠AXI ID。

在典型的效能分析中,使用者希望捕獲來自MEMC埠的資料傳輸量和突發長度,以及來自主埠的等待週期,等待時間週期和資料傳輸量。 此範例將連線主機和互連的AXI匯流排記錄為「主側」,將連線互連和MEMC的AXI匯流排記錄為「從側」。

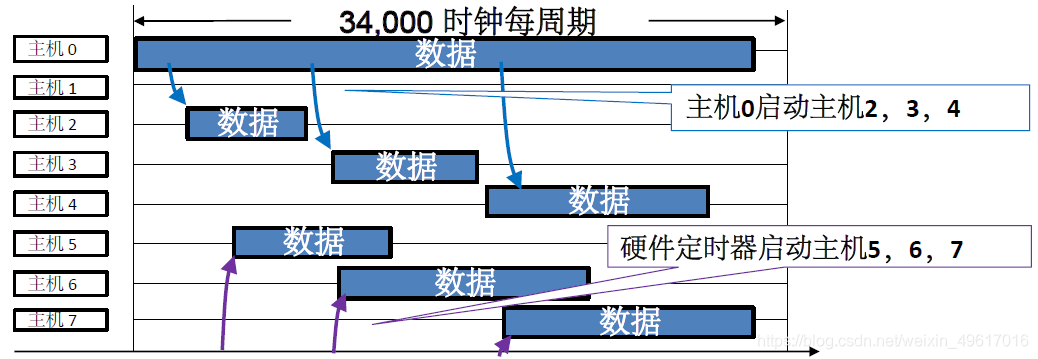

圖8是執行此範例設計的34,000個週期時模擬結果的主機存取影象檢視。 對於兩個MEMC埠,VARON每200個時鐘週期(單位時間)捕獲一次資料傳輸量。

VARON IP 的生成和連線

此步驟將建立組態檔以生成VARON IP,並定義要探測的訊號列表,然後生成VARON IP。 Verilog RTL編寫的VARON IP允許使用者使用使用者電路進行模擬。 最後,執行模擬並通過VARON Monitor執行效能分析。

有關VARON IP的生成和連線,後續會有文章詳細介紹。

分析結果

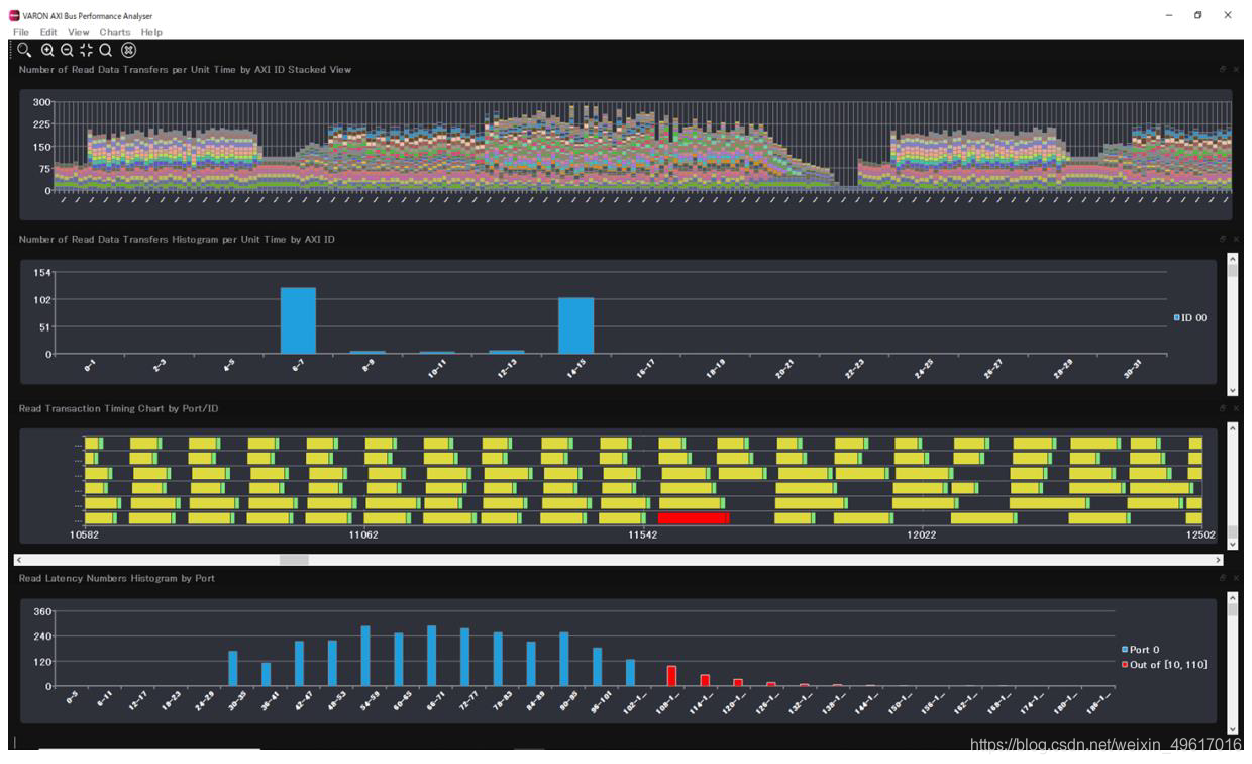

範例設計中的VARON監控器分析圖範例如圖9所示。VARON 模擬版本,允許使用者通過一次模擬獲得所有分析圖。該模擬執行80,000個時鐘週期,單位時間(用於測量資料量的間隔時間)為200個時鐘週期。

以下是圖9中分析結果圖表的列表。

- 每個AXI ID和單位時間的從站側讀取資料傳輸量

- 每個AXI ID和單位時間的從站側讀取資料傳輸量分佈

- 每個埠/ ID的主站側讀取事務時序圖

- 每個埠的主端讀取延遲分佈

VARON監視器允許使用者對分析圖進行以下操作。

- 垂直度/水平捲動(通過卷軸和遊標鍵。)

- 放大,縮小和縮放適合(通過按鈕和按鍵+,-,f。)

- 工具提示:將滑鼠移至捕獲並顯示值。

- 指定顯示的時鐘週期數(時間序列圖)

- 搜尋意外值(按鈕和按鍵:Ctrl-F)

- 開啟對話方塊->設定範圍(最小和最大值)->以紅色突出顯示超出範圍的捕獲

以下是查詢具有較大延遲值的事務的範例。

1. VARON通過「按埠讀取延遲數位直方圖」圖表幫助使用者查詢延遲值超出目標範圍的事務。

①單擊「按埠讀取延遲號直方圖」圖。

②單擊「查詢超出範圍的值」按鈕。

③為Port0設定等待時間0的最小值和等待時間100的最大值,然後單擊確定。

④超出範圍的事務將突出顯示為紅色。

2.此範例通過「按埠/ ID讀取事務時序圖」圖表查詢延遲值超出目標範圍的事務。

①點選「按埠/ ID讀取交易時序圖」圖。

②單擊「查詢超出範圍的值」按鈕。

③為Port0設定等待時間0的最小值和等待時間100的最大值,然後單擊「確定」。

④超出範圍的事務將突出顯示為紅色。

⑤單擊工具列的向右箭頭按鈕,然後搜尋下一個錯誤。