Quartus Prime基本使用方法及模擬遇到的錯誤

Quartus Prime基本使用方法

前言

Quartus常用的幾種設計方法,電路圖、直接使用語言或者兩者結合的方法,本文簡要介紹三種方法及可能出現的問題以及兩種模擬方式。

1. 電路圖

這種方式適合門級電路,搭建簡易的電路模組。

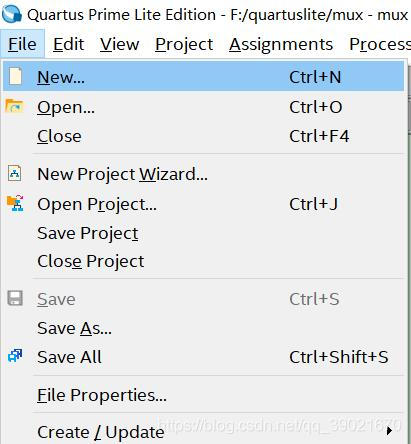

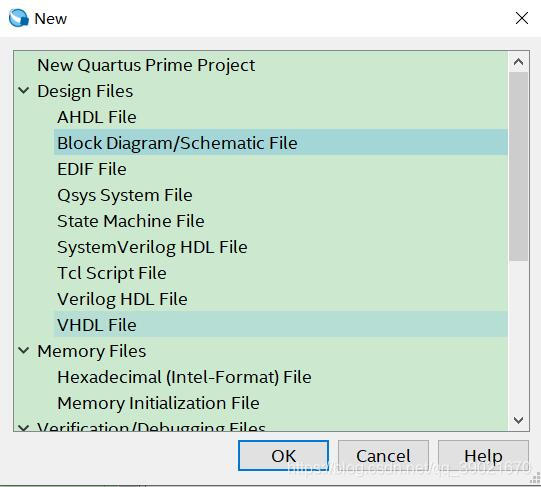

- 首先新建Block Diagram/Schematic File

2. 開啟新建立的.bdf檔案。雙擊空白處課新增所需門單元以及更大的電路單元。

2. 開啟新建立的.bdf檔案。雙擊空白處課新增所需門單元以及更大的電路單元。

3. 電路搭建成功後,編譯即可。

3. 電路搭建成功後,編譯即可。

2.VHDL/Verilog HDL語言

- 同上,新建VHDL/Verilog HDL檔案

- 寫相關程式碼,編譯即可

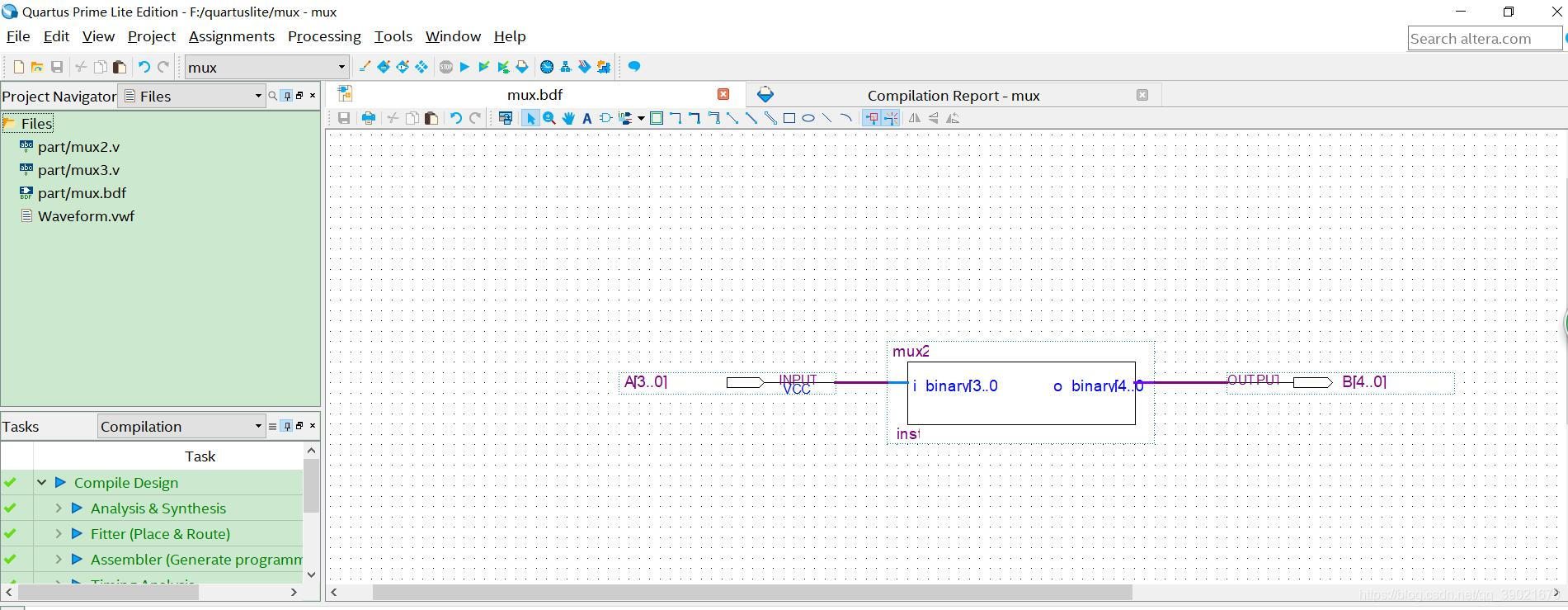

3.自底向上(語言+原理圖)

- 注意:頂層實體名需要與bdf的命名相同

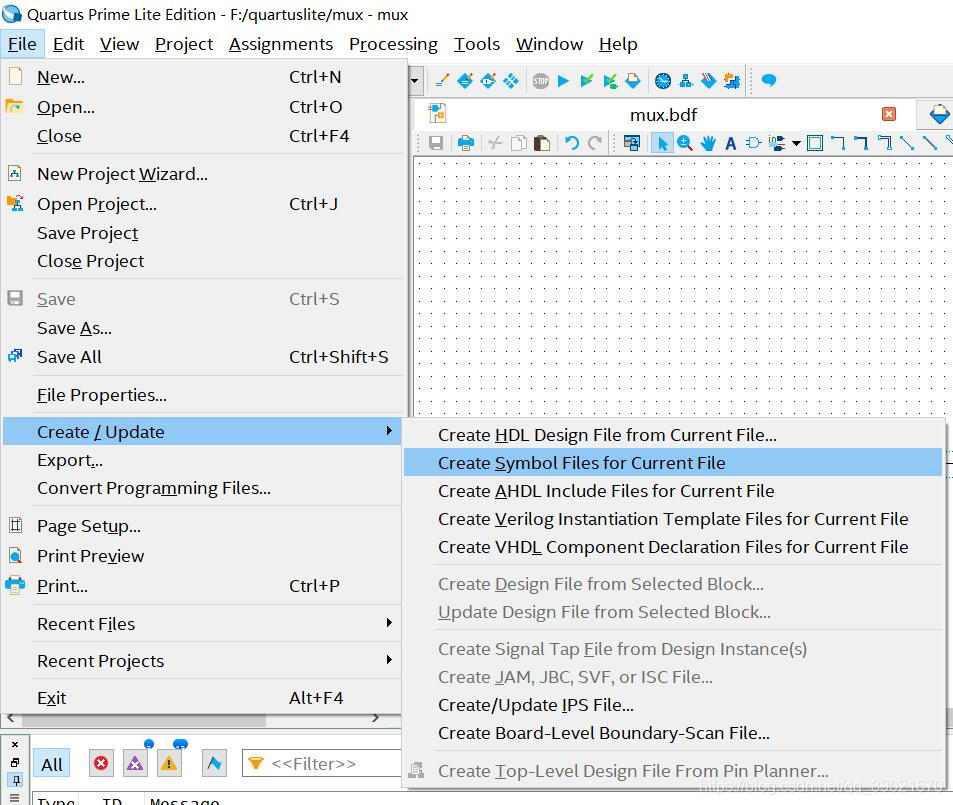

- 用VHDL/Verilog HDL語言編寫不同的電路單元,生成符號檔案。

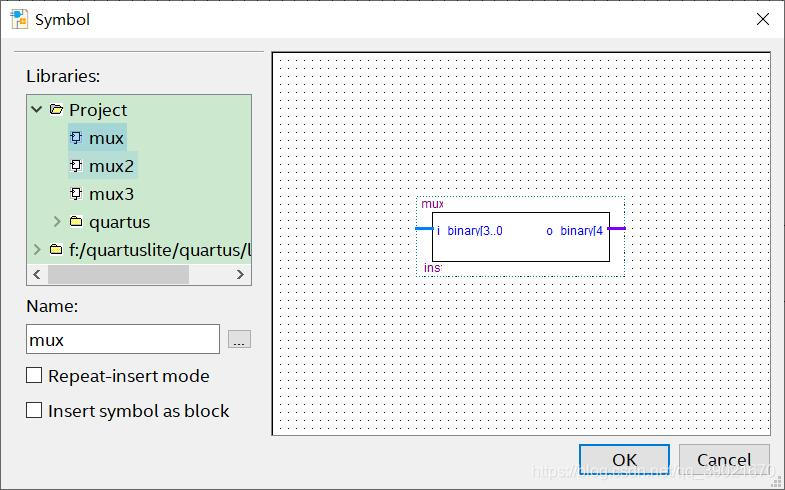

- 新建bdf檔案,雙擊,在project中可以發現剛剛建立的電路單元。

4. 將電路單元連線後即可編譯。

4. 將電路單元連線後即可編譯。

4.兩種模擬方式

- 直接用Quartus中的模擬

-

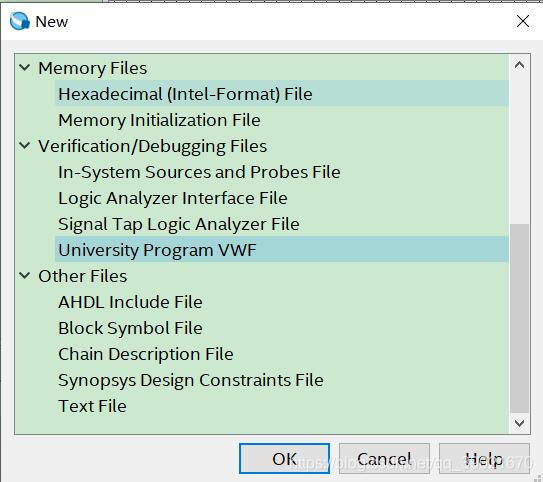

建立University Program VWF檔案

-

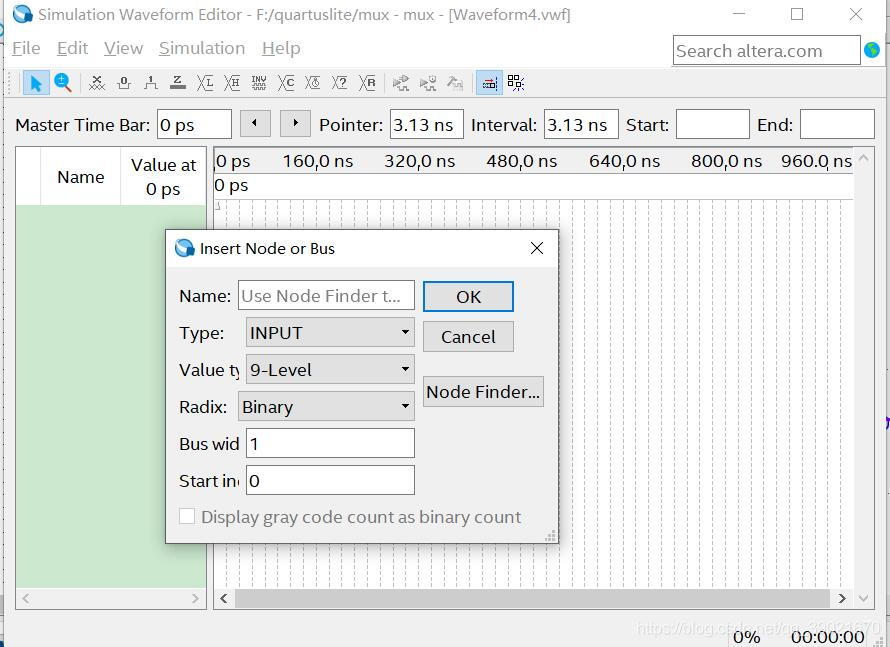

開啟建立的波形檔案,在空白處雙擊,新增所需觀察的節點

-

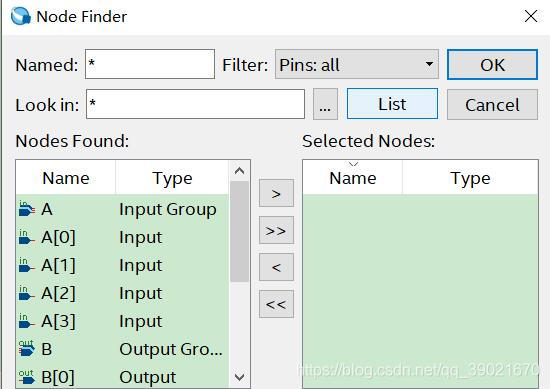

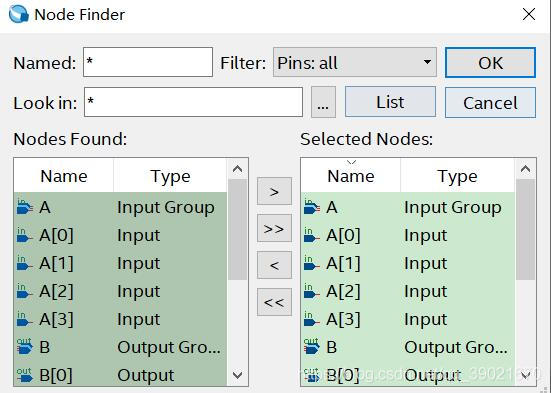

點選node Finder,通過list可以顯示電路節點

-

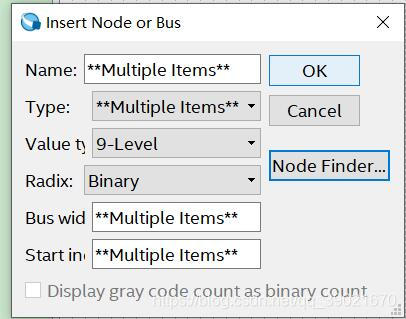

將尋找到的節點移入選擇的節點中,點選OK確認

-

點選OK確認

-

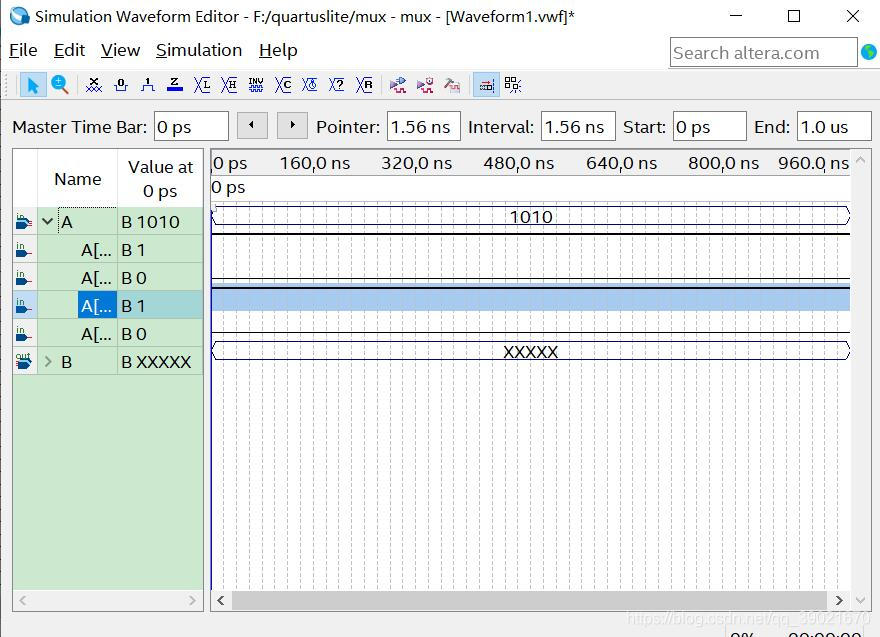

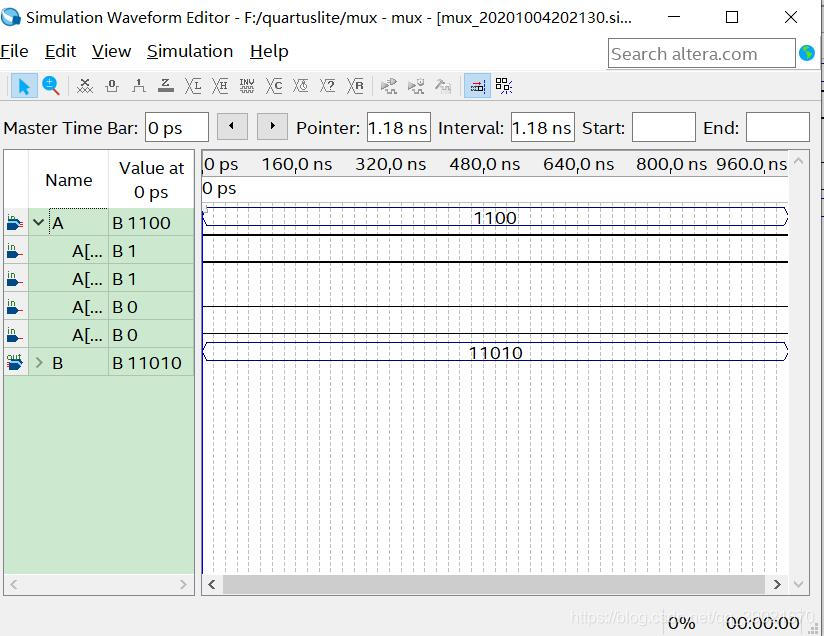

顯示波形檔案

-

通過選單欄快捷按鈕,可置0,置1,設定時鐘,選擇功能模擬或者時序模擬,出現模擬波形。

-

可能出現的錯誤

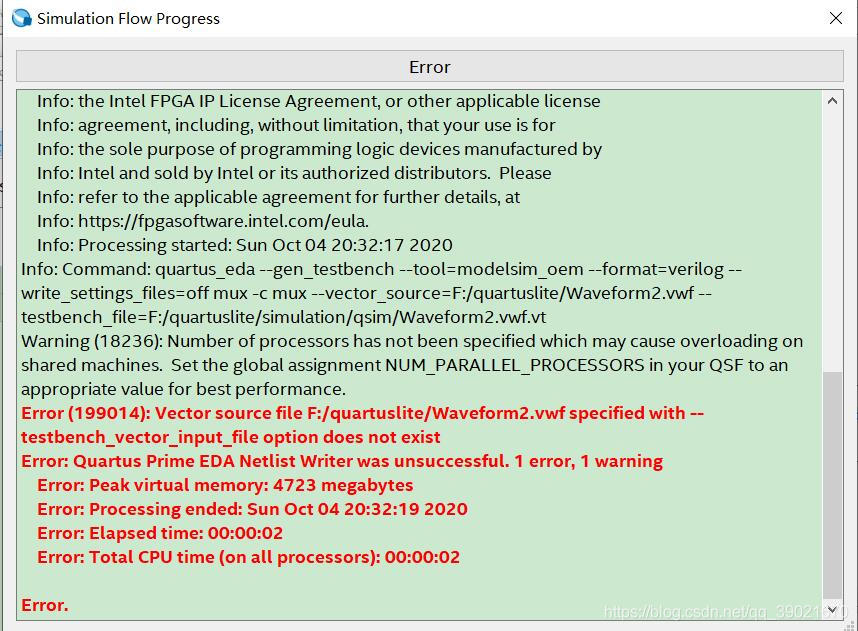

1 檔案路徑錯誤Error (199014): Vector source file F:/quartuslite/Waveform2.vwf specified with --testbench_vector_input_file option does not exist

Error: Quartus Prime EDA Netlist Writer was unsuccessful. 1 error, 1 warning

Error: Peak virtual memory: 4723 megabytes

Error: Processing ended: Sun Oct 04 20:32:19 2020

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:02

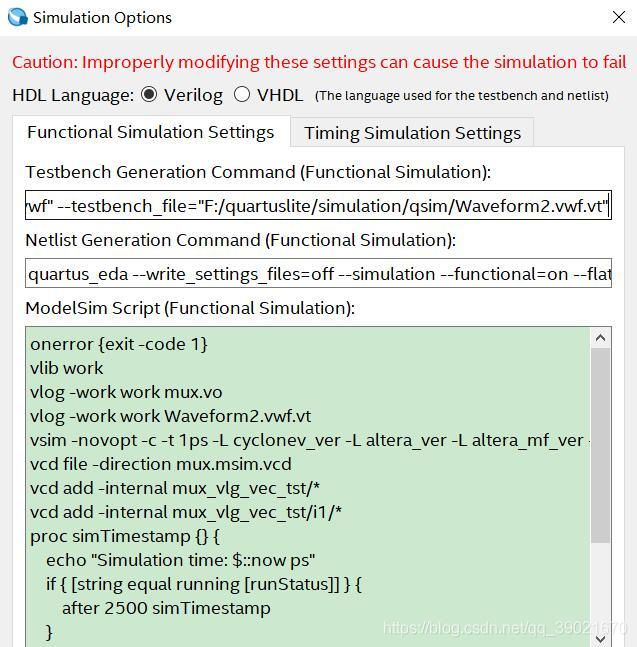

解決方法:儲存vmf檔案時,儲存在預設路徑即可。或者在vmf檔案裡Simulation的設定中修改testbench檔案的路徑

解決方法:儲存vmf檔案時,儲存在預設路徑即可。或者在vmf檔案裡Simulation的設定中修改testbench檔案的路徑

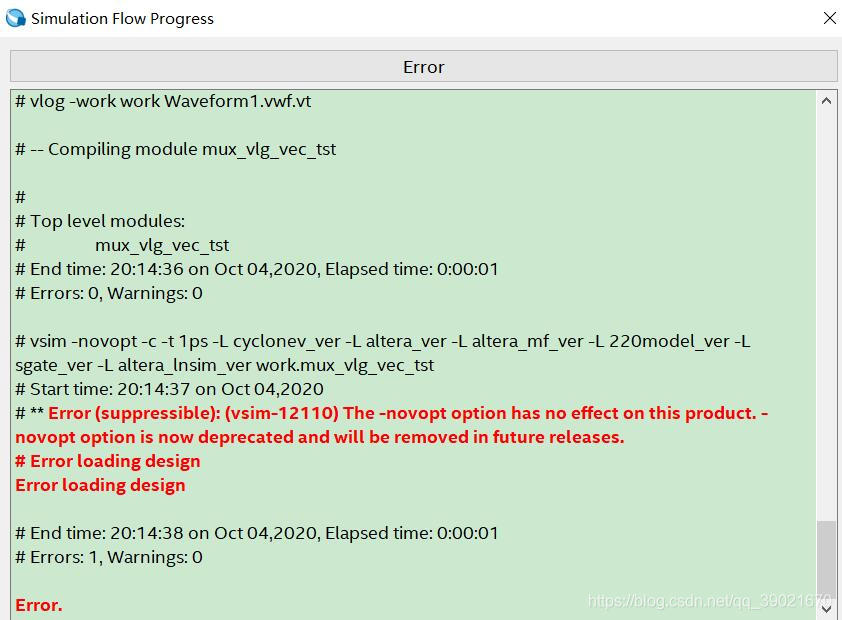

2# ** Error (suppressible): (vsim-12110) The -novopt option has no effect on this product. -novopt option is now deprecated and will be removed in future releases.

Error loading design

解決方法:將vsim 後-novop刪除

- 利用modelsim模擬

-

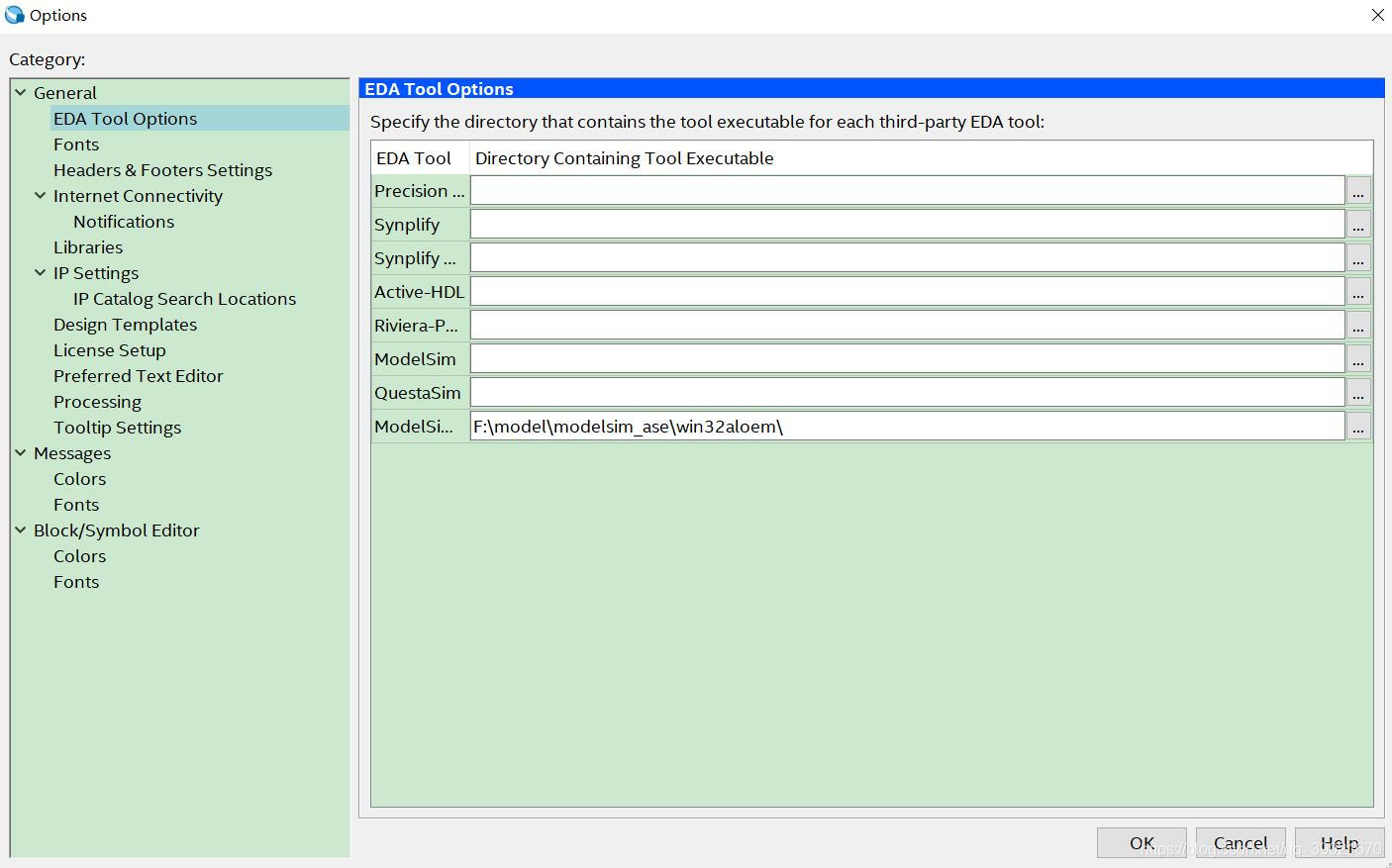

新增modelsim路徑,點選tools->options,選擇modelsim路徑,一定要選擇自己的是modelsim還是modelsim altera,在這個路徑中,記得最後的「\」,在路徑中能發現modelsim。否則會報錯「 Can’t launch the ModelSim-Altera software"下面圖片中採用的是modelsim altera。

-

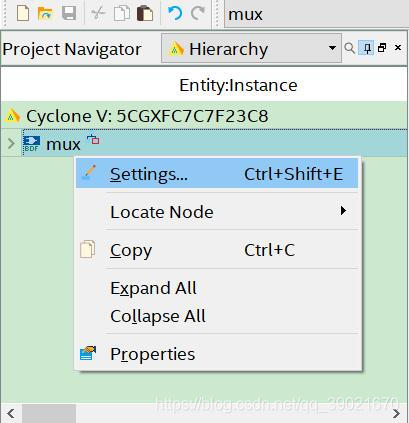

設定專案,右鍵settings

-

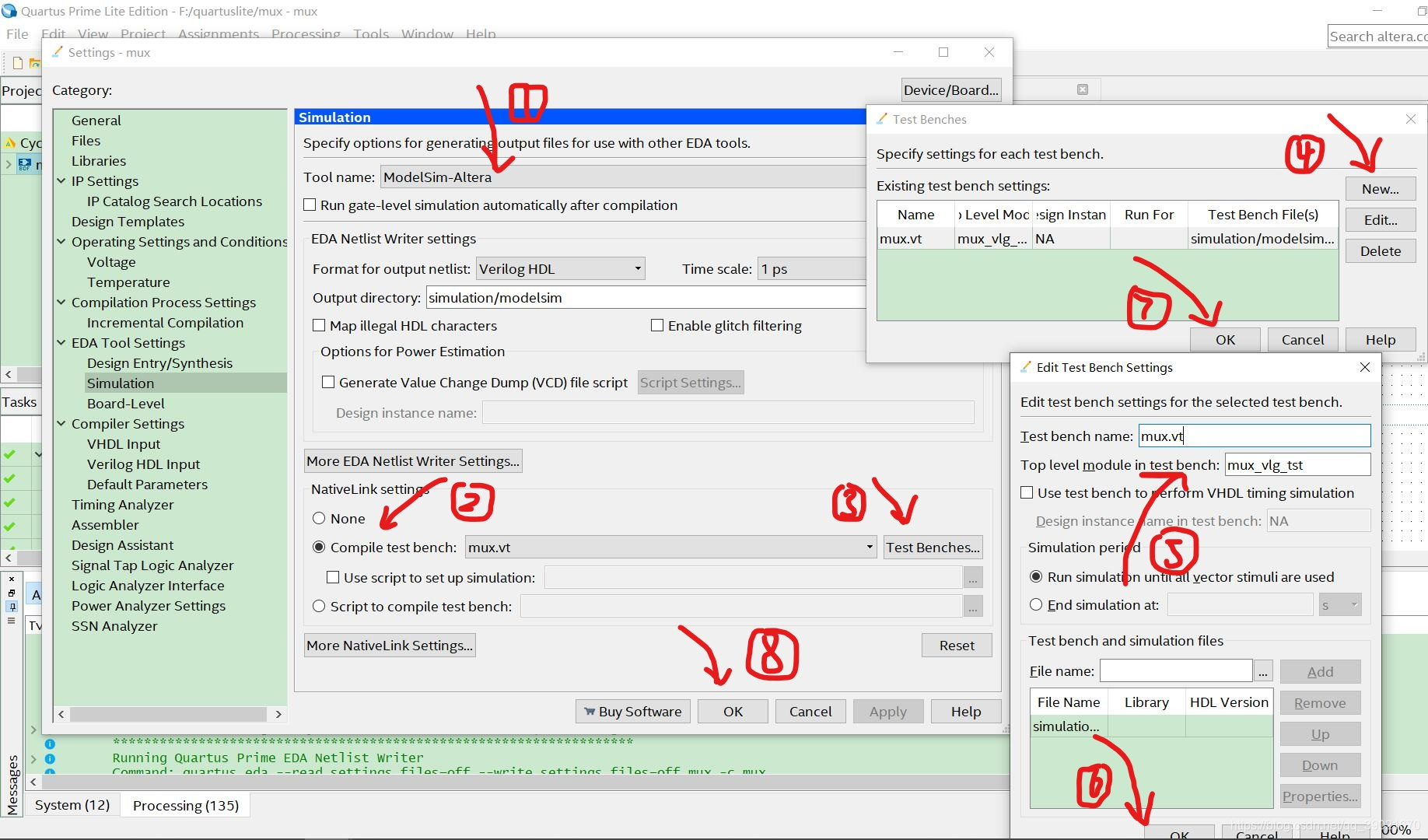

新增testbench檔案,注意第五步中的Test bench name是testbench檔名,Top level module in test bench中是testbench檔案中的模組名

-

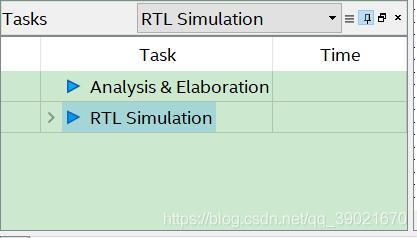

開始RTL Simulation就行