基於DE2的LCD圖形顯示設計

DE2是Altera公司針對大學教學及研究機構推出的FPGA多媒體開發平臺。DE2開發平臺選用的FPGA是CycloneII系列FPGA中的EP2C35F672C6,通過對DE2的學習,我們能夠迅速理解和掌握實時多媒體工業產品設計的技巧,並進行系統設計的驗證。DE2平臺的設計和製造完全按照工業產品標準進行,可靠性很高。本文利用處理器FPGA與液晶顯示模組的圖形顯示的程式設計技術,並以點陣為320×RGB×240的TFT LCD模組D036THEA1為例,研究了FPGA與液晶顯示模組的圖形顯示技術。其關鍵是對驅動晶片D036THEA1的各引腳和時序進行控制。在電路控制部分中,使用QUARTUS II 6.0開發工具來完成軟體設計、模擬。所有功能全部用硬體描述語言Verilog HDL程式設計實現,並下載到DE2實驗開發板上CycloneII系列EP2C35F672C6目標晶片上,使用40腳扁平電纜直接把DE2和TFT LCD模組D036THEA1連線起來.執行驗證滿足TFT LCD模組D036THEA1的圖形顯示。圖形資料可以從外接攝像頭獲取或者從FPGA晶片內產生圖形資料,本設計採用FPGA作為TFT LCD的控制,效能穩定,也可以靈活顯示引數以適應各種不同TFT LCD的控制。

目前,電子產品的生命週期越來越短,許多消費類電子產品的生命週期只有一年左右的時間,因而必須縮短產品的開發週期。可程式化邏輯裝置【1】與固定邏輯裝置相比,可大大縮短開發週期。而隨著積體電路製造工藝的進步,可程式化邏輯裝置的設計水平不斷提高,其成本已經降低到可以在消費類電子產品中大量使用的程度。從當前技術發展的趨勢來看,可程式化邏輯裝置將逐漸代替大部分的固定邏輯裝置。因此可程式化邏輯裝置應用是值得我們掌握的一門技術。

1.2 目的和意義

軟核處理器的出現以及可程式化邏輯裝置的片上記憶體容量的增大,使的可程式化邏輯裝置可以覆蓋數位電子領域中的所有應用。Altera公司推出的可程式化晶片系統以及NiosII軟核處理器【2】進一步明確了這個概念。DE2開發平臺是Altera公司針對大學及研究機構推出的一款多媒體開發平臺。通過使用DE2開發板可以做FPGA的開發設計及驗證。

本課題來源是科研與教學。是用於工業電子.國防.科研領域和日常生活中不可缺少的一部分。通過對其的瞭解而進一步認識現代社會人們所需要具備的技能。深入學習努力鑽研從而更好地運用到社會上去。

1.3國內外研究現狀及發展趨勢

嵌入式系統的將先進的計算機技術、半導體技術、電子技術和各個行業的具體應用相結合後的產物,這一點就決定了他並然是一個技術密集、資金密集、高度分散和不斷創新的知識整合系統。

FPGA並非是近年來才有的,FPGA—詞於1984年就已經出現,至今已經超過20年以上時間,不過過去十年時間內FPGA都未受到太多的重視,原因是FPGA的功耗用電、電路密度、頻率效能、電路成本都不如ASIC,在這十多年時間內,FPGA多半隻用在一些特殊領域,例如晶片業者針對新產品測試市場反應,即便初期產品未達量產規模,業能先以FPGA製成產品測試。或者有些晶片設計公司承接了小型的設計專案,在量產規模不足下業一樣使用FPGA,或如政府、軍方的特殊要求,不期望使用開放、標準性的晶片與電路,業會傾向使用FPGA。

不過如前所述的,在愈來愈多晶片無法用開設掩膜模式投產後,這些晶片一樣要上市,就只好以FPGA模式來生產。所幸FPGA也受益於摩爾定律,在工藝技術不斷提升下,電晶體愈來愈縮密化,原來相較ASIC遜色的電路密度過低、頻率效能過低、電路成本過高等問題,在新一代FPGA上,早已拉近與ASIC間的表現差距。

液晶顯示模組(LCM)採用的是Toppoly公司的TFTLCD模D036THEA1,可以接受RGB格式或YUV格式的8位元序列資料,支援NTSC時序或PAL時序,點陣為320×240,有效顯示面積為72.96×54.72mm,通過3線序列介面與LCM內部的暫存器交換資料來實現顯示控制和功能選擇。下圖7所示為TRDB_LCM彩色液晶顯示開發板。

TRDB_LCM可以用40腳電纜直接與DE2相連,引腳定義見下表1。

| 引腳編號 | 名稱 | 方向 | 含義 |

| 1~10 | NC | N/A | 未連線 |

| 11 | VCC5 | N/A | 5V電源 |

| 12 | GND | N/A | 地 |

| 13~20 | NC | N/A | 未連線 |

| 21 | DIN6 | 輸入 | LCD傳輸線第6位 |

| 22 | DIN7 | 輸入 | LCD傳輸線第7位 |

| 23 | DIN4 | 輸入 | LCD傳輸線第4位元 |

| 24 | DIN5 | 輸入 | LCD傳輸線第5位 |

| 25 | DIN2 | 輸入 | LCD傳輸線第2位 |

| 26 | DIN3 | 輸入 | LCD傳輸線第3位 |

| 27 | DIN0 | 輸入 | LCD傳輸線第0位 |

| 28 | DIN1 | 輸入 | LCD傳輸線第1位 |

| 29 | VCC33 | N/A | 3.3V電源 |

| 30 | NC | N/A | 未連線 |

| 31 | VSYNC | 輸入 | 垂直同步輸入 |

| 32 | NC | N/A | 未連線 |

| 33 | SCL | 輸入 | 3線序列介面時鐘 |

| 34 | DCLK | 輸入 | LCD資料時鐘 |

| 35 | GRESTB | 輸入 | 低電平有效的全域性復位訊號 |

| 36 | SHDB | 輸入 | 關斷控制,低電平有效 |

| 37 | CPW | N/A | 保留引腳 |

| 38 | SCEN | 輸入 | 3線序列介面使能 |

| 39 | SDA | 輸入/輸出 | 3線序列介面資料 |

| 40 | HSYNC | 輸入 | 水平同步輸入 |

表1 TRDB_LCM的引腳

TRDB_LCM的3線序列介面時序圖如圖8所示。SCEN為低電平時,3線序列介面有效,完成一次讀/寫暫存器的地址,第7位確定是讀還是寫,SDA為高電平則為讀,SDA為低電平則為寫,第8個時鐘週期SDA變為高阻狀態,最後8位元為讀或者寫的資料。

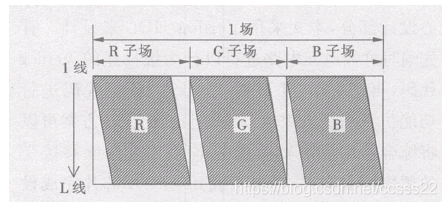

場序彩色顯示的原理【10】如圖1所示,主要是將一場的時間分成3個子場,在每個子場的時間內分別把影象的R、G、B訊號寫入顯示屏,並依次點亮紅綠藍三色光源,利用人眼的視覺暫留特性實現彩色影象的顯示。在R、G、B各子場時間內顯示屏顯示的都是單色影象資訊,而在一場時間當中R、G、B資訊分別顯示一次,所以我們看到的仍是一幅全綵色影象。如圖9所示。

module I2S_Controller( // Host Side

iCLK,

iRST,

iDATA,

iSTR,

oACK,

oRDY,

oCLK,

// Serial Side

I2S_EN,

I2S_DATA,

I2S_CLK );

// Host Side

input iCLK;

input iRST;

input iSTR;

input [15:0] iDATA;

output oACK;

output oRDY;

output oCLK;

// Serial Side

output I2S_EN;

inout I2S_DATA;

output I2S_CLK;

// Internal Register and Wire

reg mI2S_CLK;

reg [15:0] mI2S_CLK_DIV;

reg mSEN;

reg mSDATA;

reg mSCLK;

reg mACK;

reg [4:0] mST;

parameter CLK_Freq = 50000000; // 50 MHz

parameter I2S_Freq = 20000; // 20 KHz

// Serial Clock Generator

always@(posedge iCLK or negedge iRST)

begin

if(!iRST)

begin

mI2S_CLK <= 0;

mI2S_CLK_DIV <= 0;

end

else

begin

if( mI2S_CLK_DIV < (CLK_Freq/I2S_Freq) )

mI2S_CLK_DIV <= mI2S_CLK_DIV+1;

else

begin

mI2S_CLK_DIV <= 0;

mI2S_CLK <= ~mI2S_CLK;

end

end

end

// Parallel to Serial

always@(negedge mI2S_CLK or negedge iRST)

begin

if(!iRST)

begin

mSEN <= 1'b1;

mSCLK <= 1'b0;

mSDATA <= 1'bz;

mACK <= 1'b0;

mST <= 4'h00;

end

else

begin

if(iSTR)

begin

if(mST<17)

mST <= mST+1'b1;

if(mST==0)

begin

mSEN <= 1'b0;

mSCLK <= 1'b1;

end

else if(mST==8)

mACK <= I2S_DATA;

else if(mST==16 && mSCLK)

begin

mSEN <= 1'b1;

mSCLK <= 1'b0;

end

if(mST<16)

mSDATA <= iDATA[15-mST];

end

else

begin

mSEN <= 1'b1;

mSCLK <= 1'b0;

mSDATA <= 1'bz;

mACK <= 1'b0;

mST <= 4'h00;

end

end

end

assign oACK = mACK;

assign oRDY = (mST==17) ? 1'b1 : 1'b0;

assign I2S_EN = mSEN;

assign I2S_CLK = mSCLK & mI2S_CLK;

assign I2S_DATA = (mST==8) ? 1'bz :

(mST==17) ? 1'bz :

mSDATA ;

assign oCLK = mI2S_CLK;

endmodule