High-Level Synthesis高階綜合,跨越軟硬體編碼的隔閡

能將C語言轉換成硬體編碼語言的高階綜合HLS,跨越軟硬體編碼的隔閡,將軟體編碼的功能性與硬體編碼的高速性結合起來,藉助一些不斷改進中的HLS工具(FPGA三巨頭爭破頭),已然構成了一個時新的行業。雖然大多數HLS工具能夠自動將一些迴圈體或者介面進行優化,但其軟體轉換而來的結構始終難以達到資深硬體工程師的標準,故而目前HLS還是需要人工操作,針對軟體原始碼進行更細節的優化,並且已經有HLS工程師這一說,不過其要求比較苛刻,軟體程式設計和硬體程式設計是基礎,熟悉各種演演算法和數位電路是閃光點。

行業背景

FPGA設計挑戰

隨著FPGA密度隨著工藝幾何尺寸的縮小而不斷增長,設計複雜性使得繼續使用傳統的HDL設計流程變得越來越困難。儘管HDL語言和工具已經發展,但是設計週期仍然長得令人討厭。

今天,在所有領域都遇到了具有挑戰性的應用程式:高階駕駛員輔助系統(ADAS),5G,深度學習,計算機視覺,金融應用程式,航空航天和國防等。所有這些都需要幾個處理核心,通常具有複雜的控制結構。這導致處理流水線不容易實現。探索架構實現以找到最佳策略來滿足約束需要花費時間和成本,而且,專案進度壓力以及設計成本增加了對首次實現正確實現的需求。在開發的後期階段遇到瓶頸時,手工重構設計的某些部分實際上將使它步履維艱。

當需求改變時,經典的FPGA設計流程也會受到影響。在產品整合和驗證階段,經常出現後期規格變更或必須應用新約束的情況,這確實很常見。功能或效能的簡單更改可能需要進行大量的設計修改。這些設計修改可能要求對體系結構進行更新,從而導致重寫部分低階HDL實現。當然,這將導致潛在的較長的重新驗證週期。

HLS加速FPGA設計的優勢和挑戰

為了幫助解決該問題,出現了高階綜合(HLS)編譯器,以使設計人員能夠進入更高的抽象級別。這些對於設計的高度複雜部分特別有用,這些部分可以通過高階語言(例如C或C ++)輕鬆表達。更高的抽象級別使描述複雜演演算法和快速適應單調性變得更容易更改,更適合設計重用。

除了加快HDL設計的速度,HLS還具有簡化設計驗證的主要優勢。使用HLS,可以確保在門中正確實現高階C / C ++描述。不必進行擴充套件且費時的位級模擬。而且,由於HLS採取的高階C / C ++程式碼是可執行的,因此它也用於高階應用程式驗證。

HLS的另一個主要優點是能夠通過以偽指令的形式指導編譯器來快速探索不同的體系結構設計空間。這種能力是有代價的。為了指導編譯器,設計人員必須首先對程式碼以及資料在函數和迴圈中的移動方式有深刻的理解。 HLS編譯器是靜態工具,對理解程式碼的動態特性沒有任何幫助。此外,HLS編譯器的行為通常難以預測最終的效能和資源利用率。因此,設計人員必須通過對相應的程式碼部分應用各種編譯指示及其相關的引數設定,來手動探索設計空間,直到達到設計目標。

HLS工具流程

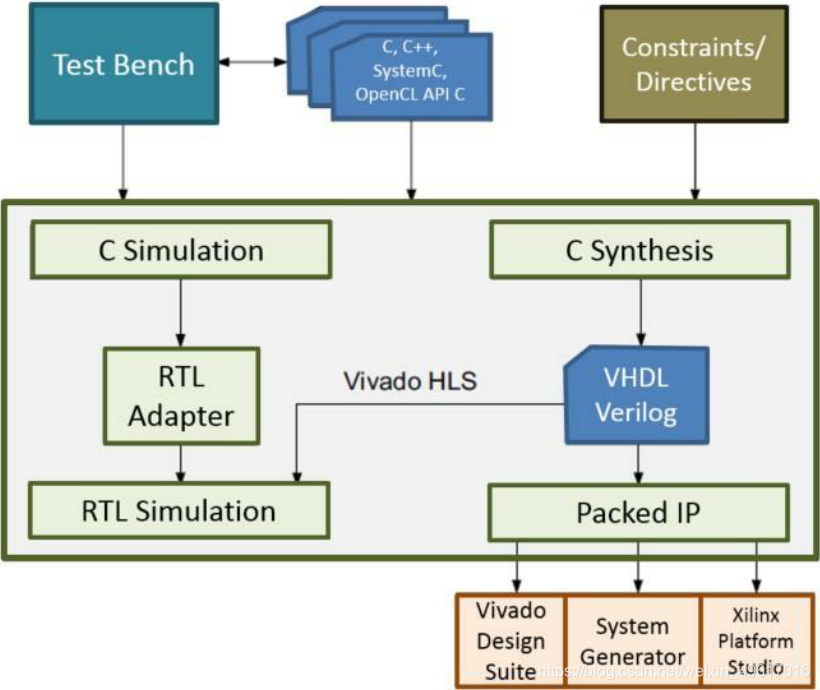

—>從C、c++、SystemC或OpenCL C開始

- 設計原始碼和測試平臺程式碼

—>C到RTL綜合

- 排程和對映資源;

- 生成通用RTL程式碼;

- 使用綜合指令進行優化

—>RTL驗證

- 使用原始的C測試臺;

- RTL模擬(XSim / ISim / ModelSim)

—>輸出到

- IP目錄;

- 系統生成器;

- DCP

HLS優勢

- 對於軟體工程,實現演演算法基於硬體(ASIC或者FPGA)的計算加速。

- 對於IC設計開發,從抽象的C層級進行功能設計。

- 對於硬體驗證,從更抽象的層次進行功能性驗證,加速設計流程。