Intel8251可程式化序列擴充套件RS232串列埠

隨著積體電路技術的發展,電子設計自動化(EDA)逐漸成為重要的設計手段,已經廣泛應用於模擬與數位電路系統等許多領域。電子設計自動化是一種實現電子系統或電子產品自動化設計的技術,它與電子技術,微電子技術的發展密切相關,它吸收了電腦科學領域的大多數最新研究成果,以高效能的計算機作為工作平臺,促進了工程發展。EDA的一個重要特徵就是使用硬體描述語言(HDL)來完成的設計檔案,VHDL語言是經IEEE確認的標準硬體語言,在電子設計領域受到了廣泛的接受。本文介紹了序列通訊的基本理論;綜述了EDA技術的發展概況,介紹了MAX+PLUSll軟體;熟悉Intel8251基本結構和工作原理;最後設計模擬了Intel8251的頂級功能模組和子功能模組.

在系統中嵌入式CPU 往往要通過各種序列資料匯流排與外界進行通訊,在應用中,非同步的序列資料通訊用得較多,而通用非同步收發器(UART Universal Asynchronous Receiver/Transmitter )在其中扮演著重要角色,它可以完成資料的串並轉換,即把並行資料按照通訊波特率轉化為通訊協定中規定的序列資料流,也可從序列資料流中取出有用資料轉變為並行資料。而UART 與CPU 介面簡單,CPU只需通過執行讀寫操作即可完成收發資料,從而完成與外界的通訊。有許多現成的晶片可以實現UART的功能:如常用的Intel8250/8251介面晶片就可以作為RS232、RS422串列埠的UART控制晶片。

FPGA/CPDL是20世紀90年代發展起來的大規模可程式化邏輯裝置,隨著EDA技術和微電子技術的進步,FPGA的時鐘延遲可達到ns級,結合其並行工作方式,在超高速、實時測控方面有非常廣闊的應用前景;並且FPGA具有高整合度、高可靠性,幾乎可以將整個設計系統下載於同一晶片中,實現所謂片上系統,從而大大縮小其體積,因此以FPAG/CLPD為代表的可程式化邏輯裝置受到了世界範圍內廣大電子設計工程師的普遍歡迎,應用日益廣泛。在國外,FGPA的技術發展與應用己達到相當高的程度;在國內,FPAG技術發展十分迅速,然而與國外相比還存在較大的差距。

2.1資料通訊概述

隨著人類社會的不斷進步、經濟的迅猛發展以及計算機的廣泛應用,人們對資訊的需求越來越大,資料通訊得到長足發展。

通訊的目的是雙方資訊的互知,是資訊的遠距離傳送。隨著社會的進步。傳統的電話、電報通訊方式已遠遠不能滿足大資訊量的需要。以資料作為資訊載體的通訊手段已成為人們的迫切要求。但「資料」還沒有統一嚴格的定義,一般可以這樣認為:資料是預先約定的具有某種含義的數位、字母或符號的組合。計算機出現以後,為了實現遠距離的資源共用,很快計算機就與通訊技術相結合,產生了資料通訊。所以說資料通訊是為了實現計算機與計算機或終端與計算機之間資訊互動而產生的一種通訊技術,是計算機與通訊相結合的產物。

綜上所述,可對資料通訊作如下定義:依照通訊協定,利用資料傳輸技術在兩個功能單元之間傳遞資料資訊。它可實現計算機與計算機、計算機與終端或終端與終端之間的資料資訊傳遞。

2.2資料傳輸方式

資料傳輸方式指的是通過某種方式建立一個資料傳輸通道將資料訊號在其中傳輸,它是資料通訊的基礎。資料的傳輸方式分為並行傳輸和序列傳輸,在序列傳輸中又分為非同步傳輸和同步傳輸。按照電路的傳輸能力,可以分為單工、半雙工、全雙工傳輸。

2.2.1 並行傳輸與序列傳輸

並行傳輸指的是資料以成組的方式,在多條並行通道上同時進行傳輸。常用的是將構成一個字元的幾位二進位制碼同時分別在幾個並行的通道上傳輸。另外加一條控制訊號即「選通」脈衝,它在資料訊號發出之後傳送,用以通知接收裝置所有的位己經傳送完畢,可以對各條通道上的訊號進行取樣了。收、發雙方不存在字元同步的問題,不需要額外的措施來實現收發雙方的字元同步,這是並行傳輸的主要優點。但是並行傳輸必須有多條並行通道,成本比較高,不適宜遠距離傳輸,因此一般較少使用。

序列傳輸指的是組成字元的若干位二進位制碼排列成資料流以序列的方式在一條通道上傳輸。通常傳輸順序為由低位到高位,傳完這個字元再傳下一個字元。因此收、發雙方必須保持字元同步,以使接收方能夠從接收的資料位元流中正確區分出與傳送方相同的一個一個的字元。這是序列傳輸必須解決的問題。序列傳輸只需要一條傳輸通道,易於實現,是目前主要採用的一種傳輸方式。

2.2.2 非同步傳輸與同步傳輸

在序列傳輸中,如何解決字元的同步問題,目前主要存在兩種方式:即非同步傳輸和同步傳輸。非同步傳輸方式的優點是實現字元同步比較簡單,收發雙方的時鐘訊號不需要嚴格同步。缺點是對每個字元都需加入起始位和終止位,因而傳輸效率低。

同步傳輸是以固定的時鐘節拍來傳送資料訊號的,因此在一個序列資料流中,各訊號碼元之間的相對位置是固定的(即同步)。接收方為了從接收到的資料流中正確地區分一個個訊號碼元,必須建立準確的時鐘訊號。與非同步傳輸方式相比,由於它傳送每一字元時不需要單獨加起始位和終止位,故具有較高的傳輸效率,但實現起來比較複雜。

有關非同步傳輸和同步傳輸的資料格式將在2.3中介紹。

2.2.3 單工、半雙工、全雙工傳輸

資料傳輸是有方向性的,根據資料電路的傳輸能力,可以有三種不同的傳輸方式或通訊方式。

(1)單工傳輸:傳輸系統的兩端資料只能沿單一方向傳送和接收,這種方式傳輸系統的一端固定為傳送端,另一端固定為接收端。反向通道的速率一般較低,為5-75bi/ts。實際應用中可以使用反向通道,也可以不用。氣象資料的收集、計算機與監視器及硬碟與計算機的資料傳輸就是單工傳輸的例子。

(2)半雙工傳輸:系統兩端可以在兩個方向上進行資料傳輸,但兩個方向的傳輸不能同時進行,當其中一端傳送時,另一端只能接收,反之亦然。無論哪一方開始傳輸,都使用通道的整個頻寬。對講機和民用無線電都是半雙工傳輸。

(3)全雙工傳輸:系統兩端可以在兩個方向上同時進行資料傳輸,即兩端都可同時傳送和接收資料。

綜上所述,非同步序列全雙工的資料傳輸方式是較為容易實現的方式,應用較為廣泛。

2.3序列通訊協定

資料通訊是在各種型別的使用者終端和計算機之間以及同一型號的計算機之間進行的。它不同於電話通訊方式,其通訊控制也複雜得多,因此必須有一系列行之有效的、共同遵守的通訊協定。所謂通訊協定是指通訊雙方的一種約定,約定包括對資料格式、同步方式、傳送速度、傳送步驟、檢糾錯方式以及控制字元定義等問題做出統一規定,通訊雙方必須共同遵守。因此,也叫做通訊控制規程,或稱傳輸控制規程,它屬於國際標準化組織ISO(International Standards Organization)的開放系統互連OSI(Open System Interconnection)七層參考模型中的資料鏈路層口。

2.3.1序列通訊介面標準

序列通訊介面按電氣標準及協定來劃分包括Rs-232、Rs-422、Rs485、LVDS等。RS-232、RS-422與RS-485標準只對介面的電氣特性做出規定,不涉及接外掛、電纜或協定。LVDS是近幾年發展起來的新型介面標準,主要應用於高速資料傳輸領域。

(l)RS-232序列介面

1969年,美國電子工業協會(EIA)公佈了RS-232作為序列通訊介面的電氣標準,該標準定義了資料終端裝置(DTE)和資料通訊裝置(DCE)間按位元序列傳輸的介面資訊,合理安排了介面的電氣訊號和機械要求。目前RS-232是PC機與通訊工業中應用最廣泛的一種序列介面。RS-232被定義為一種在低速率序列通訊中增加通訊距離的標準,它採取不平衡傳輸方式,即所謂單端通訊。典型的RS-232訊號在正負電平之間擺動,在傳送資料時,傳送端驅動器輸出正電平在+5到+l5V,負電平在-5到-15v電平。當無資料傳輸時,線上為TTL電平,從開始傳送資料到結束,線上電平從TTL電平到RS-232電平再返回TTL電平。接收器典型的工作電平在+3到+l2v與-3到-12v。Rs-232是為對等(即只用一對收、發裝置)通訊而設計的,其驅動器負載為3到7k。。由於RS-232傳送電平與接收電平的差僅為2V至3V左右,所以其共模抑制能力差,再加上雙絞線上的分佈電容,其傳送距離最大為約30米,最高速率為20kb/s。所以RS-232適合本地裝置之間的通訊。

(2)RS-422序列介面

RS-422-B全名為「平衡電壓數位介面電路的電氣特性」 (Electrical Characteristics of Balanced Voltage Digital Interface Circuits),它是美國電子工業協會EIA(Electronic Industry Association)制定的一種序列物理介面標準。RS是英文「推薦標準」的縮寫,422為標識號,B表示修改次數。

RS-422由RS-232發展而來,它是一種單機傳送、多機接收的單向、平衡傳輸規範。為改進RS-232通訊距離短、速度低的缺點,RS-422定義了一種平衡通訊介面,將傳輸速率提高到10Mbit/s,並允許在一條平衡匯流排上連線最多10個接收器。

RS-422採用平衡驅動,差分接收電路,即在傳送端,驅動器將TTL電平訊號轉換成差分訊號輸出;在接收端,接收器將差分訊號變成CMOS/TTL電平。從根本上取消了訊號地接法,大大減少了地電平所帶來的共模干擾。平衡驅動器相當於兩個單端驅動器,其輸入訊號相同,兩個輸出訊號互為反相訊號。外部輸入的干擾訊號是以共模方式出現的,兩根傳輸線上的共模干擾訊號相同,因接收器是差分輸入,共模訊號可以相互抵消,從而大大提高了抗共模干擾的能力,並能在較長距離內明顯提高傳輸速率。

RS-422的資料訊號採用差分傳輸方式,也稱作平衡傳輸。它使用一對雙絞線,將其中一線定義為A,另一線定義為B。通常情況下,傳送驅動器之間的差分電壓正電平在+2V - +6V,是一個邏輯狀態,負電平在-2V - 6V之間,是另一個邏輯狀態。另有一個訊號地C。在RS一485中還有一「使能」端,「使能」端是用於控制傳送驅動器與傳輸線的切斷與連線。當「使能」端起作用時,傳送驅動器處於高阻狀態,稱作「第三態」,即它是有別於邏輯「1」與「0」的第三態。介面訊號電平比RS-232-C降低了,就不易損壞介面電路的晶片,且該電平與TTL電平相容,可方便與TTL電路連線。

接收器作與傳送端相對的規定,收、發端通過平衡雙絞線將AA與BB對應相連,當在接收端AB之間有大於+200mV的電平時,輸出正邏輯電平,小於-200mV時,輸出負邏輯電平。定義A端B端與地之間電壓的平均值為共模電壓,RS-422接收器可以承受[-7V,+7V]的共模電壓。接收器符號見圖2.1。

|

A |

|

B |

|

DOUT |

圖2.1 平衡差分輸入線接收器

由於接收器採用高輸入阻抗和傳送驅動器比RS-232更強的驅動能力,故RS-422允許在相同傳輸線上連線多個接收節點,最多可接10個節點。即一個主裝置(Master),其餘為從裝置(Slave),從裝置之間不能通訊,所以RS-422支援點對多的雙向通訊。RS-422四線介面由於採用單獨的傳送和接收通道,因此不必控制資料方向,各裝置之間任何必須的訊號交換均可以按軟體方式(XON漢OFF握手)或硬體方式(一對單獨的雙絞線)實現。

RS-422的最大傳輸距離為4000英尺(約1200米),最大傳輸速率為10Mb/s。其平衡雙絞線的長度與傳輸速率成反比在100kb/s速率以下刁一可能達到最大傳輸距離。

(3)RS-485序列介面

為擴充套件應用範圍,EIA在RS-422的基礎上制定了RS-485標準,增加了多點、雙向通訊能力,通常在要求通訊距離為幾十米至上千米時,廣泛採用RS-485收發器。

RS-485許多電氣規定與RS-422相仿。如都採用平衡傳輸方式、都需要在傳輸線上接終端電阻等。RS-485可以採用二線與四線方式,二線制可實現真正的多點雙向通訊。而採用四線連線時,與RS-422一樣只能實現點對多的通訊,即只能有一個主(Master)裝置,其餘為從裝置,但它比RS一422有改進,無論四線還是二線連線方式匯流排上可連線多達32個裝置,SIPEX公司新推出的SP485R最多可支援400個節點。

RS-485與RS-422的共模輸出電壓是不同的。RS-485共模輸出電壓在-7V至+l2V之間,RS-422在-7V至+7V之間,RS-485接收器最小輸入阻抗為12k;RS-422是4k;RS-485滿足所有RS-422的規範,所以RS-485的驅動器可以用在RS-422網路中應用。但RS-422的驅動器並不完全適用於RS-485網路。

為方便起見將上述幾種主流通訊介面的電氣特性比較列表如表2.1:

表2.1 RS-232\RS-422\RS-485電氣特性比較

| 規定 | RS-232 | RS-422 | RS-485 |

| 工作方式 | 單端 | 差分 | 差分 |

| 節點數 | 1收1發 | 10收1發 | 32收1發 |

| 最大傳輸速率 | 20Kb\s | 10Mb\s | 10Mb\s |

| 最大驅動電壓 | +\-25V | -0.25V-+6V | -7V-+12V |

| 接收器輸入電壓範圍 | +\-15V | -10V-+10V | -7V-+12V |

| 接收器輸入門限 | +\-3V | +\-200mV | +\-200mV |

| 接收器輸入電阻 | 3K-7K | 4K(最小) | 12K |

| 驅動器共模電壓 |

| +\-3V | -1V-+3V |

| 接收器共模電壓 |

| +\-7V | -7V-+12V |

RS-232序列介面屬於個人計算機(PC)及電信應用領域中最為成功的序列資料標準;而RS-422和RS-485序列介面則是工業應用領域中最為成功的序列資料標準。由於可減少佈線成本並實現較長的傳輸距離,RS-422和RS-485序列介面被廣泛應用於汽車電子裝置、銷售點終端(POs)、工業控制、儀器儀表、區域網、蜂窩基站及電信領域,較高的輸入電阻允許多個節點連至匯流排上。由於該類電路的優異效能,國外市場上目前己經出現了種類繁多的同類電路。幾乎國際上幾家大的積體電路開發公司都有相關產品,產品型號不勝列舉。但大多為雙極工藝製造,採用CMOS工藝製作的產品還不多。

(4)LVDS

在被稱為資訊時代的今天,為適應資訊化的高速發展,高速處理器、多媒體、虛擬現實以及網路技術對訊號的頻寬要求越來越大,多通道應用日益普及,所需傳送的資料量越來越大,速度越來越快,l0Mbps的速率已然不能滿足現代計算機之間高速互聯的要求。因此採用新的技術解決I/O介面問題成為必然趨勢,LVDS這種高速低功耗介面標準為解決這一瓶頸問題提供了可能。

LVDS介面又稱RS-644匯流排介面,是20世紀90年代才出現的一種資料傳輸和介面技術。LVDS的全稱為Low Voltage Differential Signal,即低電壓差分訊號,這種技術的核心是採用極低的電壓擺幅高速差動傳輸資料,可以實現對等或一點對多點的連線,具有低功耗、低誤位元速率、低串擾和低輻射等特點。LVDS在對訊號完整性、低抖動及共模特性要求較高的系統中得到了越來越廣泛的應用。目前,流行的LVDS技術規範有兩個標準:一個是TI/EIA的ANSI/TIA/EIA-644標準,另一個是IEEEI596.3標準。這兩個標準注重於對LVDS介面的電特性、互連與線路端接等方面的規範,對於生產工藝、傳輸媒介和供電電壓等則沒有明確規定。LVDS可採用CMOS、GaAs或其他技術實現,其供電電壓可以從+5V到+3.3V,甚至更低;其傳輸媒介可以是銅質的PCB連線,也可以是平衡電纜。標準推薦的最高資料傳輸速率是655Mbps,而理論上,在一個無衰耗的傳輸線上,LVDS的最高傳輸速率可達1.923Gbps。

LVDS技術之所以能夠解決目前物理層介面的瓶頸,正是由於其在速度、噪聲、EMI、功耗、成本等方面的優點:

①高速傳輸能力:LVDS技術的恆流源模式低擺幅輸出意味著LVDS能高速驅動,例如:對於點到點的連線,傳輸速率可達800MbPs;對於多點互連FR4背板,十塊卡作為負載插入匯流排,傳輸速率可達400Mbps。

②低噪聲:LVDS產生的電磁干擾低。這是因為低電壓擺幅、低邊沿速率、奇模式差分訊號以及恆流驅動器的Iss尖峰只產生很低的輻射。在傳輸線上流過大小相等、極性相反的電流,電流在該線對內返回,使面積很小的電流回路產生最低的電磁干擾。當差分傳輸線緊藕合時,串入的訊號是作為共模電壓出現在接收器輸入的共模噪聲中,差分接收器只響應正負輸入之差。因此當噪聲同時出現在2個輸入中時,差分訊號的幅度並不受影響。共模噪聲抑制也同樣適用於其它噪聲源,比如電源波動、襯底噪聲和接地回跳等。

③低功耗:LVDS器件是用CMOS工藝實現的,這就提供了低的靜態功耗。同時LVDS使用恆定電流源驅動器,隨著工作頻率的增加,其電源電流仍然保持平坦,而CMOS和TTL技術的電源電流則隨頻率增加而呈指數上升。因此,恆定電流驅動模式大大減少了LVDS的功耗。從對負載功率的計算(3.5mA電流乘以100歐終端電阻上的350mV壓降)可看到LVDS僅有1.2mW的功耗。作為對比,TTL在負載電阻上有1V壓降,負載電流為40mA,因而負載功耗為40mW。

④節省成本:LVDS器件採用經濟的CMOS工藝製造,用低成本的電纜線和聯結器件就可以達到很高的速率。由於功耗較低,電源,風扇等其他散熱開銷就大大降低。LVDS產生極低的噪聲,噪聲控制和EMI等問題迎刃而解。與並行連線相比,可以減少大量的電纜,聯結器和麵積費用。

⑤整合能力強:由於可在標準CMOS工藝中實現高速LVDS,因此用LVDS類比電路整合複雜的數位功能是非常有利的。LVDS內整合的序列化器和解序列化器使它能在一個晶片上整合許多通道。較窄的鏈路大大減少了引腳數量和鏈路的總費用。差分訊號能承受高電平的切換噪聲,因而能用大規模數位電路進行可靠的整合。恆定電流的輸出模式使LVDS只產生很低的噪聲,因此能實現完整的晶片介面系統。

目前LVDS技術在傳輸距離上有其侷限性,一般應用在20m以下。

LVDS的顯著優勢使得其應用範圍遠遠超過那些傳統器件,標準LVDS產品可廣泛應用於計算機、通訊、消費電子、顯示等領域。LVDS擁有低噪聲的特色,最適用於筆記掌上型計算機的液晶顯示器。平板顯示器連結需要將大量的顯示資料從筆電計算機傳送到平板顯示器。美國國家半導體公司(NSC)和日本幾家筆記型電腦生產商合作定義了FPD-Link標準用於平板顯示器的連結,並生產出使用LVDS方式傳輸的樣片。此外,NSC公司還建立基於LVDS的低擺幅差分訊號標準RSDS,該標準將LVDS的效能特點應用到平板顯示器的列驅動電路與TCON的晶片的連線上。它在功耗、噪聲等方面有進一步改善,為LVDS在顯示技術領域的應用提供了新的機遇。

高速序列通訊也是LVDS最引人注目的應用之一。為實現並行資料並串及串並轉換功能,德州儀器公司(TI)日前宣佈推出一系列新型通用多晶片組器件,該系列器件充分發揮了TI在資料傳輸技術方面的設計經驗和優勢。就低電壓差分訊號(LVDS)鏈路資料傳輸而言,新系列產品是業界用途最為廣泛的資料並串、串並轉換器解決方案。採用該解決方案,設計人員不僅能將電線或電路板走線的數量減少一半以上,而且可將資料傳輸距離提高10倍。與其它串並轉換器解決方案不同,MuxIt系列產品可高度適應各種匯流排寬度和速度,應用領域包括電信、列印/影印機、視訊成像和消費類產業等。

目前,LVDS技術日益受到中國電路設計工程師的重視,LVDS應用前景廣闊,在國內的發展非常迅猛。例如銀河巨型機的高速互連傳輸中就採用了LVDS技術。但是國內使用的基本上都是國外廠商提供的成品,幾乎沒有自主設計的LVDS核心電路和晶片。令人欣慰的是,國內現在己經有幾家公司正在研發LVDS核心電路和晶片。

4.2.1 FPGA一般開發流程

一般FPAG的開發大體有如下幾個步驟:設計輸入一>功能模擬一>程式碼綜合一>實現一>下載。其中最重要的顯然是設計部分,因為產品的功能就是在設計上體現出來的;而模擬主要針對設計,採用DEA工具進行波形模擬,只有波形模擬通過才能說明設計的正確性與合理性;綜合主要是將用HDL語言所作的硬體描述對應到FPAG晶片上的單位邏輯電路上;實現是將綜合後生成的邏輯網表與具體的FGPA相適配;最終生成的位流檔案通過某種下載途徑下載到FPAG中。

4.2.2 本課題設計難點

在每一個設計模組當中,沒有統一的時鐘脈衝訊號,狀態變化的時刻是不固定的,通常輸入訊號只有在電路處於穩定狀態時才發生變化。也就是說,一個時刻僅允許一個輸入發生變化,以避免輸入訊號之間造成的競爭冒險現象。在設計北京化工大學碩士學位論文和使用時序電路時,必須考慮到器件的傳輸延時,注意競爭冒險問題,注意由於時鐘偏移造成的冒險。

設計過程中,根據理論分析,如果各個模組的復位訊號頻率存在偏差,將使得輸入輸出之間的訊號,不能正常完成轉換,同時,雖然各個模組在單獨工作的情況下,均能完成各自的功能,但如果將模組合成,就可能出現各種意想不到的問題。

對於CRc校驗用於非同步序列通訊的方法,有關軟體處理流程的資料很少。並且其介面時序涉及軟硬體的協同操作以及軟體硬體控制的相互轉換,因此是本設計的一大技術難點。

傳統設計過程中,CRC通常應用於同步序列通訊,至於在非同步序列通訊中的應用,其是否可行,還有待進一步分析。

4.2.3 UART的設計與實現

UART(UuvlesraiAs」chronousReeeiverTrnasmitte)r即通用非同步收發器,是一種應用廣泛的短距離序列傳輸介面。往往用於短距離、低速、低成本的微機與下位機的通訊中。8250,8251,NS16450等晶片都是常見的UART器件。這類晶片有些已經做得相當複雜,含有許多輔助的模組,比如FIFO。在本節裡僅討論最基本的UART,其實也是最常用的。

4.2.3.1 傳送模組的設計

首先來設計URAT的傳送模組,根據系統的要求我們首先定義如下的管腳:

mclkx16 : IN std_logic; --系統時鐘

write : IN std_logic; --寫時鐘

reset : IN std_logic; --復位,0工作,1復位

data : IN std_logic_vector(7 downto 0); --8位元並行資料輸入

tx : OUT std_logic ; --序列輸出

txrdy : OUT std_logic --標誌位

該模組的模擬波形圖如下圖所示:

![]()

圖4-1

當訊號傳送的01000110的時候,將並行訊號變為序列訊號,data[0]=0, data[1]=1, data[2]=1, data[3]=0, data[4]=0, data[5]=0, data[6]=1, data[7]=0,後3位的010為該資料的校驗訊號位。由此我們驗證了系統傳送部分的正確性。

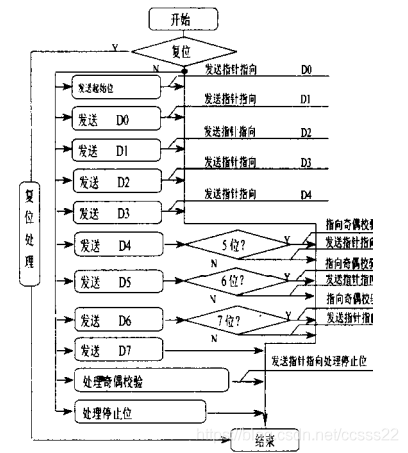

圖4-2

上圖中狀態的轉移是靠一個內部變數(Variable)來實現的,該變數在進行完當前狀態的處理後指向下一個將處理的狀態,程序(Process)的每一次處理都根據變數的內容進行相應狀態的處理,由於其功能就像一個指標,因此我們稱之為接收或傳送指標。

其中的訊號的轉換過程如下:

tsr <= '0'&tsr(7 downto 1);

tsr(7) <= tag1;

tag1 <= tag2;

tag2 <= '0';

txparity <= txparity XOR tsr(0);

IF (txdone = '1') THEN

tx <= '1';

ELSIF (paritycycle = '1') THEN

tx <= txparity;

ELSE

tx <= tsr(0);

END IF;

通過這個程式碼可以將並型訊號轉為串型訊號,將序列訊號傳送出去。

其中訊號的校驗公式如下:

paritycycle <= tsr(1) AND NOT (tag2 OR tag1 OR tsr(7) OR tsr(6) OR tsr(5) OR tsr(4) OR tsr(3) OR tsr(2));

4.2.3.2 接收模組的設計

首先來設計URAT的傳送模組,根據系統的要求我們首先定義如下的管腳:

mclkx16 : IN std_logic; -- 輸入時鐘

read : IN std_logic; -- 讀取訊號

rx : IN std_logic; -- 接收到的訊號

reset : IN std_logic; -- 復位

rxrdy : OUT std_logic; -- 接收的資料準備讀取

parityerr : OUT std_logic; -- 接收校驗標誌

framingerr : OUT std_logic;

overrun : OUT std_logic;

data : OUT std_logic_vector(7 downto 0)); -- 8 bit 資料輸出該模組的模擬波形圖如下圖所示:

圖4-3

當訊號接收串型訊號01101010的時候,將序列訊號變為並行訊號,data[0]=0, data[1]=1, data[2]=1, data[3]=0, data[4]=1, data[5]=0, data[6]=1, data[7]=0。由此我們驗證了系統傳送部分的正確性。

下面來具體介紹傳送部分的工作流程:

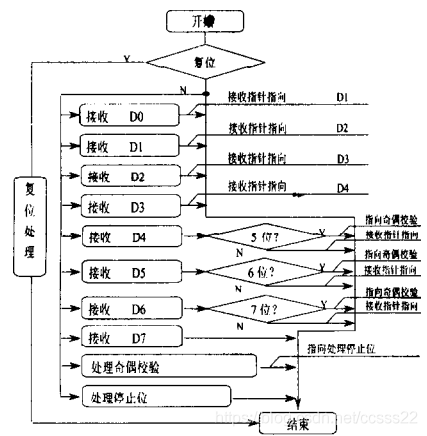

圖4-4

接收處理首先完成起始位的檢測,並自己產生接收時序控制訊號,在控制訊號的控制下,逐位接收序列輸入資料,並根據控制字判斷接收資料位數,完成資料的接收後,進行奇偶校驗位的判斷,最後判斷停止位。在接收的過程中設定接收狀態輸出訊號。

其中的訊號的轉換過程如下:

sample_data : PROCESS (rxclk, reset)

BEGIN

IF (reset = '1') THEN

-- idle_reset

rsr <= "11111111";

rxparity <= '1';

paritygen <= paritymode;

rxstop <= '0';

ELSIF (rxclk='1') AND (rxclk'EVENT) THEN

IF (idle='1') THEN

-- idle_reset

rsr <= "11111111";

rxparity <= '1';

paritygen <= paritymode;

rxstop <= '0';

ELSE

-- shift_data

rsr <= '0'&rsr(7 downto 1);

rsr(7) <= rxparity;

rxparity <= rxstop;

rxstop <= rx;

paritygen <= paritygen XOR rxstop;

END IF;

END IF;

END PROCESS;

通過這個程式,我們可以講接收端的序列訊號變為原始的序列訊號。

4.3 FPAG的綜合

在完成了系統邏輯的設計和功能模擬後,我們要對所生成的VHDL檔案進行綜合,生成門級網表檔案,這些檔案只是一些門與或非的邏輯關係,與實際的設定還有差距。我們需要對他們進行佈局佈線和時序驗證,來實現晶片內部功能單元的連線和對映哪腳。

在這些工作完成後,即可開始對設計進行綜合並優化。其中對設計的約束在整個綜合過程中的作用至關重要,它可以方便控制綜合、實現過程,使設計滿足執行速度、引腳位置等方面的要求,可以說約束是關係到整個FPGA實現成功與否的關鍵。我們採用編寫約束檔案並將其匯入到綜合、實現工具的方法。由於時鐘訊號具有高扇出的特點,所以必須給時鐘加上全域性緩衝器,另外全域性緩衝器還可以減少時鐘歪斜(clockskew),使得設計在佈線階段可以更容易,並取得最佳的效果。

另外,在器件結構允許的情況下,即器件提供全域性緩衝器足夠多的時候,應該給高扇出的訊號也加上全域性緩衝器,比如系統復位訊號等,以增加其驅動能力。

另外,對埠的約束也有利於PCB圖的完成。

對於數位電路來說,提高工作頻率也是非常重要的,因為高工作頻率意味著高處理能力。但由於本次實驗的頻率不是太高,所以我們約束頻率預設,這是因為時脈頻率較低時,不加約束自動綜合也能達到要求。在這個設定下,綜合工具往往會追求最小面積(消耗最少的閘電路)。

完成上面的工作後,我們要進行時序驗證。時序驗證的方法的主要方法包括SAT 和後模擬。在後模擬中將佈局佈線的時延反標到設計中去,使模擬既包含門延時,又包含線延時資訊。這種後模擬是最準確的模擬,能較好地反映晶片的實際工作情況。模擬工具與綜合前模擬工具相同。我們本次實驗主要根據靜態時序分析。綜合結束後,我們的工作進入了實現階段。實現的流程大體可分為以下幾個階段:編譯規劃、佈局佈線、程式位元流檔案的產生。

矽片上的資源進行對映性規劃,並檢查物理設計規則。規劃對映完FPGA設計之後,就是佈局和佈線。在佈局步驟中,主要在於把整個的邏輯塊,包括邏輯設定塊(CLB)和輸入瀚出塊(IOB)分配到電路片土的特定位置上去。如果在部分的邏輯元件中放置了時序約束,那麼佈局器就會通過移動相應的邏輯塊使它們靠近,以滿足它們的約束。在佈線階段中,把邏輯網路分配到電路片中與邏輯元胞互連的物理線段上去。如果在部分的邏輯元件中放置了時序約束,那麼佈線器就會嘗試選項擇快速的連線以滿足它們的約束。

附錄

·傳送模組:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY txmit IS

PORT (

mclkx16 : IN std_logic; --系統時鐘

write : IN std_logic; --寫時鐘

reset : IN std_logic; --復位,0工作,1復位

data : IN std_logic_vector(7 downto 0); --8位元並行資料輸入

tx : OUT std_logic ; --序列輸出

txrdy : OUT std_logic --標誌位

);

END txmit;

--以下定義一些中間變數,具體使用在以下模組中介紹

ARCHITECTURE behave OF txmit IS

SIGNAL write1, write2 : std_logic;

SIGNAL txdone1, txdone : std_logic;

SIGNAL thr, tsr : std_logic_vector(7 downto 0);

SIGNAL tag1, tag2 : std_logic;

CONSTANT paritymode : std_logic :='1';

SIGNAL txparity : std_logic;

SIGNAL txclk : std_logic;

SIGNAL paritycycle : std_logic;

SIGNAL txdatardy : std_logic;

SIGNAL cnt : std_logic_vector(2 downto 0);

BEGIN

--校驗公式

paritycycle <= tsr(1) AND NOT (tag2 OR tag1 OR tsr(7) OR tsr(6) OR tsr(5) OR tsr(4) OR tsr(3) OR tsr(2));

txdone <= NOT (tag2 OR tag1 OR tsr(7) OR tsr(6) OR tsr(5) OR tsr(4) OR tsr(3) OR tsr(2) OR tsr(1) OR tsr(0));

txrdy <= NOT txdatardy;

--當寫訊號為0的時候講資料打入暫存器THR中,THR是一箇中間變數

thr_write : PROCESS (write, data)

BEGIN

IF (write = '0') THEN

thr <= data;

END IF;

END PROCESS;

--生成一個分頻後的時鐘,16分頻

baud_clock_gen : PROCESS (mclkx16, reset)

BEGIN

IF (reset ='1') THEN

txclk <= '0';

cnt <= "000";

ELSIF (mclkx16='1') AND mclkx16'EVENT THEN

IF (cnt = "000") THEN

txclk <= NOT txclk;

END IF;

cnt <= cnt + 1;

END IF;

END PROCESS;

--轉換過程。

shift_out : PROCESS (txclk, reset)

BEGIN

IF (reset = '1') THEN

tsr <= (OTHERS => '0');

tag2 <= '0';

tag1 <= '0';

txparity <= paritymode;

tx <= '1';

--idle_reset;

ELSIF txclk = '1' AND txclk'EVENT THEN

IF (txdone='1' AND txdatardy = '1') THEN

-- load_data;

tsr <= thr;

tag2 <= '1';

tag1 <= '1';

txparity <= paritymode;

tx <= '0';

ELSE

-- shift_data; --一下幾行就是並-》串的過程。

tsr <= '0'&tsr(7 downto 1);

tsr(7) <= tag1;

tag1 <= tag2;

tag2 <= '0';

txparity <= txparity XOR tsr(0);

IF (txdone = '1') THEN

tx <= '1';

ELSIF (paritycycle = '1') THEN

tx <= txparity; --輸出校驗位

ELSE

tx <= tsr(0);

END IF;

END IF;

END IF;

END PROCESS;

--幾個控制訊號的生成

PROCESS (mclkx16, reset)

BEGIN

IF (reset='1') THEN

txdatardy <= '0';

write2 <= '1';

write1 <= '1';

txdone1 <= '1';

ELSIF mclkx16 = '1' AND mclkx16'EVENT THEN

IF (write1 = '1' AND write2 = '0') THEN

txdatardy <= '1';

ELSIF (txdone = '0' AND txdone1 = '1') THEN

txdatardy <= '0';

END IF;

write2 <= write1;

write1 <= write;

txdone1 <= txdone;

END IF;

END PROCESS;

END behave;

·接收模組:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY rxcver IS

PORT (mclkx16 : IN std_logic; -- 輸入時鐘

read : IN std_logic; -- 讀取訊號

rx : IN std_logic; -- 接收到的訊號

reset : IN std_logic; -- 復位

rxrdy : OUT std_logic; -- 接收的資料準備讀取

parityerr : OUT std_logic; -- 接收校驗標誌

framingerr : OUT std_logic;

overrun : OUT std_logic;

data : OUT std_logic_vector(7 downto 0)); -- 8 bit 資料輸出

END rxcver;

--定義的中間變數

ARCHITECTURE behave OF rxcver IS

SIGNAL rxcnt : std_logic_vector(3 downto 0);

SIGNAL rx1, read1, read2, idle1 : std_logic;

SIGNAL hunt : std_logic;

SIGNAL rhr : std_logic_vector(7 downto 0);

SIGNAL rsr : std_logic_vector(7 downto 0);

SIGNAL rxparity : std_logic;

SIGNAL paritygen : std_logic;

SIGNAL rxstop : std_logic;

CONSTANT paritymode : std_logic := '1';

SIGNAL rxclk : std_logic;

SIGNAL idle : std_logic;

SIGNAL rxdatardy : std_logic;

BEGIN

idle_preset : PROCESS (rxclk, reset)

BEGIN

IF reset = '1' THEN

idle <= '1';

ELSIF rxclk'EVENT AND rxclk='1' THEN

idle <= (NOT idle) AND (NOT rsr(0));

END IF;

END PROCESS;

--時鐘分頻

rxclk_sync : PROCESS (mclkx16, reset)

BEGIN

IF reset='1' THEN

hunt <= '0';

rxcnt <= "0001";

rx1 <= '1';

rxclk <= '0';

ELSIF (mclkx16='1') AND mclkx16'EVENT THEN

IF (idle='1' AND rx='0' AND rx1='1') THEN

hunt <= '1';

ELSE

IF (idle='0' OR rx='1') THEN

hunt <= '0';

END IF;

IF (idle ='0' OR hunt='1') THEN

rxcnt <= rxcnt + 1;

ELSE

rxcnt <= "0001";

END IF;

END IF;

rx1 <= rx;

rxclk <= rxcnt(3);

END IF;

END PROCESS;

--校驗位判斷過程和資料轉換

sample_data : PROCESS (rxclk, reset)

BEGIN

IF (reset = '1') THEN

-- idle_reset

rsr <= "11111111";

rxparity <= '1';

paritygen <= paritymode;

rxstop <= '0';

ELSIF (rxclk='1') AND (rxclk'EVENT) THEN

IF (idle='1') THEN

-- idle_reset

rsr <= "11111111";

rxparity <= '1';

paritygen <= paritymode;

rxstop <= '0';

ELSE

-- shift_data

rsr <= '0'&rsr(7 downto 1);

rsr(7) <= rxparity;

rxparity <= rxstop;

rxstop <= rx;

paritygen <= paritygen XOR rxstop;

END IF;

END IF;

END PROCESS;

--標誌訊號的生成

generate_flag : PROCESS (mclkx16, reset)

BEGIN

IF (reset='1') THEN

rhr <= "00000000";

rxdatardy <= '0';

overrun <= '0';

parityerr <= '0';

framingerr <= '0';

idle1 <= '1';

read2 <= '1';

read1 <= '1';

ELSIF (mclkx16='1') AND (mclkx16'EVENT) THEN

IF (idle='1' AND idle1='0') THEN

IF (rxdatardy='1') THEN

overrun <= '1';

ELSE

overrun <= '0';

rhr <= rsr;

parityerr <= paritygen;

framingerr <= NOT rxstop;

rxdatardy <= '1';

END IF;

END IF;

IF (read2 = '0' AND read1='1') THEN

rxdatardy <= '0';

parityerr <= '0';

framingerr <= '0';

overrun <= '0';

END IF;

idle1 <= idle;

read2 <= read1;

read1 <= read;

END IF;

END PROCESS;

rxrdy <= rxdatardy;

latch_data : PROCESS (read, rhr)

BEGIN

IF (read = '1') THEN

data <= rhr;

END IF;

END PROCESS;

END behave;