Ambarella_CV2X_SOC_PLATFORM_海思AI方案的強力競爭對手

The Ambarella CV2x 5M SoC includes an advanced CVflow computer vision processing engine

,a 1 GHz quad-core Arm Cortex-A53 CPUs,a 5M H.264/H.265 encoder,a high-performance digital signal processor(DSP) subsystem with an Ambarella image sensor processor(ISP),ISP functions such as 3A,high dynamic range(HDR),dewarping,and 3D noise reduction are provided,The flexible high-definition CV2x H.264/H.265 codec delivers recording up to 5Mp30 HEVC +1080p30 HEVC+5Mp4 MJPEG resolution,including a high-quality,low-latency secondary stream

CV2x supports multiple sensor interfaces,enabling a wide range w of popular CMOS sensors up to 32-MPixel resolution and up to 640 Mpixels/s input rate.

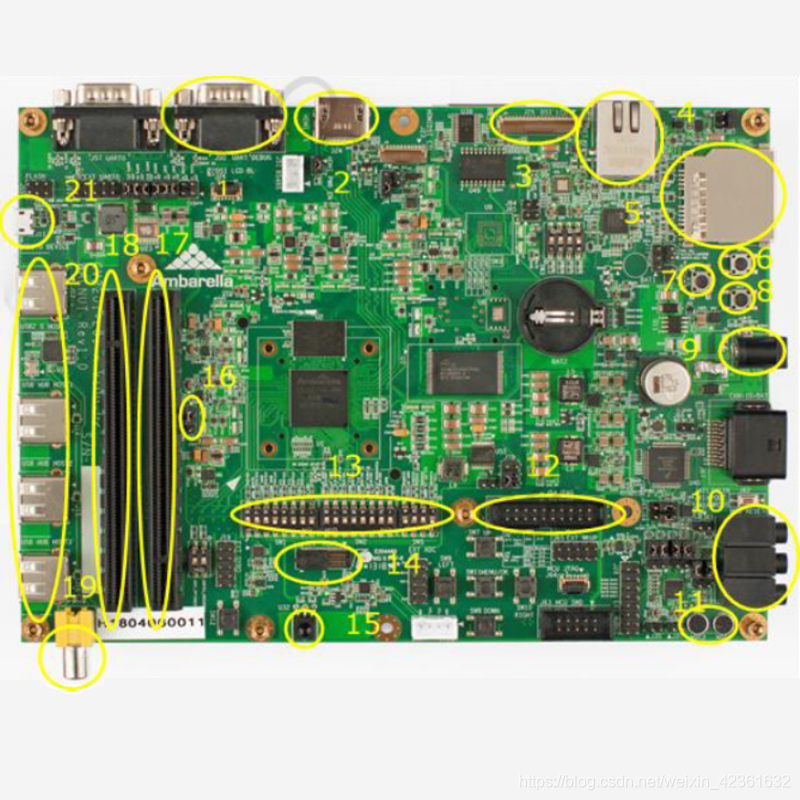

The major components and I/O connectors identified in the figure above are as follows:

1.Debug UART

2.HDMI VUUT

3.Digital DSI LCD SD/SDXC card(The card at the top supports the eMMC card direct boot,the card at the bottom does not)

5.Ethemet

6.Internal power on/off

7.Reset

8.External power on/off

9.12V DC power

10.Stereo MIC

11.Audio Line-in/Line-Out/HP-Out

12.JTAG

13.IR-receiver

14.DIP switches

15.Digital VOUT

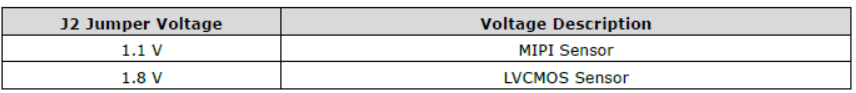

16.J2

17.VIN 2

18.VIN 1(VIN interface current used)

19.CVBS VOUT

20.USB Host

21.USB Device

Ambarella AI chip supports ARM + DSP + NPU architecture, with computing power covering 1T / 2T / 4T / 20T, tensorflow / Caffe and other architectures. It has flexible algorithm transplantation, better OP support, full range of 10nm low-power technology, top-notch image engine (ISP), the largest 4K@60FPS Coding, support 6-channel sensor access at most;