基於FPGA並行資料轉序列資料(verilog)

2020-09-25 11:00:33

Verilog程式碼:

module bit4_bit1(

input clk_50M_i,

input rst_n_i,

input [3:0]data_i,

input data_en_i,

output data_o,

output data_en_o

);

reg [3:0]data_i_tmp1;

reg [3:0]data_i_tmp2;

reg [3:0]data_i_valid;

reg data_en_tmp1;

reg data_en_tmp2;

reg [3:0]cnt;

reg data_o_tmp;

reg data_en_o_tmp;

//進來的資料和使能打兩拍同步一下

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)begin

data_i_tmp1 <= 4'b0;

data_i_tmp2 <= 4'b0;

data_en_tmp1 <= 1'b0;

data_en_tmp2 <= 1'b0;

end

else begin

data_i_tmp1 <= data_i;

data_i_tmp2 <= data_i_tmp1;

data_en_tmp1 <= data_en_i;

data_en_tmp2 <= data_en_tmp1;

end

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)

data_i_valid <= 4'b0;

else if(data_en_tmp2)

data_i_valid <= data_i_tmp2;

else

data_i_valid <= data_i_valid;

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)

cnt <= 4'b0;

else if(data_en_tmp2 || (cnt>0&&cnt<4))

cnt <= cnt + 1'b1;

else

cnt <= 4'b0;

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)

data_o_tmp <= 1'b0;

else if(cnt!=0)

data_o_tmp <= data_i_valid[4-cnt];

else

data_o_tmp <= 1'b0;

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)

data_en_o_tmp <= 1'b0;

else if(cnt!=0)

data_en_o_tmp <= 1'b1;

else

data_en_o_tmp <= 1'b0;

assign data_o = data_o_tmp;

assign data_en_o = data_en_o_tmp;

endmodule

測試檔案:

`timescale 1ns/1ns

module bit4_bit1_tb();

parameter clk_period = 20;

reg clk_50M_i;

reg rst_n_i;

reg [3:0]data_i;

reg data_en_i;

initial begin

clk_50M_i = 1'b0;

rst_n_i = 1'b0;

data_i = 4'b0000;

data_en_i = 1'b0;

#100

rst_n_i = 1'b1;

#200

data_i = 4'b0001;

data_en_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

data_i = 4'b0010;

data_en_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

data_i = 4'b0011;

data_en_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

data_i = 4'b0100;

data_en_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

data_i = 4'b0101;

data_en_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

data_i = 4'b0110;

data_en_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

data_i = 4'b0111;

data_en_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

data_i = 4'b1000;

data_en_i = 1'b1;

#clk_period data_en_i = 1'b0;

#500

data_i = 4'b0;

end

always #(clk_period/2) clk_50M_i = ~clk_50M_i;

bit4_bit1 bit4_bit1_inst(

.clk_50M_i(clk_50M_i),

.rst_n_i(rst_n_i),

.data_i(data_i),

.data_en_i(data_en_i),

.data_o(),

.data_en_o()

);

endmodule

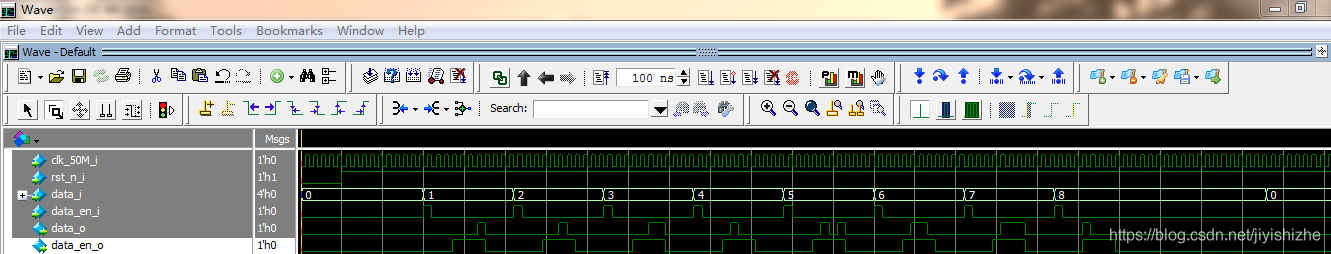

模擬截圖: